clock sample question

Hi ppl,

I have a question for you.

I have a very similar to the attached picture circuit. also you can find here (http://zone.ni.com/devzone/cda/tut/p/id/3615#toc4 , fig.2) I write some data on analog channels out and then I collect the data in the time loop. I don't understand what exactly is happening when I write the data in the buffer. Let's say I have a table of 2D 2-lines and 62500 columns that I want to write in the output analog channel, then read in the analog channel. I do not understand the meaning of the sample clock. (I read on operations 2 devices simultaneously and blah blah blah). What should be the sample clock frequency in the August channel and the channel of the ain and the number of samples per channel in the ain daqmx channel when I want to collect data? (http://zone.ni.com/devzone/cda/tut/p/id/2835; reading the data in example labview). My problem is that I do not understand what is happening when I load the August channel with data buffer; for example I put the sampling clock rate: 1000; meaning he will write each s 1000 samples of 62500 samples until the end of the samples; all of these samples that I drove from my out channel voltage piezo-beam-scanning engines. which means that each s piezo motors will get 1000 samples of tensions? now, I want to measure. should number of samples in the playback channel I put? I put my daqmx reading in the while loop. Let's say I put 100 Samper useful/channel. so, each itteration in while loop it will read the 1000 samples/channel buffer. How will I know that the buffer is already full with 1000 samples when ain channel tries to read?

The process is therefore more; correct me please if I'm wrong. The sample clock will define us the buffer data rate. For example, I load the 2D matrix: 62500 2rows columns; It will load in the buffer and then there are these samples at the August channel of the rate defined in the clock sample string? Then I want to read from the channel of the ain. What sampling clock frequency should I set for the channel of the ain? If the sample clock rate for the playback channel sets the buffer? for example (I put it there 1000 samples/s; meaning it can read 1000 samples per second?) then what the number of samples should be in the read daqmx channel in the while loop?

Please clarify me this point, I'm confused...

Hi dimani4,

There is a very comprehensive document that answers your questions. You can find this document here.

This article explains the operation of the sample clock frequency and the DAQmx Read reading samples. Quoting the article: "On the hardware side, the Schedule VI DAQmx determines the flow rate of the device/sensor data at the hardware buffer on the data acquisition card.". Here is the 'Timing VI' the sample clock. Then he also explained that "on the software side, the reading VI DAQmx determines the transfer of the data of the buffer material in the software". "." It is making reference to the samples to read the reading VI DAQmx.

I hope this information specific to your questions.

Tags: NI Hardware

Similar Questions

-

By dividing the time base clock sample by N, we're the first sample on pulse 1 or pulse N?

I use an external source for the time base a task of analog input sample clock. I'm dividing down by 100 to get my sample clock. Is could someone please tell me if my first sample clock pulse will be generated on the first impulse of the source of the base of external time, or about the 100th?

I use a M Series device, but can't see a time diagram in the manual that answers my question.

Thank you.

CASE NO.

CERTIFICATION AUTHORITIES,

I don't think it's possible to use the sample clock of 3 kHz on the fast map as the time base clock sample on the slow map and get the first sample to align. The fast card can enjoy on each pulse signal 3 kHz, while the slow card will have to meet the requirement of the initial delay before he can deliver a sample clock. If you turn this initial delay a minimum of two ticks of the time base, the slow card eventually picking around the edges of the clock 2, 102, 202, etc.. You can set the initial delay for 100, which means that the slow card would taste on the edges, 100, 200, 300... but you wouldn't get a card reading slow on the first edge of your sample clock.

Hope that helps,

Dan

-

[FlexRIO] Start-up to synchronize several clocks sample

Hello

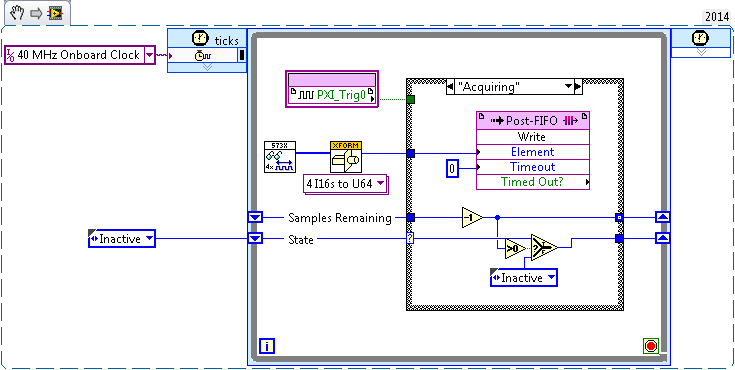

I tried before, two different (SMU-7962R + OR-5734) FlexRIO card reading in the '40 MHz Onboard Clock' or 'PXI_Clk10' areas of clock. Trigger has been achieved by simply looking for a rising edge on PXI_Trig0:

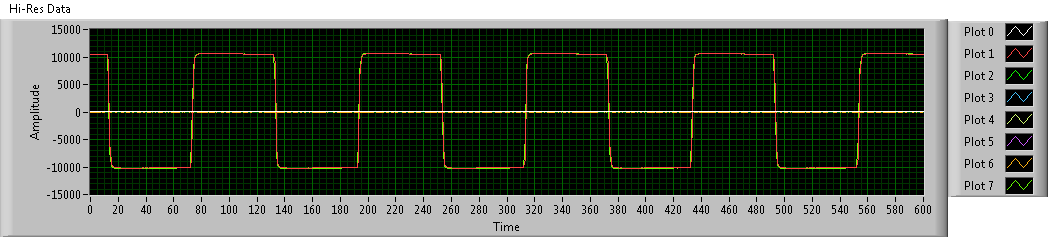

This produces seeds, but there has no inclination (or constantly tilt at least) between the two FlexRIOs - I sent a pulse train duplicated in the two cards, and the triggered-acquired waveforms were still at the stage:

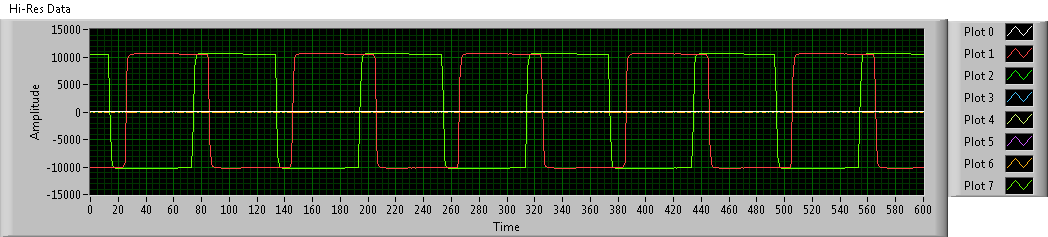

To avoid problems, I went to examples of clock (IO Module clock 0). Unfortunately, the clocks of the sample between the two FlexRIOs had nothing in common, so the acquired waveforms have been is out of phase. Worse still, the phase difference changes with each release:

Looking at the implementation of the library of the synchronization of the FIDL, the classic technique for synchronization of multiple cards FlexRIO seems to be built around synchronization master-slave (my observation is correct?). I was wondering: is there a way to simply share a sample clock shared between cards (like what the 40 MHz embedded clock was doing before), as described in http://www.ni.com/white-paper/11369/en/ ? (I think I understand the disadvantages associated with sample clock synchronization, but I'm willing to try for now).

Thanks in advance!

Hi JKSH,

Page 9 of the Manual 5734 described the different synchronized methods that can be used the 5734. You can synchronize either sample clock of each module to a clock available through your chassis backplane (for example, DStar_A) by allowing the IOModSynClk in 5734 properties (available the Details category) or use an external clock through the Clk port on the module. Activation of IOModSyncClk is probably the best approach and will lead by examples of clock on each module e/s being PLLed on the clock of the town - which must synchronize the clocks of the two sample together.

Let me know if you have follow-up questions.

Kind regards

-

Problem of clock sample e/s digital PCI-6229

Hello

I use PCI-6229. I need to use the digital output channel to generate pulses of 20 kHz 30% duty cycle.

The datasheet shows the sample clock frequency can be 1 M Hz. But in may, only 100KHzTimebase may work to generate. But acctually I need at least 200K Hz.

I've done the Vi is attached. Can someone help me with this problem?

Thank you

Hello ossoo,

The PCI-6229 is not a timing engine digital to create a digital task which runs at 1 MHz, you must use an external sample clock. However, one thing you can do is generate a pulse train at your desired frequency using a meter integrated 6229 and then using this output meter as the sample for your task digital clock. Take a look at the attached amendment, I made to your VI which shows how to build your digital task to 1 MHz using the meter on board. You can change the frequency of the train of impulses of the meter in order to change the frequency of your outputs digital. Please let me know if you have any questions.

Kind regards

-

Device supports input clock samples?

I posted this question in another forum, but I think this is the best location.

CV,

As far as I know, there isn't a way to get a T/F value for a sample of a device clock. When you choose a channel for the moment, you could search for "have / sampleclock.» However, I recommend that you check your manual to determine whether a sample clock is available for a specific device.

-

9401 buffered output digital clock sample source

Hi, I would like to generate a pulse train with a defined number of pulses, according to a defined periodicity. I use a NI9401 module in the Groove 3 CompactDAQ chassis so that I can write the required buffer sample 2047 pulse train. The problem I have is I am unable to choose any clock source slower than the time base of 100 kHz, which means that the buffer can underflow very easily. I would use a 4 kHz clock source, but cannot find how do. If I want to generate a source of the clock of one of the counters, I must have the 9401 in slots 6 or 7 which then do not allow for generation of digital signals in the buffer...

Hi, JPP,.

Access to internal counters, even if modules are connected in the Groove 1-4 of the cDAQ chassis. Note this site 6 & 7 are necessary only if you need external access to counters as task of counter in the buffer, the measures of frequency/period, etc... Since in your application, all you need is to generate a continuous pulse train and access its output internally to clock output your digital correlated, this shouldn't be a problem with your DIO module into the Groove 4. Please take a look at the following link for more information.

With the help of internal counters on one NOR cDAQ-9172 as a sample for other tasks clock

http://digital.NI.com/public.nsf/allkb/EEB574335BA0B4EB862572060055E9DD?OpenDocument

I would also like to refer to an example on our site which shows you how to use your correlated digital i/o clock counter. I hope this helps.

NOR-DAQmx: Digital Correlation of e/s with NI CompactDAQ and LabVIEW

-

HI - anyone has the issue of sample or exams MOC question links to VCAP5. Please suggest,

Thanks for the link to my blog Scott

As Scott says there is no question simulated for the DCA because it is a review of laboratory and therefore there is no questions, but you can get an idea of the format of the exam from here based: http://mylearn.vmware.com/courseware/82526/VCAPDCA_Tutorial.swf

With regard to the type of fake Sean Crookston idea made some to the VCAP4-DCA that are a good idea of the format of some of the issues you can see: http://www.seancrookston.com/?s=mock+lab

Good luck. I recommend at least 50-60 hours of laboratory practice everything on renewal and Josh Coen and Jason Langers notes (if you are looking to make the VCAP5-DCA is)

Gregg

-

IOS based App clock alarm question

The beginning of alarm when you use iPhone at the same time, the alarm 'repeated' down turn when you press OK. This cause of evil that I only expect it to be off before today and continue the next day. (This is not the case when press OK on the lock screen)

It is originally wrong, can anyone help?

I know right I understand your question. If I understand correctly, you have trouble to set an alarm, repetitive - right? Where is it you press OK? Have you checked to see if you have enabled snooze. How do you turn off the alarm when it fires?

-

Salvation. I have a movie clip in my php page. I have a button in this clip. what code should I use to change every page to another, because when I use

(release)

{

getURL ("http://www.sample.com/");

}It opens the page at the location of the swf file, but I don't want that.

I tried

(release)

{

getURL ("http://www.sample.com/", "_blank");

}but it will open in a new tab.

I want to open a new page in the same tab. Is it possible to do?

Thank you

I don't know exactly what you are trying to do but see if one of the following works for you:

getURL ("http://www.sample.com/", "_top");

getURL ("http://www.sample.com/", "_parent");

-

Reference clock synchronization and clock of sampling (not LabView but Daqmx, Sync and C)

Well, I found an example that resemble what I wanted... in LabView: http://zone.ni.com/devzone/cda/tut/p/id/9308

Now the question is all about timing of the timestamps and sample:

Here is a list of ficelleStringString ficelleT of what I called...

DAQmxCreateTask

DAQmxCreateAIVoltageChan

DAQmxSetRefClkSrc (used NISYNC_VAL_CLK10 = "PXI_CLK10")

DAQmxRegisterEveryNSamplesEvent

niSync_init (used a PXI-6682)

niSync_SetAttributeViInt32 (used Terminal = NISYNC_VAL_PXISTAR0 and NISYNC_ATTR_1588_TIMESTAMP_BUF_SIZE = 3000)

niSync_CreateClock (used Terminal = NISYNC_VAL_PXISTAR0)

niSync_EnableTimeStampTrigger (used Terminal = NISYNC_VAL_PXISTAR0)

Now this list makes me able to create a timestamp every time the clock triggers a RISING edge...

Now how to synchronize these timestamps are useful for my sample? (I mean I need to sync my calendar with the PXI_CLK10 card) because for now prices will not match the sample rate.

ALSO... a little weird...

some of my cards will accept DAQmxSetRefClkSrc but others must use DAQmxSetMasterTimebaseSrc.

Now I can't use DAQmxSetMasterTimebaseSrc with PXI_CLK10... no idea why...

So, how did I would synchronize THESE cards...

Alright I could totally be wrogn with my approach, but I'm new with stuff of OR and using C isn't exactly the best documented piece of the NC.

Thanks in advance,

SEB

Thus,.

We have the same clock sampling for all of these devices, but we are not PLL'ing with the card of the S series, we cannot guarantee that they will all be in phase. However, given that all of these devices would be based on the same reference clock, we would not drift when we started the task. Would this work?

An alternative is to use the new X-Series card, which can also do a simultaneous sampling, but I don't know if it is feesible within your application.

-

Problem with DAQmx Schedule VI (sample clock)

Hello to you all,.

I'm new to this forum, please bare with me. I have some experience with LV, but I am relatively new to data acquisition projects. I use LV2009.

I want to make sure that I use the hardware timing (instead of software distribution) in my project so I followed some of the threads here as sugested to use DAQmx Schedule VI. The problem is that no matter how I set the system I get the same error-200300 invalid calendar

type.The project is simple. I encode with 1000 pulses per

Rev and it is mounted on a shaft of a turbine water goes thru. I'm watching the frequency

and so the rotation of the shaft which tells me that the amount of water flows through the turbine. In the end, there will be 2 channels

by every encoder and ~ 3 encoders (turbines) total and calibrated the main meter that will give me constant impulses and all encoders will be compared to this master frequency.I'll use PCI6602 DAQ, but

now, for the development, I use USB6221. Let's say that the

frequency is between 500 Hz and 10 kHz. What I am doing wrong? Or maybe better to ask - what would be the right approach for this project?Thank you

Marty

Hi Marty,

It seems that your question is already answered here, but Jason is correct that the 6221 neither the 6602 support a clock sampling for frequency measurements.

As Jason mentioned, your best bet is also likely set the mode of synchronization for "implied". This means that the frequency value is sampled at the end of each period of your input signal. In addition, a solution that is clocked by the software (On-Demand) might be acceptable.

X Series DAQ devices allow an external sample clock to use for frequency measures (described in the Manual of X series). Frequency of sample-clocked measures are useful in very specific

circumstances, but it does not seem that you need this feature based on what you've described so far.(621 x) bus-powered M series can also be configured to use an external sample as the X series clock but do you not have the same features described in the manual of the X series.

I hope this helps!

-John

-

Digital filter on the sample clock 6601/6250

Hello

I use a PCI-6601 (Dev1) and the card PCI-6250 (Dev2) connected via a cable RTSI.

I apply a PWM signal to the 6601 ctr0 (Dev1 / / PFI38) and activate the digital filtering (100 ns) on the respective task (measure of the period).

I apply an analogue signal to AI0 map of 6250. As I am interested in a sample of analog measurement when the PWM signal changes from low to high, I put the clock sample of the AI task source ' Dev1 / / PFI38 "and the side assets of clock sample"Insurrection. "

Everything works fine, but I have a question:

The sample for the AI clock is the task the filtered PWM signal or not filtered PWM signal?

Kind regards

Udo

Hi Udo,

Great question! Digital filters are actually not part of the subsystem of counter, but rather the line itself PFI. So, if you have activated the digital filter for a specific line of the PFI, the signal that you route to any subsystem of the PFI line will have already crossed the filter.

It's actually the workaround to the PFI filters on M-series / TIO DAQ devices when you are not using meter (materials of filtering on each PFI line but the DAQmx driver allows only the filtering part of duties of counter on these devices).

I also wanted to emphasize that the 6250 itself has 2 onboard counters, then you could do the same thing using just the 6250 (unless you use more than 2 meters). I hope this helps!

Best regards

John

-

Specified sample rate clock works do not

I hope that I was right to post on this forum. I have a problem that I had not previously in the acquisition of data on a chassis 9172 cDAQ using a 9234 for 2 analog inputs and a 9219 for four thermocouple inputs. The 9219 is obviously not ideal as it has a rate relatively low sample (and I have a 9213 on the way), so I'll have to use to HAVE. ADCTimingMode to isolate channels on this module for "high speed" mode if I can get an adequate sampling for my load. The question that arises is that no matter what I do to specify a sample rate, the actual sampling rate ends up being 1651,61 Hz, higher than the features of the 9219, if I get an error. I tried to use the DAQmx property node to set the calendar and the clock sampling VI but neither work. The only source that I can choose is on board, but when I check the source used is cDAQ1Mod1/AI/SampleClock, even if I get an error when I try to provide as a source of sample VI clock.

As it is, my VI runs despite this error and seems to produce accurate data, but the original problem is with long testing I will have unnecessarily large data sets unless I start to decimate my other data, and the secondary problem, it's that I can't get the program to run when I try to incorporate my task of counter. In this case, the error ends the execution and he acquires no data.

I have attached my VI under the task of counter (I'm on 8.5 and have the coming upgrade as well), but also an image of a simplified version of the VI only try to specify the settings of a channel of AI. I get the same result with it. I'm a bit of a loss here because I've never had this problem before, and it seems that there is something beyond rudimentary that I'm missing, so I would really appreciate any help anyone could provide. Thanks in advance.

-

How do you use the freqout as the sample clock to write data on the of 6224 PCI

Using PCI-6224, I try currently to export data using the freqout as a reference clock sample to a digital output channel. I plug the scope to see the clock on the freqout PIN. However, the data seem to be missing. How can I output the data correctly using the reference for timing? What am I missing that connects the two signals together? Any help would be greatly appreciated. I am writing this code in MS VS C++ and here's what I've done so far:

int32 error=0; TaskHandle taskHandle=0; TaskHandle taskHandleFRQ=0; char errBuff[2048]={'\0'}; uInt8 data[8]={1,0,1,1,1,0,1,0}; /*********************************************/ // DAQmx Configure Clock /*********************************************/ DAQmxErrChk (DAQmxCreateTask("",&taskHandleFRQ)); DAQmxErrChk (DAQmxCreateCOPulseChanFreq(taskHandleFRQ,"Dev2/freqout","",DAQmx_Val_Hz/*Units*/,DAQmx_Val_Low/*IdleState*/,0/*Delay*/,10000/*Freq*/,0.5/*DutyCycle*/)); DAQmxErrChk (DAQmxCfgImplicitTiming(taskHandleFRQ,DAQmx_Val_ContSamps,8)); /*********************************************/ // DAQmx Configure Digital Output /*********************************************/ DAQmxErrChk (DAQmxCreateTask("",&taskHandle)); DAQmxErrChk (DAQmxCreateDOChan(taskHandle,"Dev2/port0/line0","",DAQmx_Val_ChanPerLine)); DAQmxErrChk (DAQmxCfgSampClkTiming(taskHandle,"/Dev2/PFI14",10000,DAQmx_Val_Rising,DAQmx_Val_FiniteSamps,8)); /*********************************************/ // DAQmx Write Code /*********************************************/ DAQmxErrChk (DAQmxWriteDigitalLines(taskHandle,8,0,10.0,DAQmx_Val_GroupByChannel,data,NULL,NULL)); /*********************************************/ // DAQmx Start Code /*********************************************/ DAQmxErrChk (DAQmxStartTask(taskHandleFRQ)); DAQmxErrChk (DAQmxStartTask(taskHandle));I think that the original code was operational. However, given that the data transmission has been set to finished, I had a hard time to visualize the data on my scope. By changing the value of DAQmx_Val_FiniteSamps to DAQmx_Val_ContSamps, I could easily see the data.

My mistake. I'm still learning here. Thanks for the time.

-

Sampling rate higher for the measurement of precision meter

I have a BNC 6259 M Series DAQ USB. I am currently using the DAQ Assistant to perform simple cash rising measured with the measuring mode single sample on request. I tested my VI with a known square wave with a function generator signal and it clearly lacks a few edges. I think that the solution lies in faster sampling. However, I was not able to understand how to use clocks to set up continuous sampling mode. I tried the forums and I found articles that were close, but not quite exactly the problem I am facing with as (http://forums.ni.com/t5/Digital-I-O/trying-to-use-NI-6251-s-DIO-port-as-input-and-output/m-p/448035#...) or (http://forums.ni.com/t5/Multifunction-DAQ/Using-Counter-of-PCI-6024E-with-Quadrature-Encoder/m-p/984...). Any guidance here would be great.

In fact, the calendar should not have anything to do with the edges being detected. Configuration of a sample clock for a county of just edge task allows you to enjoy deterministically in the account register and has no impact on the edges which can be counted. Also, the analog examples really have nothing to do with what you seem to be asking questions on.

... So it leaves the question unanswered as to why you might miss the edges. Perhaps the following information could shed some light on the question:

1. it is possible that you do not configure the counter exactly as you think you are. Can you post the VI you use? As a point of reference, count digital events shipping example does not use any clock sample timing and just questioned the value of the register count with a software loop, but the meter should not miss all this edge on the input source. There are examples that are timed by the material available as well, but this is not necessary, unless you need a constant specified dt between your counter samples. To use the examples of the timed sample, you will need to generate a clock of either another subsystem on the map or use an external clock.

2. assuming that the configuration of the counter is not the issue, there may be a problem with the method that you use to determine if you are away from the edges. How do you know that you are away from the edges? The function generator produces only a finite pulse amount? You start the meter before start out impulses?

3. If the two points above do not raise red flags, it seems likely that the meter is registered just not some of the impulses of your FGEN. Can I assume that the output of the FGEN is 0 - 5V TTL? What is its frequency and duty cycle? The maximum external source for the meter on the M-series products: DAQ (like the 6259) is specced at 20 MHz, but this depends on a clean signal with good connections. At frequencies above it, the bandwidth of the front-end of the PFI lines becomes limiting. If you have an available specification document for your FGEN I'd like to be able to see it.

I hope this gets you throw on the right track to solve the problem - impatience comes back with more information.

Best regards

Maybe you are looking for

-

That means rendering and how long it takes it?

Never seen the orange line that indicates my project must be made. I noticed how slow my actions when I looked into this orange make the line. I down loaded plug ins of Pixel film and used quite a bit in my project, (I don't know if they are 2D or

-

Why Apple is so late, just got an iPhone 5SE and I can't pair it with my macbook pro via Bluetooth, I can't believe its that poor. You wait at least Apple products to pair each plus, if not to some third-party products. Anyone have an idea how I can

-

Cannot update the Gmail password in Mail, community advice does not

Mail worked fine for years. Then changed the password and can not get it working again. I understand how to update the Gmail, password is as follows: Under mail > preferences > account > "Your Gmail account" > account information, click outgoing (SM

-

I'm unable to show all of the icons on my desktop.

I'm unable to show all of the icons on my desktop. The taskbar appears, and I can access my applications from the start menu, but no icon on the desktop application. I use Windows XP, SP3.

-

How to move files between folders without having to turn off UAC (as admin)

I am connected to my computer as an administrator (Windows Vista). I take loads and loads of photos - when I edit that I need to move them between folders or subfolders. If I have active user account control, the system tells me that I don't have p