compilation of FPGA

Hello!

How can I compile a code to the FPGA without hardware. I just want to see something on my FPGA BRAMs. If I compile code to FPGA with actual hardware, it takes too much time.

Best regards

HITMANNN wrote:If I compile code to FPGA with actual hardware, it takes too much time.

As long as you have defined your specific material in the LabVIEW project, you can compile your FPGA screw with or without connection, but in all cases, it will take the same time to compile. Compilation of FPGA can be a lengthy process.

Tags: NI Software

Similar Questions

-

Choose ISE or Vivado Xilinx tools for a specific compilation of FPGA

Hello

Is there a way to specify what version of Xilinx Compilation tools to use when compiling an FPGA VI? I want to try the version Vivado tools rather than the version of ISE to see if there is an improvement. I have listed some information on my setup below.

It's my current setup:

NI5772 / PXIe7966 digitizer and FPGA

SMU-1082 chassis

SMU-PCIe8388 / SMU-PCIe8389 controller

LabVIEW 2014In the past, I used the LabVIEW 2014 FPGA Xilinx tools 14.7 Module to compile my code. But I also want to try the version of Vivado, "LabVIEW FPGA Module Xilinx tools Vivado 2013.4 2014', to see if it gives better results."

Page-based "compatibility between tools Compilation of Xilinx and FPGA hardware OR" here:

http://www.NI.com/product-documentation/53056/en/

Looks like the PXIe7966 FPGA must be compatible with the tools of Vivado 2013.4.I tried to uninstall the version 14.7 ISE tools, and install the 2013.4 of tools Vivado (so Vivado 2013.4 tools are the only xilinx tools installed on the computer). But LabVIEW complains that the ISE 14.7 tools are not installed and does not compile the FPGA VI.

Thank you!

MichaelThis FPGA is a Virtex-5 FPGA, so you're stuck with ISE. You need a card FPGA that either uses the architecting chip (I think it was only in cRIOs) or 7 Kintex to use the compiler to Vivado.

-

Compilation of FPGA hangs in LV2014SP1

Hi all

I've recently updated to LV2014SP1 of LV2014. Since then, I can't compile my FPGA VI locally for a project (cRIO9067), which was done in LV2014. Whenever I try, the compiler will in the step of "logic optimization. Then, after severyl minutes, vivado.exe drops to 0% CPU usage and are still just there indefinitely. After a long period without increasing time CPU for vivado.exe, the worker of compilation obviously restarts the compilation and the same thing happens again. Yesterday I let sit for 4 hours, and when I think about it, vivado.exe had consumed some time CPU 36 minutes and that he was still sitting there with 0% CPU usage.

When you use a server compilation (still under LV2014), the VI compiles fine from the same project on the same PC! In addition, compilation of other screws FPGA for the same thing and other targets (cRIO9030) works locally.

The same problem occurred on a second PC that has also been upgraded to 2014SP1. Even up until 2014 with the toolkit and FPGA Xilinx 13.04 time has not helped - I can not always compile.

Any ideas or similar problems anyone?

Hey, Jörg,.

Can you download and install CompactRIO Module Support 14.6?

We have published a patch for 926 x modules that did not compile with the SP1 build tools exist.

-

Internal error OR-farm - impossible to compile the FPGA VI

Hello!

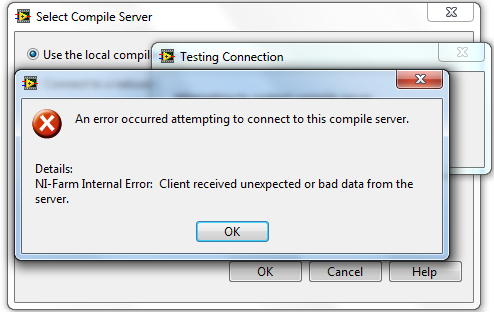

When I try to compile any FPGA VI with LabVIEW2013 or 2012 SP1, I get the following error:

"Year error occurred trying to connect to this server compilation."

Details:

Internal error OR the farm: Client Server received unexpected or bad data. »

Intermediate files are not generated, the error message appears immediately after I have select build of build specification or I click the run arrow.

I use the local server for compilation.

The equipment I use: CompactRIO Evaluation Board - SbRIO9636, DELL laptop, Intel core2 Duo T5800, 2 GHz, 3 GB RAM, Windows 7 Ultimate 64-bit, SP1.

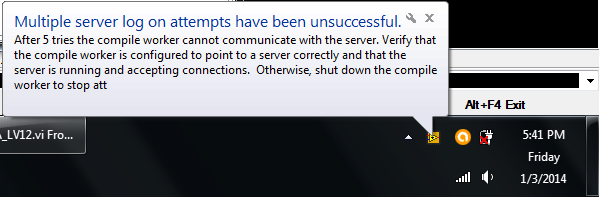

The intermediate files CAN be generated without any problems if I select in the menu. If I run the FPGA application compile worker, a ToolTip message specifying that "FPGA compile runs", but after a few seconds, another message appears: newspaper several attempts were unsuccessful - please see attached images.

At first, I thought that my firewall (Comodo 6.3) is the reason for this, so I disabled it but nothing changed. Then I tried to fix LabVIEW FPGA and XILINX tools with the firewall disabled but din do not solve the problem. I tried with LabVIEW SP1 of 2012 and 2013.

If you have any suggestions, please let me know! Thank you!

We would like that you try to reset the NIAuth database by following these steps:

1. go to Windows Services (Bring up Windows with Ctrl + Alt + Delete Task Manager, click the Services tab, click the Services button at the bottom right of the window.

2 stop the NI Application Web Server and NI System Web Server services in this order (right click, stopping service and select).

2 backup, and then delete all the files under %PROGRAMDATA%\National Instruments\NIAuth: registry.bin and commitmark.

3. run NI System Web Server and NI Application Web Server services in this order.

4. navigate to http://localhost:3580 / connection of an IE on the local computer and try to log in with username "admin" and password empty. Succeeds, the server will return one signed in as: message from the admin.

After you follow these steps, try and connect to the FPGA compiler, and then let me know what are the results.

-

Impossible to compile the FPGA in project

Hello

I get the following error when I am trying to compile an FPGA VI on a Compact Rio 9022, I missing something on my stand in?

Everyone has seen this before and know what is happening?

An internal software error occurred. Please contact National Instruments technical support on ni.com/support with the following information:

7 error error component the generator module VI: NULL

Possible reasons:

LabVIEW: File not found. The file may have been moved or deleted, or the path to the file would be incorrectly formatted for the operating system. For example, use- as Windows path separators: on Mac OS, and Linux. Check that the path is correct using the command prompt or file Explorer.

=========================

NOR-488: The non-existent GPIB interface.This looks really familiar. I know I've seen this error. I think there is a problem if you upgrade to the latest NOR-RIO, but you don't put at level LV FPGA 8.6.0 to 8.6.1, or something like that. Would it be, kmoyna?

-

Compilation of FPGA - real formal error on the cost of the port cannot be an expression

Details:

ERROR: HDLCompiler:192 - "C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd" line 1408: real formal on the cost of the port cannot be an expression

ERROR: HDLCompiler:854 - "C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd" line 69:Unit ignored due to previous errors.

File VHDL C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd ignored errors

-->The compilation happens to step "using the unit felt" but then stops soon after with a compilation error.

The line in question (1408) refers to the output of a "Reinterpretation FXP" node with the text

Cost => (others-online '0'),

in the part of port of the code card. This is the output of the FXP reinterpret node is directly connected to an indicator in a VI sub whose output is then entered directly at a crossing high multiply node. The code is part of a cosine sine LUT I programmed. She used to compile without a problem, but I think I know where is the problem. In one case, I have used only the sine of output of the algorithm and theory, Xilinx can optimize away from the part of cosine. I have two instances of this VI in my code and looking at those generating any errors, the output is associated with a cosine indicator.

Cost-online s_Cosine_2434,

It seems that the track is essentially optimized away, but the compiler, Xilinx has a problem with the flag being present on the sub - VI but the idnicator is not used anywhere. As a result, the cost gets set to an invalid value. I guess close to reinterpret it FXP at the exit of the Subvi is an important aspect of this problem.

I think I know enough now to fix this (remove the path manually by duplicating the sub - vi), but it may be useful for future bug fixes feedback in the FPGA module. It is not the first time that this kind of removal of incorrect code me has given problems, but this is the first time I could clearly identify the problem.

Shane

Hey Shane,

Looks like someone filed a bug report on it a month or two ago. It's the CAR # 475397 if you want to check for it in the list bug fixed for 2014 SP1.

-

LabVIEW crashing whenever I try to execute / compile an FPGA VI

I have a project of RT using a cRIO-9012 / 9112 and every time that I hit on the FPGA VI, the compilation process starts but immediately blocked LabVIEW. The FPGA code is simple - just a development which is basically copied from the VI example OR for the module OR 9214 starting point. I have LabVIEW Real-time, LabVIEW FPGA, OR-RIO installed (LabVIEW 2013 32 bit running on 64-bit Windows 7 computer), Xilinx tools 14.4 installed. The crash error report dialog box is shown below:

I don't know what it takes then try to diagnose and correct the problem. Thoughts?

If it turns out that I had explicitly wired constant I/O device to the i/o method node FPGA and FPGA to IO property under my VI, who, for some reason, was originally the compiler crashes labview. Remove these constants and in defining the elements of e/s instead in the context menus in right-click for both types of nodes seem to have eliminated the fracas.

-

Compilation of FPGA 61330 error on a cRIO

Hi all

Currently, I have to rebuild a fpga bitfile to reflect a new hardware configuration on a cRIO. I have installed on my computer, tools that have been able to compile the bitfile several times; but now I get an error when I compile. I have attached two images of the error to this message. I'm currently under this software configuration:

It turns out it was a firewall issue. I had turned off my firewall, but there was a tertiary process still running. I added a few my firewall exceptions, which should allow the program to work, but it didn't. Once I deleted these exceptions, the compiler run with no errors. I think it's time to get a new firewall program. Thanks for all your help.

-

Error compiling 2010 FPGA - TclTasklC:project_028: unknown property value

Hi, I use a cRIO 9075 and a NI 9211 to measure the temperature to a project very busy with. Whenever I have try the code for compilation of t I have a compilation error which read as follows:

Compilation failed due to an error of Xilinx.

Details:

ERROR: TclTasksC: project_028:Unknown 'spartan6' property value specified for "PROP_DevFamily."

Can someone help me on how to solve this error, I'm using LabVIEW 2010 FPGA and Xilinx 11.5

Concerning

You are welcome! I am happy to know that everything works correctly!

Happy Friday!

Jordan

-

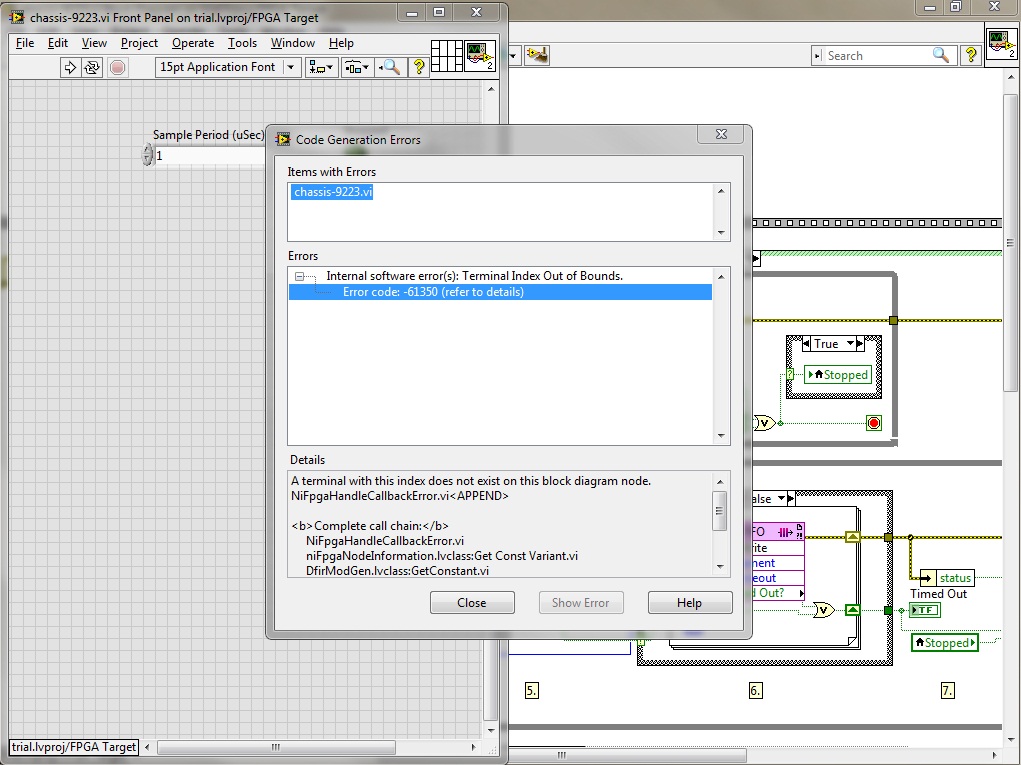

I get the error (in a popup window) when my VI FPGA code in chassis 9118 OR NI 9223 module compiled help. This error occurs when compiling the process (generating intermediate files, scene 7 of 7). How to solve this error?

Thank you

additional information:

Original error message:

-------------------------Errors:

Software (s) internal error: Terminal Index out of Bounds.

:-61350 error code

Details:

A terminal with this index does not exist on this block diagram node.

NiFpgaHandleCallbackError.vi«"" "String of full appeal:»»"»

NiFpgaHandleCallbackError.vi

niFpgaNodeInformation.lvclass:Get Const Variant.vi

DfirModGen.lvclass:GetConstant.vi

niLvFpgaMungerBrainwashIONodeCommon_Dfir.vi

niLvFpgaMungerBrainwashSingleIOGrowableMethod_DFIR.vi

nirviEIOMethodImplementation_SpecifyDFIR.vi

nirviEIOMethodImplementation_SpecifyDFIR.vi.ProxyCallerHi tesa,.

This is a bug that has been fixed in LabVIEW 2012 SP1. The number of CAR created for this bug is 332811 and as you can see in this link, it is already in the list of bug fixes.

Carmen C.

-

Problem compiling LV FPGA (urgent)

Hello

I'm trying to make a code FPGA LV in my crio 9074, but it takes a lot of time unsusually (40 minutes or more).

I'm trying to implement this example to generate a waveform: http://www.ni.com/example/28209/en/

Up to now, it's show "generation of carrots" message and in the newspaper, I'm repeatedly getting this message:

aved CGP file for project 'coregen.

Fix generics to 'ReallyLongUniqueName_ReallyLongUniqueName '...

Generic external application to 'ReallyLongUniqueName_ReallyLongUniqueName '...

Delivery of files related to "ReallyLongUniqueName_ReallyLongUniqueName"...

Setting netlist generation implemented to

'ReallyLongUniqueName_ReallyLongUniqueName '...

Synthesis running for "ReallyLongUniqueName_ReallyLongUniqueName."

13.4 - Xilinx CORE Generator O.87xd (nt) of output

Copyright (c) 1995-2011 Xilinx, Inc. All rights reserved.

Save all the run-time messages

C:\NIFPGA\jobs\W543T9Q_a5T1mXb\coregen.log

In the CGP project «coregen» file

Fix generics to 'ReallyLongUniqueName_ReallyLongUniqueName '...

Generic external application to 'ReallyLongUniqueName_ReallyLongUniqueName '...

Delivery of files related to "ReallyLongUniqueName_ReallyLongUniqueName"...

Setting netlist generation implemented to

'ReallyLongUniqueName_ReallyLongUniqueName '...

Synthesis running for "ReallyLongUniqueName_ReallyLongUniqueName."It seems that it is in some kind of loop without end Peae guide me how to solve the problem.

Thank you...

These are 'normal' of the process of compilation output messages (although they are a little curious). It is normal to have a certain number of these modules in the FPGA design, if you use analysis library functions; each of them can take several minutes to synthesize. The compilation has finished?

Fortunately, if you're doing only minor subsequent changes compile compile times are expected to decline because the compiled results of each of these components is cached.

-

Remote compilation of FPGA on a Linux machine

Hello

I try to use the worker of compilation on an architecture based on Linux (RHEL) with a development of Windows 7 PC (Labview 2014). This works if the two machines are on a private network, but not on a managed network of field with several strict firewall rules.

What are for use on Windows Firewall settings to allow the connection between the worker of compilation and compilation Server?

(Incidentally: the compile Server seem not to exist for Linux.) "Is it true?)

Thanks for your help.

You are right.! There is no compilation of Linux server... So I also use a Windows Server

For more information, I was able to connect the PC by opening TCP port /3580 (instead of 3582).

See you soon.

-

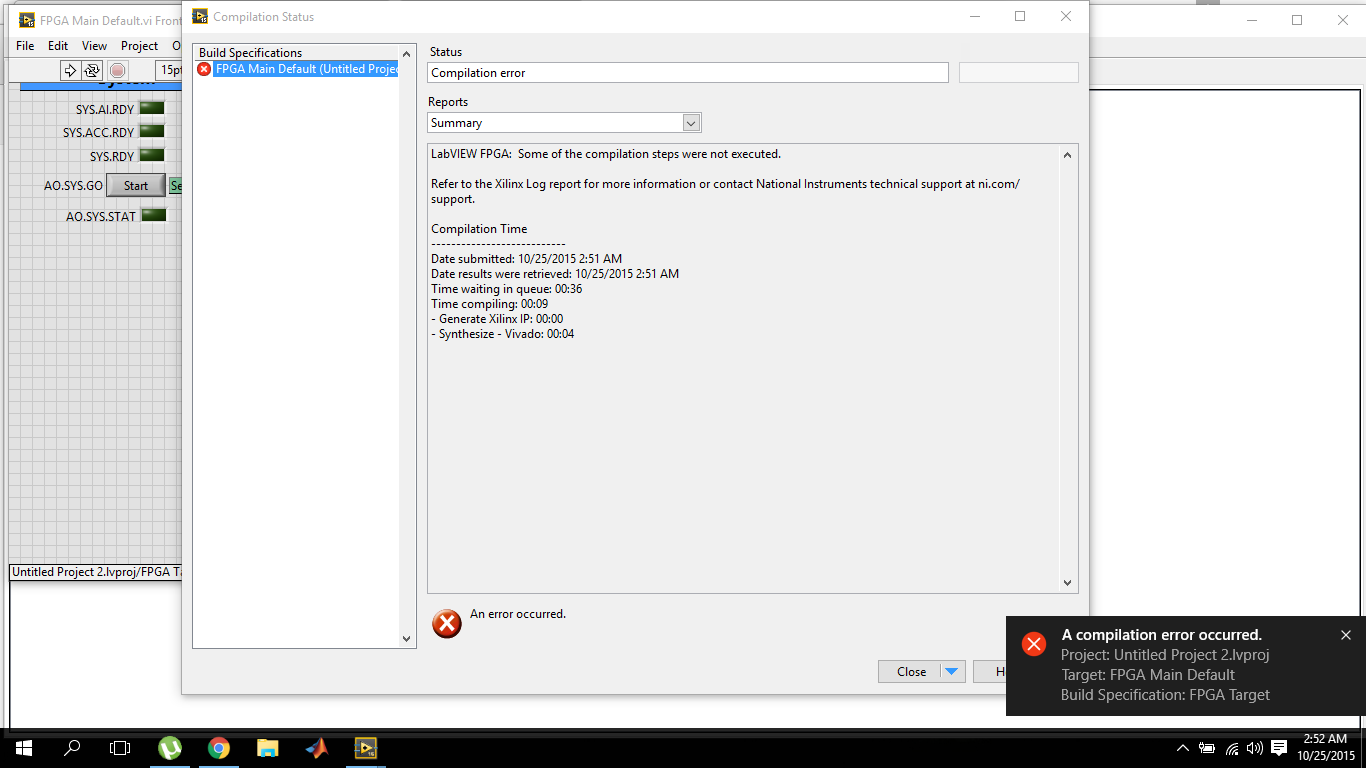

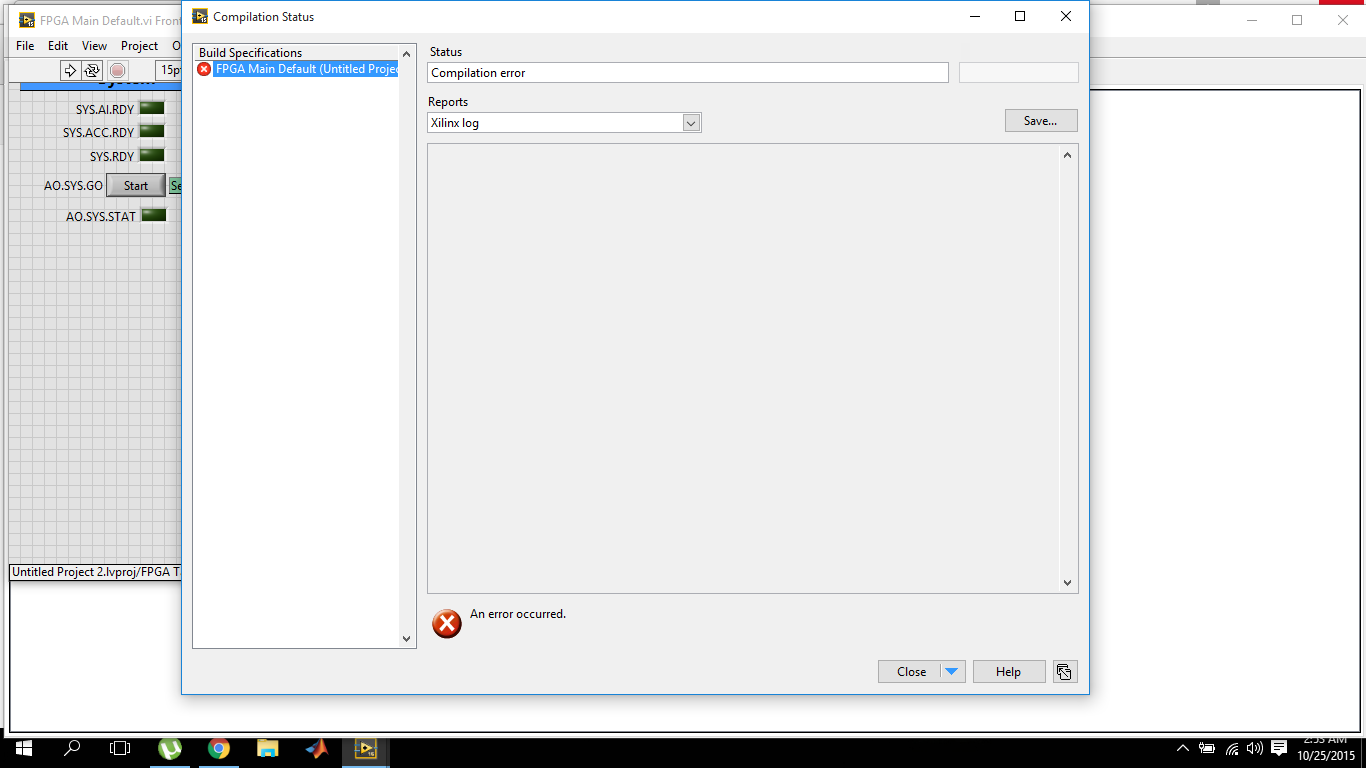

LabVIEW FPGA, 2015 compilation error

I've recently switched to LabVIEW 2015 and I'm working on OR myRIO. So also installed myRIO 2015 bundled software. The problem I have is that the compilation of fpga fails within 10 seconds.

and the target Xilinx journal report is empty

The first time when I tried to compile on 2015 version, it failed and the message box that failed came alongwith the avast antivirus warning for malicious activity. I reported it as wrong and now I tried several times with avast shield disabled control, but the results are the same. While the version of labVIEW 2014 works very well.

Now, I'm sure that there is something wrong with the installation of Vivado because this dll is part of it. The dll must be default in the2014_4\lib\win32.o directory C:\NIFPGA\programs\Vivado if you are using an operating system for 32-bit AND also in C:\NIFPGA\programs\Vivado2014_4\lib\win64.o If you use a 64-bit operating system. If the dll is not here, it is probably that the anti virus (I've never seen what happens to Xilinx but I have for other stuff).

I'm emphasizing the 2014_4 because LabVIEW 2015 uses Vivado 2014_4 while 2014 LabVIEW uses Vivado 2013_4. Since you have also installed LabVIEW 2014, you must have 2013_4 as well and if it works, you will find the dll I just wanted you make sure you check the correct directory for the Vivado 2014_4.

Download and install (reinstall or repair if already installed) 2015 LabVIEW FPGA Module Xilinx tools Vivado 2014.4. You can also use the DVD Setup if you have. It would be a good idea to do the installation with the disabled and even anti-virus try the first compilation the same. Try and let me know if the problem persists.

Kind regards

-

FPGA connect for compiling the server

Hi all

I'm just trying to write my code for my Spartan 3 FPGA. I was moved to another computer so I tried to install the right tools... LabView 2010, the module, LabView FPGA 2010 so that the pilot of the Commission of the Spartan Xlinix I use. Windows XP (32 bit)

Everything seems functional until the moment when I try to compile the code on my device. Apparently it "impossible to connect to the build server" or "compilation tools are not installed on this computer." I thought that all that is necessary to compile is included in the download of the module.

Is there some piece of obivous I'm missing? Thanks in advance.

Hi Oli,

I had the same problem recently. It is very important that all the good software and drivers are installed in the order so that everything works as expected. Looks like you have installed the driver appropriate for the Xilinx Board, you may not have Compilation of Xilinx tools for your FPGA. For the Spartan 3 FPGA, I recommend that you download Xilinx tools 12.4. This will allow your computer to compile the FPGA bitfiles for your specific FPGA module.

Kind regards

-

ERROR: TclTasksC:process_077: in the FPGA Compilation

Hi all

I use for my application in which I am facing following error when compiling my fpga code compact rio 9072:

Compilation failed due to an error of Xilinx.

Details:

ERROR: TclTasksC rocess_077: did not finish. Please, look in the newspaper and report files.false

rocess_077: did not finish. Please, look in the newspaper and report files.false

When running

"process run"card.

(file "C:\NIFPGA\jobs\XI64xG6_My449tj\map.tcl" line 6)ERROR

ack:2310 - type compositions "SLICEL" too found to adapt to this device.

ack:2310 - type compositions "SLICEL" too found to adapt to this device.

ERROR ack:18 - the design is too large for the device and package.

ack:18 - the design is too large for the device and package.

Please see the Design summary section to see the cost estimates for

your design exceeds the resources available in the device.

NOTE: A file NCD will be always generated to allow you to examine the mapped

Design. This file is intended for assessment use only and will not be processed

successfully through NOMINAL.

This NCD mapped file can be used to assess how the logic of the design has been

mapped in FPGA logic resources. It can also be used to analyze

preliminary to the level logic (route pre) calendar with one of the static electricity of Xilinx

analysis of synchronization (PRHT or Timing Analyzer) tools.

Summary of the design:

Error number: 2

Number of warnings: 69

Use of logic:

Number of slice Flip Flops: 7 886 on 15 360 51%

Number of 4-input lut: 16 104 on 15 360 104% (OVERMAPPED)

Distribution of logic:

Number of slots occupied: 8 744 7 680 113% (OVERMAPPED)

Number of slices only related logical container: 8 744 100% 8 744

Number of slices that contains no logical relationship: 0 to 8 744 0%

* See NOTES below for an explanation of the effects of unrelated logic.

Total number of 4 input lut: 17 400 on 15 360 113% (OVERMAPPED)

Number used as logic: 15 998

Number used as a middle way: 1 296

Number used as Rams 16 x 1: 82

Used number recorded the shift: 24

The logical Distribution report slice is not significant if the design is

too mapped to a resource not slices or if Placement fails.

Number of IOBs servile: 183 on 333 54%

BIO flip flops: 74

Number of RAMB16s: 1 24 4%

Number of MULT18X18s: 2 on 24 8%

Number of BUFGMUXs: 4 to 8 50%

Number of DCMs: 1 on 4 25%

Fanout of the Non-horloge nets on average: 3.38

Peak Memory use: 361 MB

Total in time REAL in the completion of the card: 1 dry 12 mins

Time CPU until the end of the total map: 1 dry 12 mins

NOTES:

Related logic is defined as logical that share connectivity - for example two

Lut are "related" if they share common inputs. During Assembly of the slices.

Card gives priority to combine the logic that is related. Generates so

best performance of synchronization.

Without logical report does share no connectivity. Card will start only packing

logic not related in a slice once that 99% of the slices are held through

logical packaging partners.

Note that once the logical distribution reaches the level of 99% by related

logical packaging, this does not mean the device is completely used.

No logical report package will begin, continuing until all usable LUTs

and FFs are busy. According to your timing budget, an increase in the concentrations of

logical packaging unrelated can adversely affect the performance of timing set

your design.

Mapping performed.

See the report of map file "toplevel_gen_map.mrp" for more details.

Problem encountered during the packaging phase.

Failure of the process 'Map '.Start time: 18:29:23

End time: 18:44:42

Total time: 00:15:19Can someone tell me why this error came?

Thank you best regards &,.

Vipin Ahuja

Vipin Hello,

It seems that your code requires more resources that are available on the FPGA. Optimizing your code can help to solve your problem:

You may have noticed some "Overmapping", mentioned in the newspaper:

Number of 4-input lut: 16 104 on 15 360 104% (OVERMAPPED)

Distribution of logic:

Number of slots occupied: 8 744 7 680 113% (OVERMAPPED)Take a look at this article:

http://digital.NI.com/public.nsf/allkb/060BA89FE3A0119E48256E850048FFFE?OpenDocument

And this:

http://digital.NI.com/public.nsf/WebSearch/311C18E2D635FA338625714700664816?OpenDocument

Kind regards

Navjodh

National Instruments

Maybe you are looking for

-

Satellite T110 - 10 X - blue screen when creating backup

I bought this netbook a week ago. First of all, I'm okay with windows 7 (home premium x 64-preinstalle) but in a few days, I loved. Yesterday, when I tried to make an image backup (for the first time) problem began. 1. in the creation of the back to

-

HP ENVY 15-u010dx: HP ENVY 15-u010dx

Hi, I have a HP ENVY 15-u010dx that will not start... no fans no lights at all, except the charging light doesn't turns white when it is plugged. It flashes also once very slowly. What does that mean? I have it apart and need help solving problems wi

-

upgrade dell optiplex gx620 to vista need driver for onboard sound plz help

dell optiplex gx620 to on-board sound card Vista upgrade is not compatible with Vista can anyone help with driver sound...

-

Microsoft Windows 8 PRO Downgrade to Windows 7 PRO

Greetings, This post is more than a complaint about Microsoft INABILITY to support its biggest business customers, in the hope that someone at Microsoft will really help me, instead of giving me the evasive that was given to me for the last 3 days...

-

character toggle Panel hides all docked panels

With the latest "upgrade" menu bar - "Character/paragraph rocker panel" hides all anchored panelsSee the link:http://www.mediafire.com/watch/93sucude9s1uncn/PS_characterPanel.MP4