Compilation of LabVIEW FPGA on crash RT cRIO 9082

Hello

I developed a project of NI VeriStand FPGA (see Project.png) for a target of 9082RT cRIO (which contains 2 cRIO: 9205 & 9264).

I have develop a piece of software code to run it on the chassis of RT cRIO 9082 because I never used this kind of front frame.

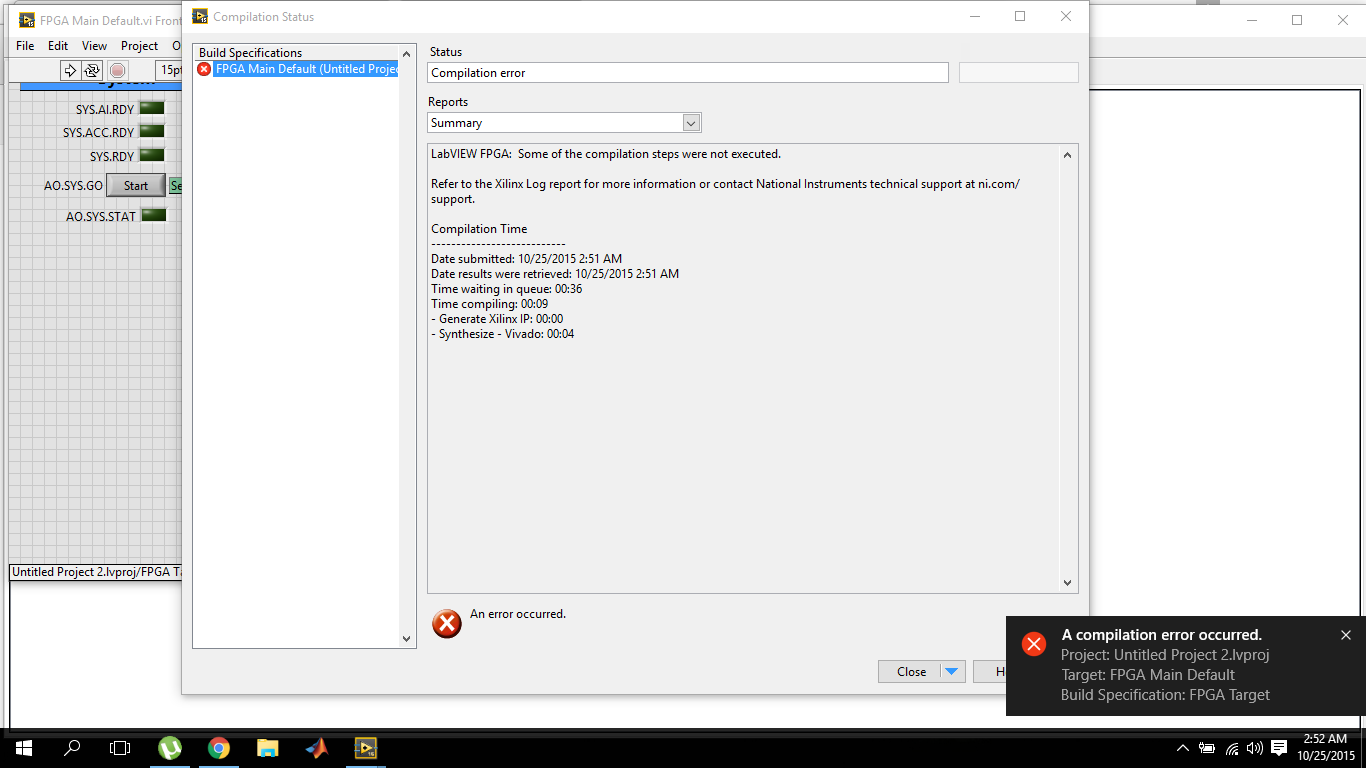

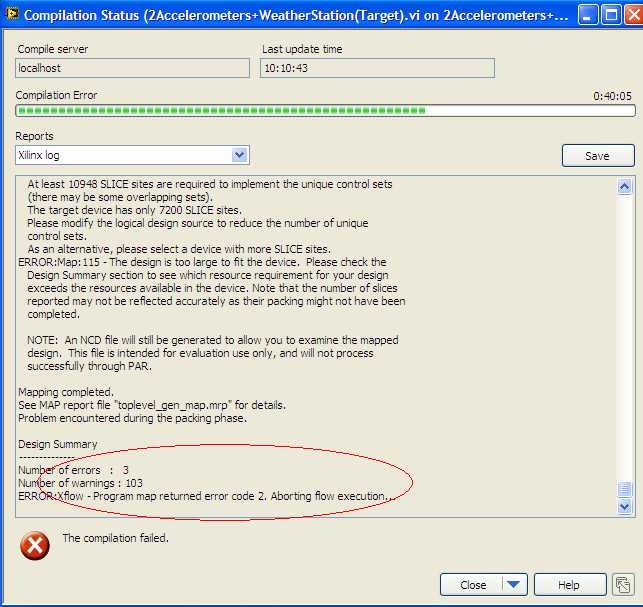

The problem appears when I tried to compile the FPGA.

Start the compilation, I see a pop-up (see Msg.bmp) and failed to compile (cf.). Details.bmp).

With the following error, I'm sure that the failure is not because of my code.

Can you help me?

I found the problem that comes from the installation of 2012 more develop.

When the FPGA module and 13.4 Xilinx tools is installed, the DLL 'LIBBz2.dll' (of the NIFPGA\...\Common\nt\Xilinx record 13.4 "is not copied in the following"C:\Windows\system32"folder.

After I manually copied this dll to the "system32" folder, I restart labview and the compilation was successful.

A. Kaszubiak

Tags: NI Hardware

Similar Questions

-

The project-centric issue of peer to Peer with an external compiler in LabVIEW FPGA

Hi all

FPGA OR Version: 14.0

I have an application developed in LabVIEW interfacing FPGAs developed in LabVIEW FPGA making of peer to peer Communications.

Everything works fine.

I try on the port to Visual Studio 2013 (on the same PC) and am able to communicate with the FPGA very well using the C API.

However, I have a problem now with the help files or the peer supported external compiler peer.

I get these errors:

1. cannot open the file source 'PublicIncludes/nistreamCommon/prefix.h '.

2. impossible opening the file source 'PublicIncludes/nistreamCommon/postfix.h '.

in

c:\Program Files (x 86) \National Instruments\Shared\ExternalCompilerSupport\C\include\nip2p.h

in my project...

I looked in the folder c:\Program Files (x 86) \National Instruments\Shared\ExternalCompilerSupport\C\include\ and the PublicIncludes\nistreamCommon folder does not exist.

What I am doing wrong?

Hello!

It seems that you have worked with another engineer of Applications on this issue. For the love of documents, the nip2p library is not supported in CVI. There has been cases where users were able to get this work to comment on the two header files.

Thank you!

-

LabVIEW FPGA: Problem compiling look-up Table

Current versions of software:

LabVIEW 2014 SP1

LabVIEW FPGA 2014

Xilinx Vivado

I'm having a huge problem in trying to compile my LabVIEW FPGA code.

Some recall of the code:

It's all in a SCTL.

I am streaming in a FIFO DMA and comparing it with the values previously stored in the shift registers (which are initialized to 0 at the start of the loop) in the SCTL.

The results of the comparison are then piled into a U16 and loaded into a lookup table (I use the LUT - 1 d), and I'm so help this LUT to decide what value will be charged to travel to record for the next iteration of the loop, which, in any case, would be either the current values of the flow, or the post previous registry value.

(It's a triage loop)

I am able to run very well in simulation mode code, but when I try to compile, I get this error:

"The selected object has a built-in shift register that makes the output on a particular loop iteration correspond to the entries in the previous iteration."

Connect the outputs of the object directly to a minimum number of nodes of Feedback or uninitialized shift registers. You cannot connect the outputs to another object.

See using LabVIEW for more information on the objects with registers embedded offset. »

Someone at - it ideas why this happens, and what might be the possible solutions?

I'm tempted to break it down into separate loops, but I prefer not to because it is now a loop (and working in my simulation).

I found my problem.

Any time that a LUT is in a chain shift register, it cannot:

1. be part of a string of shift register that has a variable initialized

2. follow-up to no decisive structure, like a box structure.

I just moved the position of LUT and it works.

-

When I compile a labview fpga VI, (my version of labview fpga is 2014), I get the not found error Xilinx 10.1 build tools.

But for 2014 labview, version 14.7 Xilinx is the only compatible and that I installed. But it is still asking for Xilinx version 10.1. I tried both with configured CompactRIO and also a vi without hardware. The same is repeated each time.

What can be the problem? Please help me.

Elodie

What FPGA target do you use? I think for Virtex 2 target Xilinx 10.1 tools are used.

-

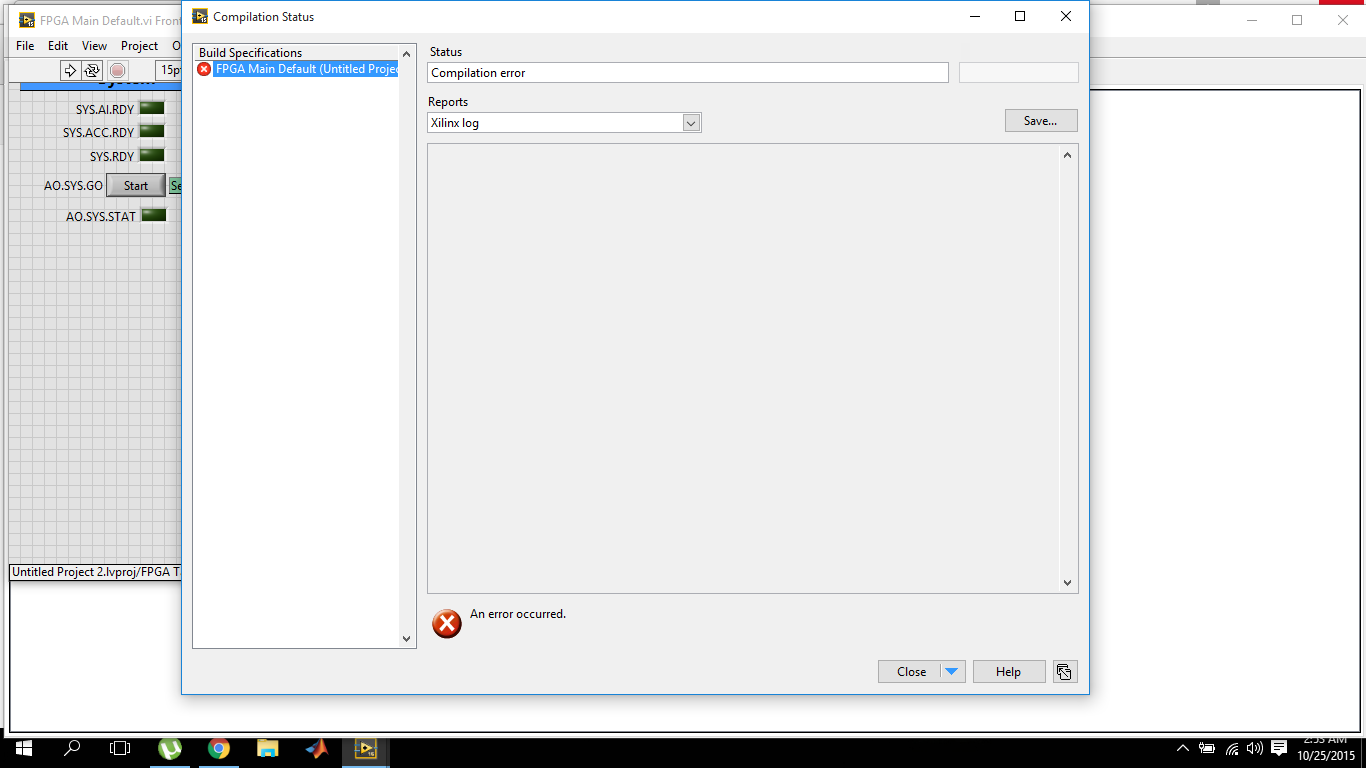

LabVIEW FPGA, 2015 compilation error

I've recently switched to LabVIEW 2015 and I'm working on OR myRIO. So also installed myRIO 2015 bundled software. The problem I have is that the compilation of fpga fails within 10 seconds.

and the target Xilinx journal report is empty

The first time when I tried to compile on 2015 version, it failed and the message box that failed came alongwith the avast antivirus warning for malicious activity. I reported it as wrong and now I tried several times with avast shield disabled control, but the results are the same. While the version of labVIEW 2014 works very well.

Now, I'm sure that there is something wrong with the installation of Vivado because this dll is part of it. The dll must be default in the2014_4\lib\win32.o directory C:\NIFPGA\programs\Vivado if you are using an operating system for 32-bit AND also in C:\NIFPGA\programs\Vivado2014_4\lib\win64.o If you use a 64-bit operating system. If the dll is not here, it is probably that the anti virus (I've never seen what happens to Xilinx but I have for other stuff).

I'm emphasizing the 2014_4 because LabVIEW 2015 uses Vivado 2014_4 while 2014 LabVIEW uses Vivado 2013_4. Since you have also installed LabVIEW 2014, you must have 2013_4 as well and if it works, you will find the dll I just wanted you make sure you check the correct directory for the Vivado 2014_4.

Download and install (reinstall or repair if already installed) 2015 LabVIEW FPGA Module Xilinx tools Vivado 2014.4. You can also use the DVD Setup if you have. It would be a good idea to do the installation with the disabled and even anti-virus try the first compilation the same. Try and let me know if the problem persists.

Kind regards

-

LabVIEW FPGA CLIP node compilation error

Hello NO,.

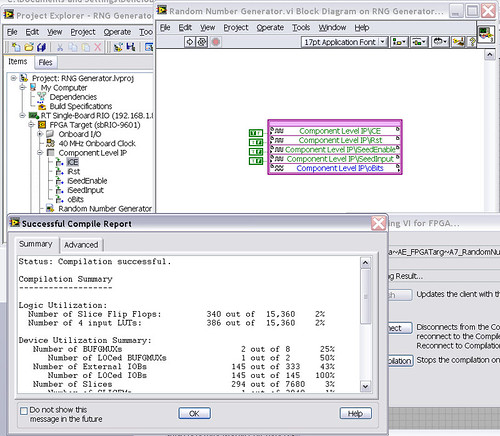

I work on an application for my Single-Board RIO (sbRIO-9601) and faced with a compile error when I try to compile my FPGA personality via the ELEMENT node. I have two .vhd files that I declare in my .xml file and all at this point works great. I add the IP-level component to my project and then drag it to the VI I created under my FPGA.

Within the FPGA personality, I essentially have to add some constants on the indicators and entries CLIP to my CLIP out and attempt to save/compile. With this simple configuration, I met a compilation error (ERROR: MapLib:820 - symbol LUT4... see report filling for details on which signals were cut). If I go back to my VI and delete indicators on the output (making the output pin of the CLIP connected to nothing), compiles fine.

I've included screenshots, VHDL and LV project files. What could be causing an indicator of the output of my VI to force compilation errors?

Otherwise that it is attached to the output ELEMENT, a successful compilation...

After that the output indicator comes with CLIP, compilation to fail...

NEITHER sbRIO-9601

LabVIEW 8.6.0

LabVIEW FPGA

Windows XP (32-bit, English)

No conflicting background process (not Google desktop, etc.).Usually a "trimming" error gives to think that there are a few missing IP. Often, a CLIP source file is missing or the path specified in the XML file is incorrect.

In your case I believe that there is an error in the XML declaration:

1.0

RandomNumberGenerator

urng_n11213_w36dp_t4_p89.vhd

fifo2.vhd

This indicates LV FPGA to expect a higher level entity called "RandomNumberGenerator" defined in one of two VHDL files. However, I couldn't see this entity in one of two files. If urng_n11213_w36dp_t4_p89 is the top-level entity, edit the XML to instead set the HDLName tag as follows:

urng_n11213_w36dp_t4_p89 Also - in your XML, you set the 'oBits' music VIDEO for output as a U32, however the VHDL port is defined as a vector of bits 89:

oBits: out std_logic_vector (89-1 downto 0)

These definitions must match and the maximum size of the vector CLIP IO is 32, so you have to break your oBits in three exits U32 output. I have added the ports and changed your logic of assignment as follows:

oBits1(31 downto 0)<= srcs(31="" downto="">

oBits2(31 downto 0)<= srcs(63="" downto="">

oBits3(31 downto 0)<= "0000000"="" &="" srcs(88="" downto="">Both of these changes resulted in a successful compilation.

Note: The only compiler errors when you add the flag because otherwise your CUTTING code is optimized design. If the IP is instantiated in a design, but nothing is connected to its output, it consumes all logic? Most of the time the FPGA compiler is smart enough to get it out.

-

Compilation of the variable results in LabVIEW FPGA

Hello. I would ask why LabVIEW FPGA generates different results of compilation for the same code. When I compile several times my code, the maximum speed and total changes bitfile slices generated according to the compilation, but I does not alter with the FPGA VI. In addition, is the precise relationship of compilation? Thank you

It's normal. The FPGA compiler starts to place pieces of code on the FPGA somewhat randomly and adjusts them until either the design adapts and responds to the criteria of the moment or there that the compiler determines that it cannot fit all the code and meet time constraints. The outputs that the FPGA VI generates when run will always be the same.

-

LabVIEW FPGA failure with compiler Xlinx?

I'm in LabVIEW FPGA 8.6 with NOR-RIO 3.0.1 (to 8.6). When I compile a simple program, I get the notorious:

«Error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

I checked the FPGA compile server and I ran the utility fixTlink.VI with no improvement. This produces two identical PC, neither one having a FPGA installed card.

Any ideas?

After further analysis, the problem was to be in our facility in LabVIEW FPGA 8.6. Using the correct Installer of NEITHER solved the problem.

This thread is now resolved.

-

LabVIEW fpga compile: translation error then again translate

Hello everyone,

I have a question about the process of compiling LV FPGA.

The context:

I am compiling a binary FPGA for the NOR-5644R (viterx6 inisde). the process is quite long (up to 7 hours depending on how is our CLIP). I am canvassing any idea of attaching the compilation process.

The fact:

By analyzing the log file of the previous compilation, I noticed that the stage translate is made twice, probably because one is a failure. the excerpt from log files are copy/paste below.

Further, it seems the errors (at least some of them) translate the first are induced by the commented lines of NOR provided file UCF (RfRioFpga.ucf)

The question:

Why to translate step to do it twice (the first being failed)? would it not quicker to make only the second succefull one? in other words, it is really necessary for the first fails to translate step for the FPGA binay?

Any ideas?

Thanks in advance!

See you soon,.

Patrice

----

log file extract 1:

"...

NGDBUILD Design summary of results:

Error number: 387

Number of warnings: 1443Total in time REAL until the end of the NGDBUILD: 2 h 16 min 45 s

Time CPU until total NGDBUILD: 2 h 11 min 21 secOne or more errors were found during the NGDBUILD. No file NGD will be written.

Writing the file of log NGDBUILD 'RfRioFpga.bld '...

'Translate' process failed

..."

log file excerpt 2:

"...

NGDBUILD Design summary of results:

Number of errors: 0

Number of warnings: 818Writing the file 'RfRioFpga.ngd '... NGD

Total in time REAL until the end of the NGDBUILD: 29 min 17sec

Time CPU until total NGDBUILD: 27 min 33secWriting the file of log NGDBUILD 'RfRioFpga.bld '...

NGDBUILD done.

'Translate' process completed successfully

..."

Hi Patrice,

It seems strange that it performs this step two times (and was worried when I saw the first time), but there is good reason for that, certainly. LabVIEW inserts constraints for components, he adds, but sometimes the components get optimized out by the compiler. When the compiler encounters stressed that points to the now non-existent component, it error. LabVIEW circumvents this by running the process to translate two times. The first time, it may fail. LabVIEW will remove the constraints that fail, then run again translate it. Unfortunately there is no way around this problem.

-

Please help me for this problem "error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

Look for the error on the Web site of or or on the forums. Take a look at the following links:

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=381394&requireLogin=false

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=205754&requireLogin=false

-

Internal software error of LabVIEW FPGA Module - 61499

I get the error next (in a pop-up window) in the phase of sompilation for the FPGA target with a vhdl IP. This error continues to occur even after restart LabVIEW and the PC. Someone at - it solved is this kind of problem before without having to re - install the software?

Here is the error information:

Error-61499 occurred at niFpgaXml_GetValue_String.vi<><><><>

Possible reasons:

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has occurred. Please contact National Instruments technical support on ni.com/support.

Additional information: lack the tag required XML (/ CompileServerList)

As a first step, I can compile the vhdl IP node successfully. However, once when I'm running a VI with the FPGA, the bureau stop working. After that I restarted by force, it cannot perform the build of a vhdl IP node. Even without connecing to the jury of LabView, he pointed out errors before the end of the sompilation.

Interestingly, the screw which also includes nodes IP vhdl that I properly compiled before, I can still run the VI to the Commission and it works correctly.

Thank you

Looks like your ActiveJobsList somehow has been corrupted. I saw occur when computers are hard stop or blue screen during compilation. I don't have that LabVIEW 2014 installed on my machine, so your path will be a little different, and the file extension will be a .txt or .xml instead of .json, but try this:

Move the file "C:\Program Files (x 86) \National Instruments\LabVIEW 2014\vi.lib\rvi\CDR\niFpgaActiveJobList.json" (or your equivalent) out of the above directory (back it upward and delete essentially) and restart LabVIEW. Must regenerate the file and resolve the problem.

-

cRIO-9082 DMA bandwidth between RT and FPGA

Hello

I would like to know the bandwidth the cRIO-9082 between FPGA and RT DMA? How many MB/s? I can't find the answer on the web page of NOR.

I know that there are 3 DMA channels, but how fast I could send data from FPGA to memory RT?

What is the optimum size of the element in the DMA channel? U8, U16, U32, or U64?

Material: cRIO-9082 RT

Software: LabVIEW 2012, 2012 LabVIEW FPGA

Best regards

Peter

CLA

-

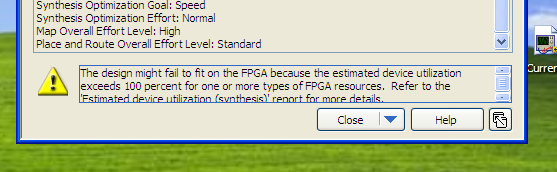

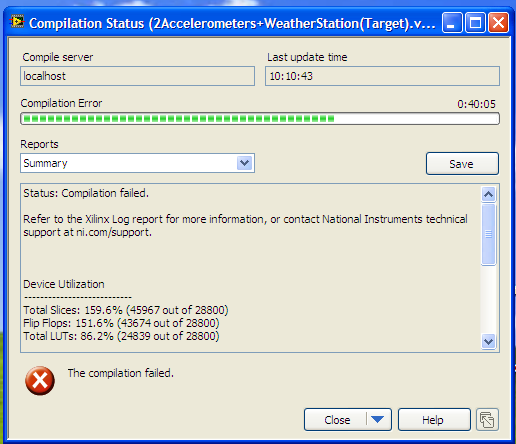

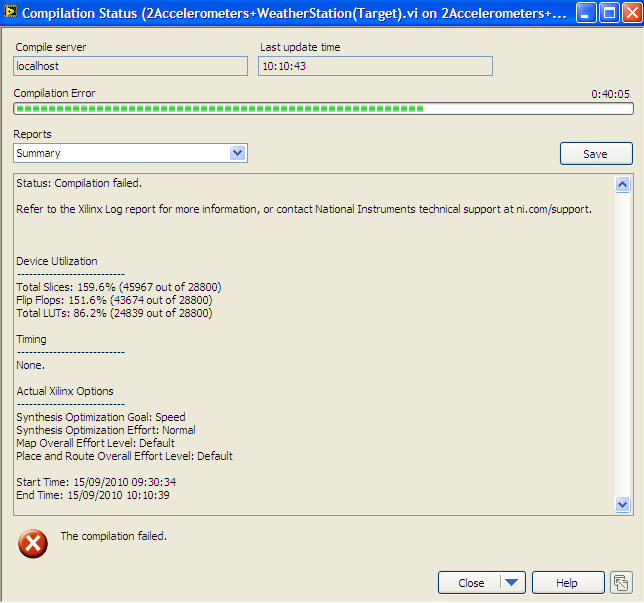

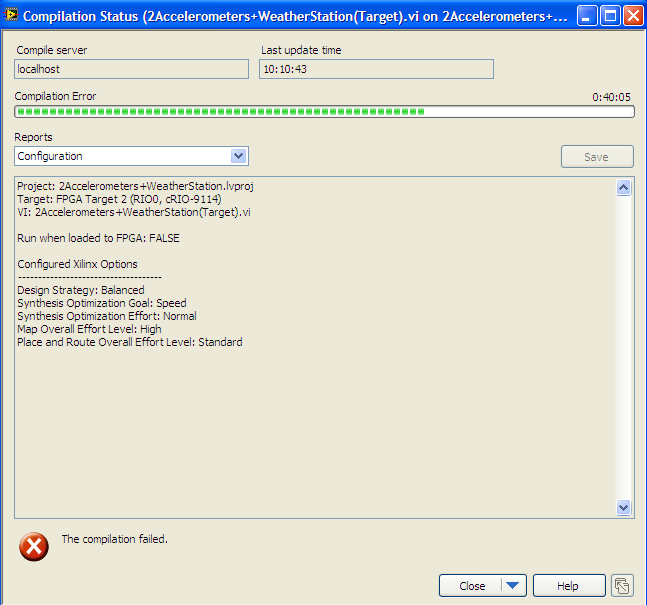

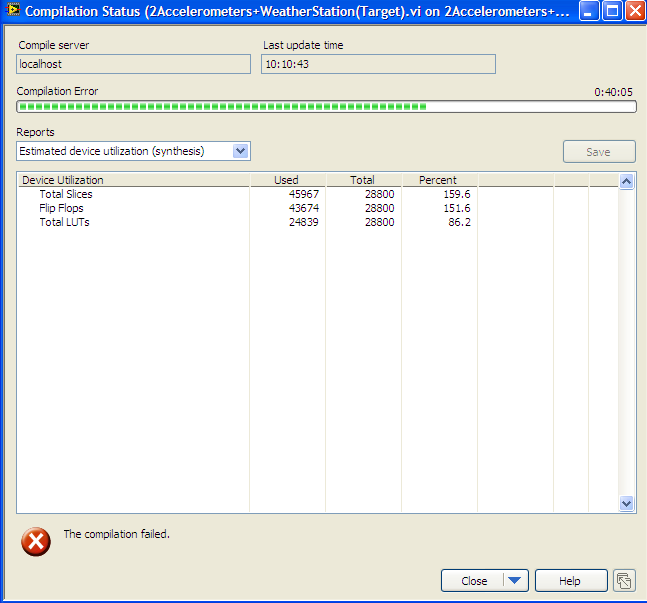

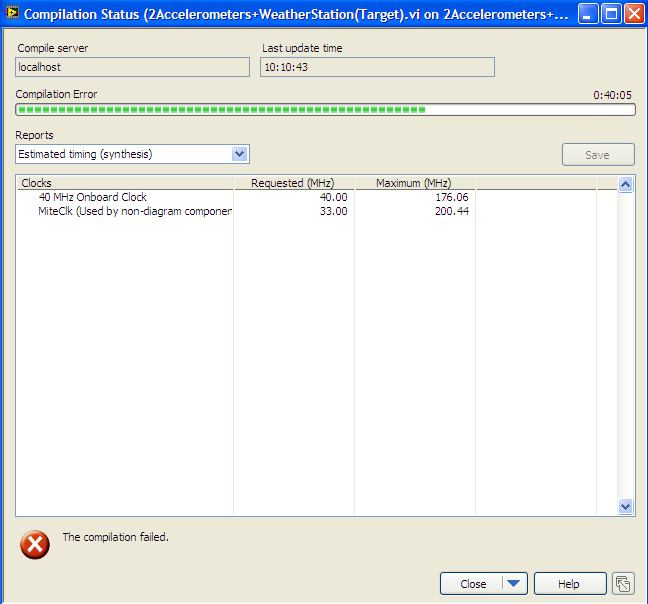

Failure of compilation of the FPGA target

Hi all

I met a problem when I tried to compile my target FPGA VI. Failed to compile for some reason any to halfway after start of the compilation. I post a few screen shots of the labview error information.

What causes this problem? How could I solve this problem?

Thank you very much!

Kind regards

masterwho

Also you have large networks on the Panel before the FPGA VI?

Or is there the great paintings inside the code?

If you can, put a piece of your code.

-

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has Unknown

Sir/Madam,

Note Labview 2012 SP1 installed about 2 weeks ago.,.

Accident occurred during the compilation of an fpga vi who worked satisfactorally in the past.

When I restarted and went to the message recomplile "LabVIEW FPGA: an internal software error in the LabVIEW FPGA Module" see attached picture of popup.

I reinstalled Labview in its entirety and backed out the changes I made to the vi but still get the same message.

Thanks in advance

Daryl

It turns out that the question was in the VI and not of LabView FPGA module as the message may indicate. I created a vacuum vi, cut and pasted items in this from the vi error and recompiled and it ran very well.

Somehow the vi has been corrupted internally.

Thank you it's fixed.

-

Hello

I'm working on 802.11 application, I tried to change the FPGA code.

I really need to compile all the code after changes? or just save the VI to observe the effects of the change.

Yes, LabVIEW code must be compiled using the FPGA Toolbox after you make all the changes. I think the only exception is when you run mode simulated on your PC.

Maybe you are looking for

-

Title. With hardware acceleration: http://imgur.com/jHRk6Yl words 'empty' look and really weird air instead of being "BOLD". But if I disable it, normal fonts look "weird" in some Web sites (not all) and are difficult to read.Any solution? Thank you!

-

Satellite Pro 6100 himself turn off

Hello I'm from the Italy. It is 3 days that my Satellite Pro 6100 after some time (it can be 30 minutes or 3 hours) close itself.I tried to update bios version 1.70 to 1.90 without any result. I tested my HARD drive and it works fine. I formatted and

-

Lenovo Y400 HDD partition after upgrade to 8.1 WIndows

I upgraded my Lenovo Y400 Windows 8.1, and I noticed that there are 8 partitions on disk 0. Is this normal? Otherwise, what partition I could merge/delete/resize without sacrificing the functionality of One (OKR) key recovery? I want to buy SSD in th

-

I can't understand how we get to the bios screen. In the past it has screen on boot up that say press F2 or similar to get into the bios.

-

What is slp_dd_hathi_110_017.exe and how do I?

Hi- I was repairing a corrupted install of Windows XP on a Dell laptop, and as part of what I have been reinstalling and updated the drivers for my Photosmart C7280. I went to HP and Support drivers for my printer and OS, and methodically downloaded