DB trigger compile errors

HelloI need AFTER THAT INSERT ON WH_I_ITEMS not null values between 2 inserted in WH_TRANSACTIONS

CREATE OR REPLACE TRIGGER TRANSACTIONS_INSERT

AFTER INSERT ON WH_I_ITEMS

REFERENCING NEW AS NEWS OLD AS OLDS

FOR EACH ROW

BEGIN

INSERT INTO WH_TRANSACTIONS VALUES (

:NEWS.STORE_ID := :OLDS.STORE_ID ,

:NEWS.TRANSACTION_SERIAL := :OLDS.TRANSACTION_SERIAL +1,

:NEWS.TYPE_ID := 9 ,

:NEWS.TRANSACT_NUMBER = 1,

:NEWS.TRANSACT_DATE := SYSDATE );

END;

/SQL> SHOW ERRORS

Errors for TRIGGER TRANSACTIONS_INSERT:

LINE/COL ERROR

-------- ----------------------------------------------------------------

2/6 PL/SQL: SQL Statement ignored

3/33 PL/SQL: ORA-01745: invalid host/bind variable name

4/3 PLS-00049: bad bind variable 'NEWS.TRANSACTION_SERIAL'

4/36 PLS-00049: bad bind variable 'OLDS.TRANSACTION_SERIAL'

5/3 PLS-00049: bad bind variable 'NEWS.TYPE_ID'

6/3 PLS-00049: bad bind variable 'NEWS.TRANSACT_NUMBER'

7/1 PLS-00049: bad bind variable 'NEWS.TRANSACT_DATE'Abdetu...

Your syntax in the manual is incorrect, it should be something like

INSERT INTO WH_TRANSACTIONS VALUES (

:OLDS.STORE_ID,

col2,

..

);

Tags: Oracle Development

Similar Questions

-

HI I have a little myself refreshing on oracle so I don't know what I have beening hurts but after looking at the code for half a day, I can not yet understand what's wrong, I double check most of the thing and it looks good from what I understand. Can someone help me find the problem? the problem is what is stated in the subject and I am using 10g express edition.

CREATE TRIGGER tr_validateDoubleBooking

BEFORE INSERTING

ON the time range

FOR EACH LINE

DECLARE

Time to tank (5);

Date DATE;

Tank installation (10);

FacilityBooked EXCEPTION;

BEGIN

Select ts_Time, ts_Date, time, Date, slot facilities installation

where Facility =: NEW.facility and ts_Time =: NEW. Time and ts_Date =: NEW. Date;

IF (= installation: NEW.) Installation and time =: NEW. Date and hour =: NEW. Date) then

RAISE FacilityBooked;

END IF;

EXCEPTION

When FacilityBooked THEN

raise_application_error (-20300, 'The Room' | to_char(:New.)) Facility) |' has already been reserved ");"

While OTHERS THEN

raise_application_error (-20299, ' there may be an error with the database ');

End tr_validateDoubleBooking;

/Change your 'Date' and variable 'Time' to something like T_DATE, because the DATE is a keyword

as well;

-- change this Time char(5); Date Date; -- to this l_Time char(5); l_Date Date;and change the rest of your code accordingly

In addition, you cannot select the same table you have a trigger on:

Find out about the mutation of trigger for this example:http://www.morganslibrary.org/reference/table_trigger.html

Published by: bluefrog on July 2, 2010 14:45

-

The 11g trigger compile errors

Using the 11g Win 2008 Server 64 bit. I am trying to create a trigger that willl automatically calculate the total cost of an item of the requested quantity multiplied by unit cost. The trigger is used to bypass user input if the cost toal of an element is empty. I tried the following syntax variations and would appreciate advice on the proper syntax to use. Thank you, J

CREATE OR REPLACE TRIGGER prodreq_qtycalc

AFTER INSERT ON PRODUCT_REQUIREMENTS

FOR EACH LINE

BEGIN

IF: OLD. TOTALCOST IS NULL

THEN UPDATE PRODUCT_REQUIREMENTS

SET: NEW. TOTALCOST = (UNITCOST * QTYNEEDED);

END;Jay wrote:

Using the 11g Win 2008 Server 64 bit. I am trying to create a trigger that willl automatically calculate the total cost of an item of the requested quantity multiplied by unit cost. The trigger is used to bypass user input if the cost toal of an element is empty. I tried the following syntax variations and would appreciate advice on the proper syntax to use. Thank you, JCREATE OR REPLACE TRIGGER prodreq_qtycalc

AFTER INSERT ON PRODUCT_REQUIREMENTS

FOR EACH LINE

BEGIN

IF: OLD. TOTALCOST IS NULL

THEN UPDATE PRODUCT_REQUIREMENTS

SET: NEW. TOTALCOST = (UNITCOST * QTYNEEDED);

END;As a general rule, it's a BAD design to store the value calculated online.

What happens if UNITCOST or QTYNEEDED is NULL?

1 CREATE OR replace TRIGGER prodreq_qtycalc 2 before INSERT ON product_requirements 3 FOR each ROW 4 WHEN (old.totalcost IS NULL) 5 DECLARE 6 BEGIN 7 :NEW.totalcost := ( :old.unitcost * :old.qtyneeded ); 8* END prodreq_qtycalc; SQL> / Trigger created. -

Error FRM-40735: trigger ON-ERROR raised unhandled exception ORA-01001

When I want to create a new project the form send this error message:

FRM-40735: trigger ON-ERROR raised unhandled exception ORA-01001

I already compile forms, they ran autoconfig and has no

Forms is: PAXPREPR

the module is: projects

EBS version: 11.5.10.2

DB: 11.2.0.3.0

Please see:

PAXPREPR - creating a project gets error FRM-40735: error Trigger & ORA - 01001 (Doc ID 417218.1)

PAXPREPR - FRM-40735 when you try to copy the project template after you have entered a fast entry (Doc ID 417537.1)

Thank you

Hussein

-

where to see the compile error

Hello

on 10 gR2, I created a trigger and received after WARNING:

Where can I see the compile error?Warning: Trigger created with compilation errors.

Thank you.Dear Sir

Question displays the error message; SQL command more. You will get the error message.

Kind regards

Srikanth -

FRM-40735: trigger ON-ERROR raised unhandled exception ORA-06508

Hello

We are the migration form 6i to 10g (10.1.2.0.2) with HP_UX. Here are the steps I took

1. I compiled all the forms/pll/menu locally using Shift + Ctrl + k, and Clt + T and saved in the folder (local_10g).

2. then all copied from local_10g to the file (unix_10g) in Unix.

3 compiled it using the command Frmcmp and got all the mmx, plx successfully and most of the fmxs. (some of FMAS throw error).

4 copied all fmx, plx, mmx to unix (unix_10g) folded in my forms_prod say local.

5. when I run fmb in my local forms_prod folder, I have error FRM-40735: trigger ON-ERROR raised unhandled exception ORA-06508.

I added location c:\forms_prod in Forms_path (regedit) and Forsm_Path (default.env). (for locals)

I added the location of u01\unix_10g in Forms_Path (default.env) on unix.

Please let me know what and where I am doing wrong? I'd really appreciate your help.

Thank you

SandyHello

In General, you have to compile the module on each of the target servers, because the executable modules are not portable.

François

-

Xilinx Compilation error: Formal HDLCompiler:432 < eiosignal > has no real or default value

Hello

I've compiled several programs for sbRIOs previously but did not run in before compile errors. I can't find any support to see what is actually wrong. Any help with this would be appreciated!

The summary of the situation of the Compilation is:

LabVIEW FPGA: Compilation failed due to an error of xilinx.

Details:

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000031_SequenceFrame.vhd" line 87: Formalhas no real or default value.

INFO: TclTasksC:1850 - enforcement process: synthesize - XST is made.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000032_CustomNode.vhd", line 18. eiosignal is declared here

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000031_SequenceFrame.vhd" line 106: Formalhas no real or default value.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000033_CustomNode.vhd", line 18. eiosignal is declared here

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000031_SequenceFrame.vhd" line 125: Formalhas no real or default value.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000034_CustomNode.vhd", line 18. eiosignal is declared here

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000031_SequenceFrame.vhd", Line 144: Formalhas no real or default value.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000035_CustomNode.vhd", line 18. eiosignal is declared here

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000031_SequenceFrame.vhd" line 163: Formalhas no real or default value.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000036_CustomNode.vhd", line 18. eiosignal is declared here

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000031_SequenceFrame.vhd" line 182: Formalhas no real or default value.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000037_CustomNode.vhd", line 18. eiosignal is declared here

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000031_SequenceFrame.vhd", line 201: Formalhas no real or default value.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000038_CustomNode.vhd", line 18. eiosignal is declared here

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000031_SequenceFrame.vhd" at line 220: Formalhas no real or default value.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000039_CustomNode.vhd", line 18. eiosignal is declared here

ERROR: HDLCompiler:854 - "C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000031_SequenceFrame.vhd" line 50:Unit ignored due to previous errors.

File VHDL C:\NIFPGA\jobs\R6n310u_Z1R8lYC\NiFpgaAG_00000031_SequenceFrame.vhd ignored errors-->

Total memory use is 189944 kilobytes

Number of errors: 9 (0 filtered)

Number of warnings: 4 (filtered 0)

Number of news: 0 (0 filtered)"Synthesize - XST" process failed

I had similar errors (not real or by default) then compile using the code LV would not remove, but the compiler Xilinx would be due to determine it was unused. It is usually inaccessible code with a register read in the main loop, but write it to enroll in a deal structure that would not be executed. Differences in the ability of the LV compiler or compiler of Xilinx to decide what is safe to delete this could lead.

Other times we had errors when a clock has been specified in the file of constraints, but the clock was not used.

Maybe one of these two seemingly unrelated points might help.

Shane.

-

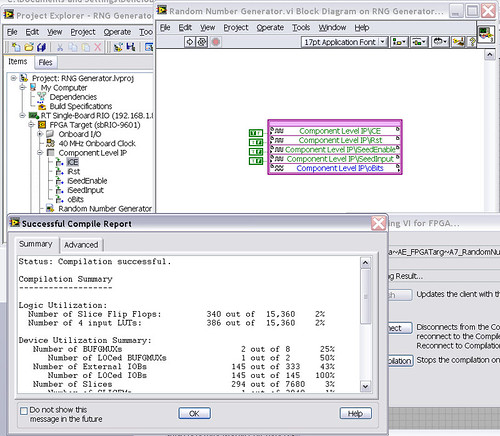

LabVIEW FPGA CLIP node compilation error

Hello NO,.

I work on an application for my Single-Board RIO (sbRIO-9601) and faced with a compile error when I try to compile my FPGA personality via the ELEMENT node. I have two .vhd files that I declare in my .xml file and all at this point works great. I add the IP-level component to my project and then drag it to the VI I created under my FPGA.

Within the FPGA personality, I essentially have to add some constants on the indicators and entries CLIP to my CLIP out and attempt to save/compile. With this simple configuration, I met a compilation error (ERROR: MapLib:820 - symbol LUT4... see report filling for details on which signals were cut). If I go back to my VI and delete indicators on the output (making the output pin of the CLIP connected to nothing), compiles fine.

I've included screenshots, VHDL and LV project files. What could be causing an indicator of the output of my VI to force compilation errors?

Otherwise that it is attached to the output ELEMENT, a successful compilation...

After that the output indicator comes with CLIP, compilation to fail...

NEITHER sbRIO-9601

LabVIEW 8.6.0

LabVIEW FPGA

Windows XP (32-bit, English)

No conflicting background process (not Google desktop, etc.).Usually a "trimming" error gives to think that there are a few missing IP. Often, a CLIP source file is missing or the path specified in the XML file is incorrect.

In your case I believe that there is an error in the XML declaration:

1.0

RandomNumberGenerator

urng_n11213_w36dp_t4_p89.vhd

fifo2.vhd

This indicates LV FPGA to expect a higher level entity called "RandomNumberGenerator" defined in one of two VHDL files. However, I couldn't see this entity in one of two files. If urng_n11213_w36dp_t4_p89 is the top-level entity, edit the XML to instead set the HDLName tag as follows:

urng_n11213_w36dp_t4_p89 Also - in your XML, you set the 'oBits' music VIDEO for output as a U32, however the VHDL port is defined as a vector of bits 89:

oBits: out std_logic_vector (89-1 downto 0)

These definitions must match and the maximum size of the vector CLIP IO is 32, so you have to break your oBits in three exits U32 output. I have added the ports and changed your logic of assignment as follows:

oBits1(31 downto 0)<= srcs(31="" downto="">

oBits2(31 downto 0)<= srcs(63="" downto="">

oBits3(31 downto 0)<= "0000000"="" &="" srcs(88="" downto="">Both of these changes resulted in a successful compilation.

Note: The only compiler errors when you add the flag because otherwise your CUTTING code is optimized design. If the IP is instantiated in a design, but nothing is connected to its output, it consumes all logic? Most of the time the FPGA compiler is smart enough to get it out.

-

LV 2011 (and 2012 LV) compilation error. Size not valid in _InstSize: 21

I created a Subvi in LV8.5 to manage events UI outside a main vi. The Subvi gets control references who are registered for the events, through a queue that all actions are sent to a consumer case, nothing complicated. Everything works fine in LV8.5, but now I got all LV2011SP1 on a Windows 7 64 bit and I still get the same error:

"Compile error. Report this issue to National Instruments Tech Support. Invalid size in _InstSize 21 "

which appears 3 times. I tried to open the same code also in LV2012, same error... When you try to isolate the problem, I discovered that by disabling the code in 3 cases of greater consumption that I can get rid of the warning, but then I can't reduce the problem to one...

Any ideas?

Yes, the thing to put 'problem' labview code into a Subvi its own helped me as well.

My speculation is that it forces the choice of another compiler (without the bug) path when compiling the source of the LV.

I think you should file a bug report using the pages of http://ni.com/support .

In this way we will have better tools in the future.

BR,

/ Roger

-

Compiler error. Report to Technical Support OR: err c = 0xF1 ufppushop

Compiler error. Report to Technical Support OR: err c = 0xF1 ufppushop

When recording / runing a vi that performs calculations in a node formula containing several if and a switch statement. (LV6.1, WinNT)

I solved the problem: the compile error occurred because a single formula node entry was an enum.

When you insert a cast to digital, the problem has been resolved. -

DMA FIFO of FPGA compilation error

Hello

I have a cRIO 9074 with FPGA. I tried a simple piece of code to learn how to acquire the data that is generated on the FPGA at a rate of 10 KHz and transfer it to the host VI to treat later in offline mode. However, I meet this compilation error when you compile the FPGA VI base containing a node to write FIFO (photo of the VI attached below). In compiling the report, it is said that there are 256 RAM Block used (the total number is 40), so an error has occurred. The error notification of exact compilation from Xilinx report is reproduced below:

# From the PAM program

# o toplevel_gen_map.ncd - intstyle xflow-calendar toplevel_gen.ngd map

toplevel_gen. FCP

#----------------------------------------------#

"Target part using" 3s2000fg456-4 ".

Design of mapping in the lut...

Guided running of packaging...

Running based on the delay of packaging of LUT...

ERROR

ack:2310 - type compositions "RAMB16" too found to adapt to this device.

ack:2310 - type compositions "RAMB16" too found to adapt to this device.ERROR: card: 115 - the design is too large to fit the device. Please consult the Design summary section to see what resource requirements for your design exceeds the resources available in the device. Note that the number of slices don't notice it that their packaging could not be completed accurately.

NOTE: A file NCD will be always generated to allow you to examine the mapped design. This file is intended for evaluation use only and will not be processed successfully by means of BY.

Mapping performed.

See the report of map file "toplevel_gen_map.mrp" for more details.

Problem encountered during the packaging phase.

Summary of design

--------------

Error number: 2

Number of warnings: 125

ERROR: Xflow - card program returned the error 2 code. Aborting the workflow execution...

Bitstream not created

Time history analysis

What does that mean? How can I fix this error?

Thank you

Bogdan

Hey,.

Have you already tried to reduce the size of the FIFO memory?

Christian

-

Outside regs, reg 1239 compiler error

I installed LV2009 and trying to open the version 8.6 vi.

I get a message "compilation error. Report this problrm to Technical Support from National Instruments. off-regs - no release candidate has found, reg 1239! »

32-bit client of Labview on Win 7 64 bit and Win Server 2008 64 bit give the same error.

The attached code.

Technical support NOR suggested installation LV 2009 service pack 1, which fixed the problem.

-

Hello

If I declare a const, which is based on a value previously declared const I get a compilation error:

const int MY_INT_CONST1 = 10; no error.

const int MY_INT_CONST2 = MY_INT_CONST1 + 10; compile error: initializer must be constantI tried to search the Internet to see if this goes against ANSI-C, but did not find the relevant answer.

Anyone who knows and who have a source of information?

Thank you!

dml72

Hello

As I remember, in ansi C, global variables must be initialized by constants.

So, we can write:

# define MYVAR 5

int a = MYVAR;

because the preprocessor replace MYVAR by 5 before compiling the sources.But if we write

const int a = 1;

const int b = a;We want to initialize b with the value of a, which is a global variable and the compiler should detect an error (declare a constant variable will generate a compiler error if the variable is reassigned to the program, but is still a variableand not a constant).

The same compilation error should appear if write us in the global section

int a = 1;

int b = a;

int c = myFunc ();

However in the locals, initialiseur initializer is not necessary to be consistent, so we can write

void myFunc (void) {}

const a = 1;

const b = a;

c const = myfunction2 ();

...

}In summary, the keyword "const" is not the reason for this error, you can add or remove this keyword, the error will always be the same.

It is simply impossible to initialize a global variable with another variable as global variables are initialized before executing any statement.

Concerning

Etienne

-

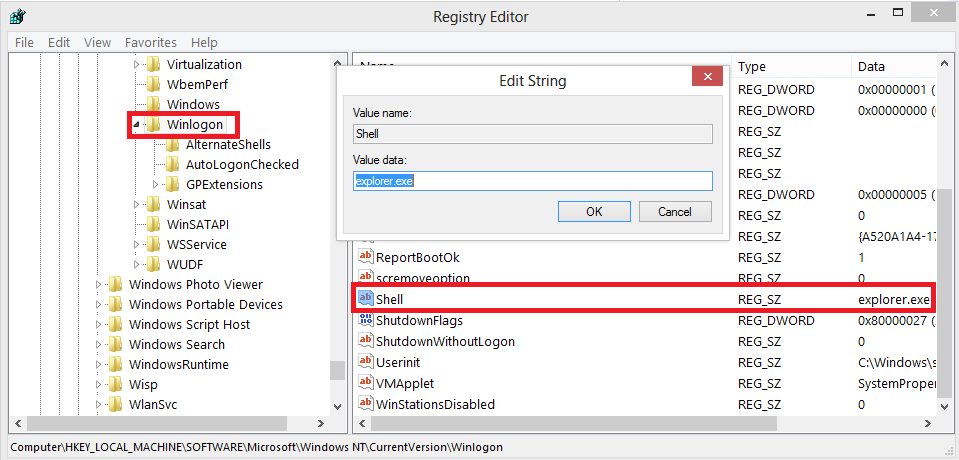

Microsoft JScript compilation error CODE 800A03f7

The error comes whenever I'm away from the computer. The error comes in this way, as shown below:

Windows Script Host

Script: C:\User\Avinash (it's administrator name)\AppData\Roaming\4e5f\5849.js

Line: 1

Char: 21949

Error: Constant not terminated string

Code: 800A03F7

Source: Microsoft JScript compilation errorThe error comes whenever I'm away from the computer. The error comes in this way, as shown below:

Windows Script Host

Script: C:\User\Avinash (it's administrator name)\AppData\Roaming\4e5f\5849.js

Line: 1

Char: 21949

Error: Constant not terminated string

Code: 800A03F7

Source: Microsoft JScript compilation erroron the other

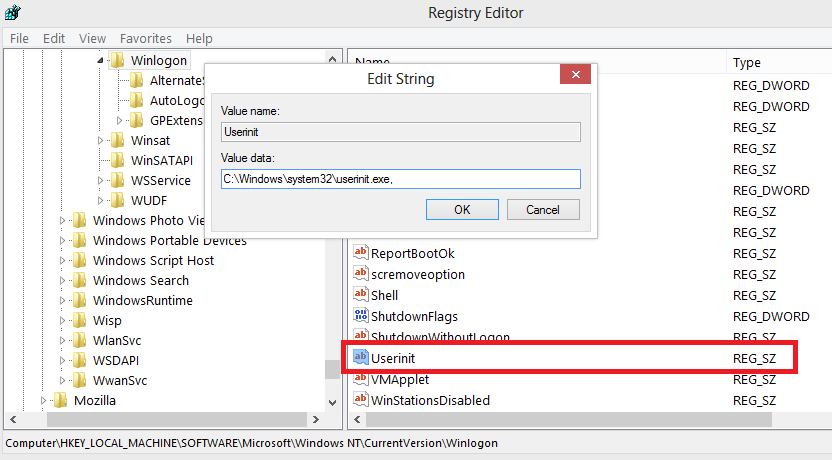

Go to start > run and type regedit and enter

Go to HKEY_LOCAL_MACHINE\SOFTWARE\Microsoft\Windows NT\CurrentVersion\Winlogon

On the right, look for Shell which should have value of explorer.exe just just like that... All right of explorer.exe, delete if there is nothing.

(This is the correct way, it should be)

(3) under the same key Winlogon also look for Userinit check if it is as in the picture... it's the way it should be...

(This is the correct way, it should be)

-

Hello when I try to compile my code it gives me the compile error!

I've seen this page

http://digital.NI.com/public.nsf/allkb/311C18E2D635FA338625714700664816

and I tried a lot to adapt to my code! reduced use of the lut of 107 to 101%, but he actually uses Interpolation spline 4times separately to move 4 motors! that it overlooked,

I also enclose my code!

Please take a look at reduced fpga4 and rt4reduced! N give me suggestions how can I reduce space, and if this compilation error is indeed bcz of space! This is the maximum can reduce the code! all Motors must move simaltaneously so I can't think about using a spline function unique move one, then the other engine!

Please find the code and the report of the attachmenet1

Sara

Maybe you are looking for

-

How to remove the download button located next to my home button?

-

The EA6700 supports 3 and 4 TB of drives such as the Seagate STBV3000200 or Seagate STBV4000200 on the USB 3.0? Steve

-

Update Windows 10. It will set up my SSD?

So I just signed up for the update of Windows 10. However, before downloading, I would like to know if it will delete everything on my C: drive (where my Windows 7 is installed). It will keep my same, or what things I need to backup the drive on an e

-

Well, if im getting very annoyed, I have a computer laptop hp mini 110, I don't remember the password because I haven't used for a while so im trying to wipe completely like a reset password usb work noy what f11 so that never does not give me am res

-

A hard drive can be used for readyboost in win 7?

I wanted to use one of my HARD drive for readyboost. How to do?