FPGA memory during construction errors...

I am building an FPGA application for a sbRIO-9636. I just added an element of memory to act as a circular buffer.

The element of memory is the size of 414000 U8 points. When I build, I get an error in the status of compilation window that starts like this.

«LabVIEW FPGA: compilation failed due to an error of Xilinx.»

Details:

ERROR: sim - user configuration exceeds the number of BRAM in the selected device

ERROR: sim:963 - initializer property intellectual could not set the basic model IP IP settings

ERROR: sim - user configuration exceeds the number of BRAM in the selected device

ERROR: sim - could not initialize the IP model.

ERROR: sim - generator execution failure of Tcl.

ERROR: sim - failed generation 'ReallyLongUniqueName_ReallyLongUniqueName '. Failed to run generator for Tcl.

ERROR: sim:877 - error detected during execution of intellectual property "block memory generator v7.3.

Release 14.7 - Xilinx CORE Generator P.20131013 (nt) Copyright (c) 1995-2013 Xilinx, Inc. All rights reserved.

I have attached the error any reading.

Help, please!

I just realized why I see this error. The sbRIO-9636 comes with 2 088 kbits of RAM block. I missread the quantity in 2 088 kbytes of RAM block, me wanting to use 414000 bytes will not work.

Thanks to all those who are looking into that.

Tags: NI Software

Similar Questions

-

FPGA an internal software error occurred. writing of memory

Hello world

We encounter an error during the compilation of an FPGA VI. It is probably related to our use of block FPGA memory. We have a non-timed while loop which is reading a host-target FPGA FIFO and writing in memory block (inside a Subvi called z_scan_write.vi). In another loop (this one is timed loop), there's a Subvi we called z_scan_read.vi, within which read us of the memory block.

Does anyone have an idea what goes wrong and how to avoid this problem? Thank you very much in advance for any suspicion!

The full error message is as follows. Note that this is for the two subVIs z_scan_write.vi and z_scan_read.vi...

An internal software error occurred. Please contact National Instruments technical support on ni.com/support with the following information:

nirviUIDToObject.vi

Error getting of to the UID object reference.

All the analyzed text:

-61060

C:\Program Files (x 86) \National Instruments\LabVIEW 2010\vi.lib\rvi\ClientSDK\Core\ErrorReporting\Private\nirviPersistentNameToProjectItemLineInfoCallback.vi

zIntensityTuples/{29C03A58-DC8D-4BC7-BAFA-66AFAE4E42D1}/%s

ProjItem

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.z_scan_write.vi_FPGACompileCopy00000021.VI

2747

Memory write 'memory method Node '.

ProjItem

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.z_scan_read.vi_FPGACompileCopy00000001.VI

194

Reading memory "memory Node method.

ProjItem

-61060

C:\Program Files (x 86) \National Instruments\LabVIEW 2010\vi.lib\rvi\ClientSDK\Core\ErrorReporting\Private\nirviPersistentNameToProjectItemLineInfoCallback.vi

zIntensityTuples/{29C03A58-DC8D-4BC7-BAFA-66AFAE4E42D1}/%s

ProjItem

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.z_scan_write.vi_FPGACompileCopy00000021.VI

2747

Memory write 'memory method Node '.

ProjItem

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.z_scan_read.vi_FPGACompileCopy00000001.VI

194

Reading memory "memory Node method.

ProjItem

-61106

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI

NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI

2

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.main.vi_FPGACompileCopy00000001.VI

2803

Subvi: ' NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI'

3

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.main.vi_FPGACompileCopy00000001.VI

2816

Subvi: ' NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI'

-61106

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI

NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI

2

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.main.vi_FPGACompileCopy00000001.VI

2803

Subvi: ' NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI'

3

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.main.vi_FPGACompileCopy00000001.VI

2816

Subvi: ' NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI'

-61106

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI

NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI

2

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.main.vi_FPGACompileCopy00000001.VI

2803

Subvi: ' NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI'

3

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.main.vi_FPGACompileCopy00000001.VI

2816

Subvi: ' NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI'

-61106

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI

NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI

2

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.main.vi_FPGACompileCopy00000001.VI

2803

Subvi: ' NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI'

3

1

C:\NIFPGA\compilation\FPGAWrapperAK101_PXI-7813R_main_C0C9511F\MungedForFPGA\NI. Munge.main.vi_FPGACompileCopy00000001.VI

2816

Subvi: ' NEITHER. Munge.generate_DAC_voltages.vi_FPGACompileCopy00000001.VI'

We could solve the problem. It was actually caused by the fact that we had set some subVIs to not reentrant. Their semifinal implementation (with the option to clone preallocate) solved the problem.

-

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has Unknown

Sir/Madam,

Note Labview 2012 SP1 installed about 2 weeks ago.,.

Accident occurred during the compilation of an fpga vi who worked satisfactorally in the past.

When I restarted and went to the message recomplile "LabVIEW FPGA: an internal software error in the LabVIEW FPGA Module" see attached picture of popup.

I reinstalled Labview in its entirety and backed out the changes I made to the vi but still get the same message.

Thanks in advance

Daryl

It turns out that the question was in the VI and not of LabView FPGA module as the message may indicate. I created a vacuum vi, cut and pasted items in this from the vi error and recompiled and it ran very well.

Somehow the vi has been corrupted internally.

Thank you it's fixed.

-

Find Permutations using perms in MathScript throws memory is full error

I use the perms Mathscript function to find the possible permutations of the numbers to a number in a table. According to the Help function permanent , he agrees to 15 items or less. I can feed this function up to 9 items, but when I try 10 I get the error: LabVIEW: memory is full. I increased virtual memory by the suggestion in why I am getting "memory is full" error KB.

The error occurs when Windows Task Manager reached 628 M no matter what I change my virtual memory. I have 2 GB of RAM in my computer. Any suggestions?

Thank you

What is expected. With N = 10, the final matrix will be 10! x 10, or approximately 36Million DBL elements. Each contains 8 bytes, which bears the imprint to ~ 290 MB for a single copy of the matrix of results expected.

Looking at the memory usage of the VI for N = 9, is already 100 MB, so it seems there are about 4 copies of the final table in memory. No wonder that N = 10 is impossible.

I recommend to the instruments in plain LabVIEW (son and loops) with a data type of U8, you will probably be able to go higher than 9.

Remember that 15 is unrealistic, because the dimensions of the matrix are I32, but the size of the array will be N!. This means that you don't have enough lines for example N > 12 anyway.

You have a good reason that you need such huge tables?

-

How to remove obsolete downloaded programs files, memory dump window, error reports window xp

How to remove obsolete downloaded programs files, memory dump window, error reports window xp

Use the disk cleanup tool in Windows XP to clean several types of files and folders are no longer, you want or need.

"lauraschenberg" wrote in the new message: * e-mail address is removed from the privacy * _xp...

How to remove obsolete downloaded programs files, memory dump window, error reports window xp

http://answers.Microsoft.com/message/422fde34-2f99-464c-B6C9-a36c63e2155b

Tags meta-tags: performance; windows_xpMonday 9 April 2012 08:05:37 + 0000: CreateMessage lauraschenberg

-

Parity memory of motherboard errors

I have a Dell Inspiron 2 gb laptop core duo with Windows Vista. The computer will boot into safe mode without error. Start in normal mode, always gives a message "parity memory, hardware dealer error contact, shut down system" blue screen. There is no memory provided address to determine if the parity memory is on the motherboard or memory cards. I tried using only 1 GB memory card and the two cards does not. With the help of new results in the same error message memory cards. Therefore, I conclude that the faulty memory is on the motherboard.

Of course, the warranty has expired.

In the past, I assigned the faulty memory to a virtual disk and told the owner not to use the virtual disk. This technique WORKED under versions of Windows prior to Vista. I can not any reference to the virtual disks in vista (in the less definable at the start).

Is there a technique known to define and work around a bad block of memory on the motherboard? It seems that the Windows operating systems should be able to work around the bad memory; words, detect the memory parity error, determine a range memory declare unusable, and continue the normal boot process.

It's EXPENSIVE to replace a motherboard just because of a parity error. I guess the memory on the motherboard is NOT REMPLACABLE. If the parity memory error is on a replaceable card, then replace the memory card is an acceptable expense.

Any suggestions other than to buy a new computer or replace the motherboard?

Don

Hello

Did you change your computer?

I suggest you to follow the links and check out them.

Method 1:

How to fix BlueScreen (STOP) errors that cause Windows Vista to shut down or restart unexpectedly

http://support.Microsoft.com/kb/958233

Method 2:

How will I know if my computer has a memory problem?

http://Windows.Microsoft.com/en-us/Windows-Vista/how-do-I-know-if-my-computer-has-a-memory-problem

-

'low memory - close applications' error messages

I have 8 GB of RAM and that you have not added all the apps on my work habits, but very recently, I get 'not enough memory - close applications' error messages. It seems that something is using a lot of RAM. How can I fix it?

I have been using RAMMap for a different problem, but it might work for you.

Download and install and create a shortcut on your desktop for RAMMap and / or PIN to the taskbar. When you sense the system becomes unresponsive, use Ctrl + Shift + Esc to access the Task Manager. Click the performance tab and the resource monitor button. Click the memory tab and check if free is close to zero, or is equal to zero. If it is, open RAMMap, click on empty on the menu bar and the empty queue. This action restores instantly free memory.

-

Error memory during the conversion of the .fmb to .fmt

Hi all

When I tried to convert a file (text format) .fmt file Unix .fmb its me gives error memory.

Command I use is

f60gen module = INTG_TEST.fmb userid=apps/xxxxxx@DB1 forms_doc = Yes = yes batch

Where from the constructor of the form I can do without any error of Administration-> Convert->

Can you get it someone please let me know?

Thank you

DevSorry... should be script = yes

Parse = yes is the opposite.

-

Hello

I am new to first pro cs4 sdk. I give the following error during build of SDK_Custom_Importpipl & SDK_Custom_Import.cpp

3 error LNK1104: cannot open file 'C:\Program Files\Adobe\Adobe first Pro CS4\Plug-ins\Common\\CustomImporterSDK.prm"E:\snehal\Premiere Pro CS4 SDK Win\Projects\SDK_Custom_Import\LINK SDK_Custom_Import r1

What is the right solution for this problem

Please help me!

Make sure that this .prm file is not used by another application. For example, you might have Preimere Pro running that this plugin was loaded and that when you try to rebuild the plugin, VS is probably to remove the old .prm file and write a new. Well, it cannot, since it is in use.

-

An error not handled during construction or the app runnning a Cordova/PhoneGap BB10

I'm trying to implement a project of 10 BlackBerry with Cordova/PhoneGap 3.0.0.

It took me a long time to understand the Platform for BlackBerry 10 guide actually refers to the version available on http://cordova.apache.org/ and must be installed noted differently on the first page of the site Web PhoneGap.

I have successfully created a project and added my Z10 camera as target.

However, when you try to run 'build debug z10' or "run z10" I always get the following error message:

events.js:72 throw er; // Unhandled 'error' event Error: spawn ENOENT at errnoException (child_process.js:980:11) at Process.ChildProcess._handle.onexit (child_process.js:771:34)

Any solution to this?

We've tracked down the cause of this error to the tools BlackBerry NDK is missing from the system path.

After you have installed the BlackBerry native SDK, tools must be added to your system path. Manually add the bin directory to your path, or run the following scripts in the directory where you installed the NDK:

Windows

bbndk - env.bat

Linux/Mac

source bbndk - env.sh

Note: the script execution will only add tools to your path for the current shell. If they persist, you must add the path to the bin directory using the Windows or Linux/Mac bash profile environment settings.

-

Error during construction through ripple for Blackberry Playbook, with WebWorks-Tablet

Hello

I am currently working on a blackberry app coded in HTML5.

I am looking to build for the playbook, following the instructions

However, when building it, I get the following error message

The first error message is caused by error when loading "jvm.dll" However, I checked, and this file exist in this directory.

Any help or sugestion would be greatly appreciated!

Thank you.

You must use JDK 6, and it must be 32-bit. I use the 32-bit JDK 6u45.

-

Disable the extended FIFO FPGA target during execution

Hello

I use a FIFO extended target in my FPGA to constantly calculate the derivative of a measured value (dB/dt). Thus the FIFO stores all values during time dt. This means dt determines the number of items in the FIFO and dB is determined by the actual value less the oldest value in the FIFO. It works well when I initialize with the code in figure InitFIFO.

But the FIFO of compensation is not possible (see figure clearFIFO). In the while loop if "reset dB" is false, as the new value of B is written on the FIFO, then the oldest value is read from, for the number of items in the FIFO remain constant. To change dt during execution, I need to clear the FIFO and initialize it with a new length (number of items). I tried the next loop, but it does not work. The FIFO does not initilized with the elements. The length is zero and the loop counter for (#deltaB Length2) is 0.

What I am doing wrong? Is there a better way to erase a FIFO during execution in the FPGA? I'm now stuck for 2 days with this problem and looking forward to any idea or suggestion.

Thank you very much. Best regards

Andy

Hej,

Thank you for your response. You were correct, that deltab FIFO length was 0 because the defalt value was zero. The problem is that in my host vi on the RT system I put DeltaB FIFO length in a loop of high priority and as you can see when I restart the FPGA, DeltaB FIFO length has a valid value (the code in figure 1 works well with a local variable of DeltaB FIFO length in the FPGA). But the variable to set the variable "reset dB" is under the control of the loop of low priority of the host vi. And there, I had an entry DeltaB FIFO length unwired.

So, I learned that a control FPGA read/write unwired sends a '0' or resets the variable to its default value in the FPGA. I assumed that nothing is transferred and the last variable is retained if you let a control read/write unwired. Now, I learned of this stupid error!

Thanks a lot again!

Andy

-

BIOS reports that node NUMBER 1 has no memory during installation VMVisor - 4.1 on ASUS KGPE-D16

Hello

I try to install vSphere Hypervisor (ESXi) 4.1 on a newly built server and during the installation process, I get the following error message:

The BIOS reports that node NUMBER 1 has no memory. This problem is caused by either a bad BIOS or a very skewed distribution of modules of memory.

Here's my server details

Motherboard - ASUS KGPE-D14 socket 34

Processor: AMD Opteron 6128, 2 GHz

Memory - Kingston 2 X 4 GB

Currently I use a single processor and 8 GB of memory (4 GB each two locations) and do not install another CPU or add additional memory to the same problem of NUMA. I went through all the articles from vmware regarding this issue and there is no luck so far. Please help me how I can solve this problem and get further.

Thank you

Praveen

You have the RAM installed in what locations? If you use a CPU, I think that you need a stick in the first slot of orange, ignore the following location Orange and install the second stick in the third slot orange.

-

Portege 3500 modules - 512MB memory lead to error

Hallo,

I tried to upgrade the memory in my P3500.

There are currently 1 256 MB module installed in the slot under the keyboard.I bought 2 x 512 MB PC133 SO-DIMM ram modules, but both lead to errors / beeps from the BIOS. I tried different combinations:

keyboard-slot: 512

the location of the bottom: vacuum

--> long shortkeyboard-slot: vacuum

the location of the bottom: 512

--> long short shortkeyboard-slot: 512

the location of the bottom: 256

--> long shortkeyboard-slot: 256

the location of the bottom: 512

--> long short shortkeyboard-slot: 512

the location of the bottom: 512

--> long short (pause) long short shortIt sounds like the bios refuses the 512 MB modules

I guess what the beeps mean:

long short - refusal of keyboard-ram slot

long short short - refusal of low-ram slotbut according to the manual, it should be possible to install 1 or 2 modules of 512 MB. What I am doing wrong?

Do I need a BIOS update? (currently installed: "ACPI BIOS 1.20")If a new BIOS only supports 512 MB modules - is there a possibility to upgrade the bios from unix?

(the only download BIOS I found on the support pages unfortunately just Toshiba works for windows)Help would be very appreciated...

Yes, you can improve your 3500 up to 1024 MB of memory (2 x 512 MB), but only with the right modules

You need * 16 x 32 (16 chip architecture) * PC133, 3, 3v sdram modules (144 pin so-dimm)I'm afraid that your 512 MB modules are not compatible :-(you can count the chips on the module, there should be 8 chips on both sides of the module

-

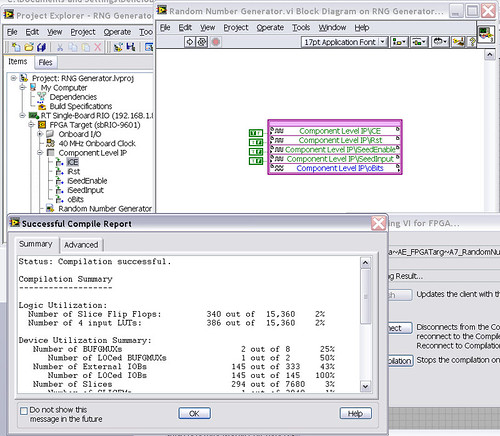

LabVIEW FPGA CLIP node compilation error

Hello NO,.

I work on an application for my Single-Board RIO (sbRIO-9601) and faced with a compile error when I try to compile my FPGA personality via the ELEMENT node. I have two .vhd files that I declare in my .xml file and all at this point works great. I add the IP-level component to my project and then drag it to the VI I created under my FPGA.

Within the FPGA personality, I essentially have to add some constants on the indicators and entries CLIP to my CLIP out and attempt to save/compile. With this simple configuration, I met a compilation error (ERROR: MapLib:820 - symbol LUT4... see report filling for details on which signals were cut). If I go back to my VI and delete indicators on the output (making the output pin of the CLIP connected to nothing), compiles fine.

I've included screenshots, VHDL and LV project files. What could be causing an indicator of the output of my VI to force compilation errors?

Otherwise that it is attached to the output ELEMENT, a successful compilation...

After that the output indicator comes with CLIP, compilation to fail...

NEITHER sbRIO-9601

LabVIEW 8.6.0

LabVIEW FPGA

Windows XP (32-bit, English)

No conflicting background process (not Google desktop, etc.).Usually a "trimming" error gives to think that there are a few missing IP. Often, a CLIP source file is missing or the path specified in the XML file is incorrect.

In your case I believe that there is an error in the XML declaration:

1.0

RandomNumberGenerator

urng_n11213_w36dp_t4_p89.vhd

fifo2.vhd

This indicates LV FPGA to expect a higher level entity called "RandomNumberGenerator" defined in one of two VHDL files. However, I couldn't see this entity in one of two files. If urng_n11213_w36dp_t4_p89 is the top-level entity, edit the XML to instead set the HDLName tag as follows:

urng_n11213_w36dp_t4_p89 Also - in your XML, you set the 'oBits' music VIDEO for output as a U32, however the VHDL port is defined as a vector of bits 89:

oBits: out std_logic_vector (89-1 downto 0)

These definitions must match and the maximum size of the vector CLIP IO is 32, so you have to break your oBits in three exits U32 output. I have added the ports and changed your logic of assignment as follows:

oBits1(31 downto 0)<= srcs(31="" downto="">

oBits2(31 downto 0)<= srcs(63="" downto="">

oBits3(31 downto 0)<= "0000000"="" &="" srcs(88="" downto="">Both of these changes resulted in a successful compilation.

Note: The only compiler errors when you add the flag because otherwise your CUTTING code is optimized design. If the IP is instantiated in a design, but nothing is connected to its output, it consumes all logic? Most of the time the FPGA compiler is smart enough to get it out.

Maybe you are looking for

-

Difference between mail header in the list and the detail window

Sometimes after receiving multiple emails at the same time and I want to watch a mail by clicking on the object in the list, another mail opens in the mail window, and everything that I've done (by removing the other mail, returned mail...) I'm not a

-

When I was cleared a paper inside my HP Office Jet 6500 E709n jam, I somehow now have a disconnected plastic Ribbon that I need to reconnect. I can't find a diagram inside my printer or instructions on how and where to reconnect this Ribbon plastic.

-

Why Express PSD gives a different result of amplitude as FFT PSD?

Hello When I use the express VI of spectral measures to trace the power spectral density, I get a different result than when using the FFT PSD VI. The data are the same but the amplitudes are different in the PSD plot. Everyone comes through this? Th

-

Enlarge/reduce the image for print on HPC309A

How to enlarge or reduce the size of the image when copying on the HPC309A? Thanks for your help, TEHACHAP

-

Hi allI'm exploring OBIEE use Tracking report and wanted to verify a few things.There is a report that gives just 1 form and for most of the user the i.e.Total dry time execution time report shows 1-2 seconds.However, I also see an entry for some use