LabVIEW fpga compile: translation error then again translate

Hello everyone,

I have a question about the process of compiling LV FPGA.

The context:

I am compiling a binary FPGA for the NOR-5644R (viterx6 inisde). the process is quite long (up to 7 hours depending on how is our CLIP). I am canvassing any idea of attaching the compilation process.

The fact:

By analyzing the log file of the previous compilation, I noticed that the stage translate is made twice, probably because one is a failure. the excerpt from log files are copy/paste below.

Further, it seems the errors (at least some of them) translate the first are induced by the commented lines of NOR provided file UCF (RfRioFpga.ucf)

The question:

Why to translate step to do it twice (the first being failed)? would it not quicker to make only the second succefull one? in other words, it is really necessary for the first fails to translate step for the FPGA binay?

Any ideas?

Thanks in advance!

See you soon,.

Patrice

----

log file extract 1:

"...

NGDBUILD Design summary of results:

Error number: 387

Number of warnings: 1443

Total in time REAL until the end of the NGDBUILD: 2 h 16 min 45 s

Time CPU until total NGDBUILD: 2 h 11 min 21 sec

One or more errors were found during the NGDBUILD. No file NGD will be written.

Writing the file of log NGDBUILD 'RfRioFpga.bld '...

'Translate' process failed

..."

log file excerpt 2:

"...

NGDBUILD Design summary of results:

Number of errors: 0

Number of warnings: 818

Writing the file 'RfRioFpga.ngd '... NGD

Total in time REAL until the end of the NGDBUILD: 29 min 17sec

Time CPU until total NGDBUILD: 27 min 33sec

Writing the file of log NGDBUILD 'RfRioFpga.bld '...

NGDBUILD done.

'Translate' process completed successfully

..."

Hi Patrice,

It seems strange that it performs this step two times (and was worried when I saw the first time), but there is good reason for that, certainly. LabVIEW inserts constraints for components, he adds, but sometimes the components get optimized out by the compiler. When the compiler encounters stressed that points to the now non-existent component, it error. LabVIEW circumvents this by running the process to translate two times. The first time, it may fail. LabVIEW will remove the constraints that fail, then run again translate it. Unfortunately there is no way around this problem.

Tags: NI Software

Similar Questions

-

stuck FPGA compilation, no errors

Hello

I wrote a LabVIEW FPGA 8.6.1 program (I have written several, this is my most recent). When I run it on the development computer it seems to work fine without any errors. When I try to compile, however, it still stalls on this part:

'Analysis of generic entity

library ( Architecture). This isn't feeze (the compiler is always updated time and you can see it working). It just doesn't progress no further than this point. By chance, does anyone know what could cause this? I know that maybe it's a little vague, sorry. Thank you!

Nevermind, I figured it. I had a knot of analog input within a For loop. This wire entry (i.e. given out the analog input node) was connected to a tunnel auto-index on the loop For I have just disabled automatic indexing on this tunnel and everything seems to compile fine now.

-

LabVIEW FPGA: Compilation failed due to an error of xilinx

I'm getting a 'Compilation failed due to the error of Xilinx' you try to compile the code in LabVIEW 2013.The code has successfully compilated in labview2012. Any suggestions on what is causing this problem?

Details:

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\THY4t7n_z6im2K7\NiFpgaAG_0000003a_SequenceFrame.vhd" line 29: Formalhas no real or default value.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\THY4t7n_z6im2K7\NiFpgaSetOutputDataEnable.vhd", line 37. cparametersignal is declared here

ERROR: HDLCompiler:854 - "C:\NIFPGA\jobs\THY4t7n_z6im2K7\NiFpgaAG_0000003a_SequenceFrame.vhd" line 21:Unit ignored due to previous errors.

File VHDL C:\NIFPGA\jobs\THY4t7n_z6im2K7\NiFpgaAG_0000003a_SequenceFrame.vhd ignored errors

-->Total memory use is 204688 kilobytes

Number of errors: 2 (filtered 0)

Number of warnings: 4 (filtered 0)

Number of news: 0 (0 filtered)"Synthesize - XST" process failed

Compile time

---------------------------

Introduction date: 2014/2/26 18:15

Date recovered results: 2014/2/26 18:17

Waiting time in the queue: 00:06

Compilation of time: 02:02

-PlanAhead: 01:16

-Generator kernel: 00:00

-Synthesis - Xst: 00:35Hi guys

I think I can give you a helping hand on this.

I have the same problem when I'm working on the Tutorial (2013) exercise 2 with Rio evaluation Kit.

You can try one of the following option.

Solution 1.

1. in the VI package manager.

Select 'Tools '->' Options'-> "General '->' package Installation"-> Unchecked 'mass Compile screws after Installation of the package.

Solution 2

1. in the VI package manager, uninstall the driver LCD

2. unchecked "Mass compile screws after Installation of the package" (see Solution 1)

3 reinstall the driver of the LCD screen.

Mine did after Solution 2 and the compiler works.

Hope it will be useful for you guys.

Thank you

-

LabVIEW FPGA compile Cloud Computing Service stuck on the production of carrots

Hello

Since I was on windows 8 I do use cloud server compile compile my screws

However, lately he has been slain a lot during production of carrots.

Is that what I can do to get rid of this problem? Sometimes it just doenst seem to compile at all but sometimes it compiles. It's embarrassing because I rely on this service.

Any advice?

How long compiling stuck there? If your application requires a number of hearts, it can take a long time to generate all the necessary support files. For some large FPGA, this party may take several hours the first time you hit a new compilation/instance machine. Fortunately, the carrots are cached, so maybe why it is sometimes faster, depends on which machines your compilation is striking.

-

tables of fixed size in FPGA compilation error - how to implement a waveform control in an FPGA?

Hello

After being stuck for two days, please let me briefly describe my project and the problem:

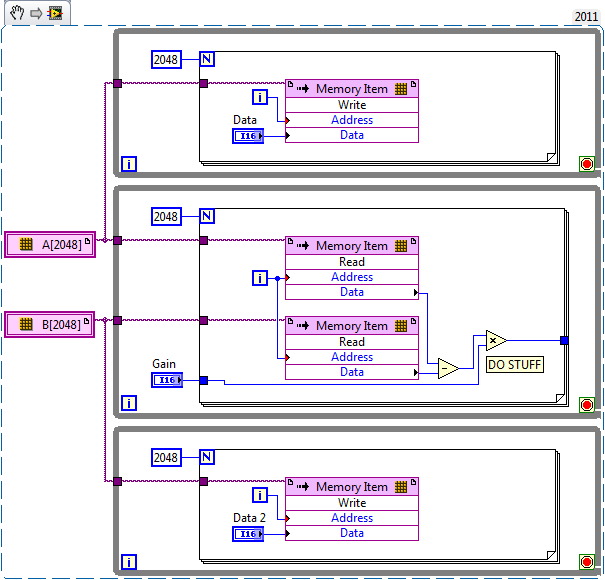

I want to use the cRIO FPGA for iterative control of waveforms. I want to capture a full period of the waveform, subtracting a reference waveform period and apply control algorithms on this. Subsequently the new period of correction must be sent again for the output module OR. If it does not work, the captured waveform will look like the one reference after several iterations.

I am planing to create an array of size fixed for the capture and the reference waveform (each around 2,000 items for a given period). I use so 2 paintings of each elements of 2000. I use the function 'replace the subset of table' to update each element captured in the loop sampling and a feedback for each table node to keep in memory (I also tried shift registers, but then the berries do not have a fixed size any more and I can't start the compilation process).

If I try to compile the FPGA vi, I get the following error:

Details:

ERROR ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

"Synthesize - XST" process failedBefore I added berries to my code I could compile the FPGA without problems. So, it seems that the tables are too big for the FPGA. :-(

Therefore, I would like to ask if there is perhaps a better method to implement my problem in LabVIEW FPGA? How could avoid the tables to save my waveforms on a period?

Thanks a lot for your help in advance.

Best regards

Andreas

Unfortunately, the LabVIEW FPGA compiler cannot deduct stores shipped from berries (yet). When you create these two large paintings, you are creating essentially several registers very, very large. Just by looking at your picture, I guess that there are at least 4 copies of each of the tables.

You want to use LabVIEW FPGA memories instead. You can create memories outside the loop and then read/write them where you are currently referencing the berries. The only change that you really need to do is to break down your treatment in scalar operations. I have attached a simplified version of your plan, I hope it helps. Let us know if you have any other questions.

-

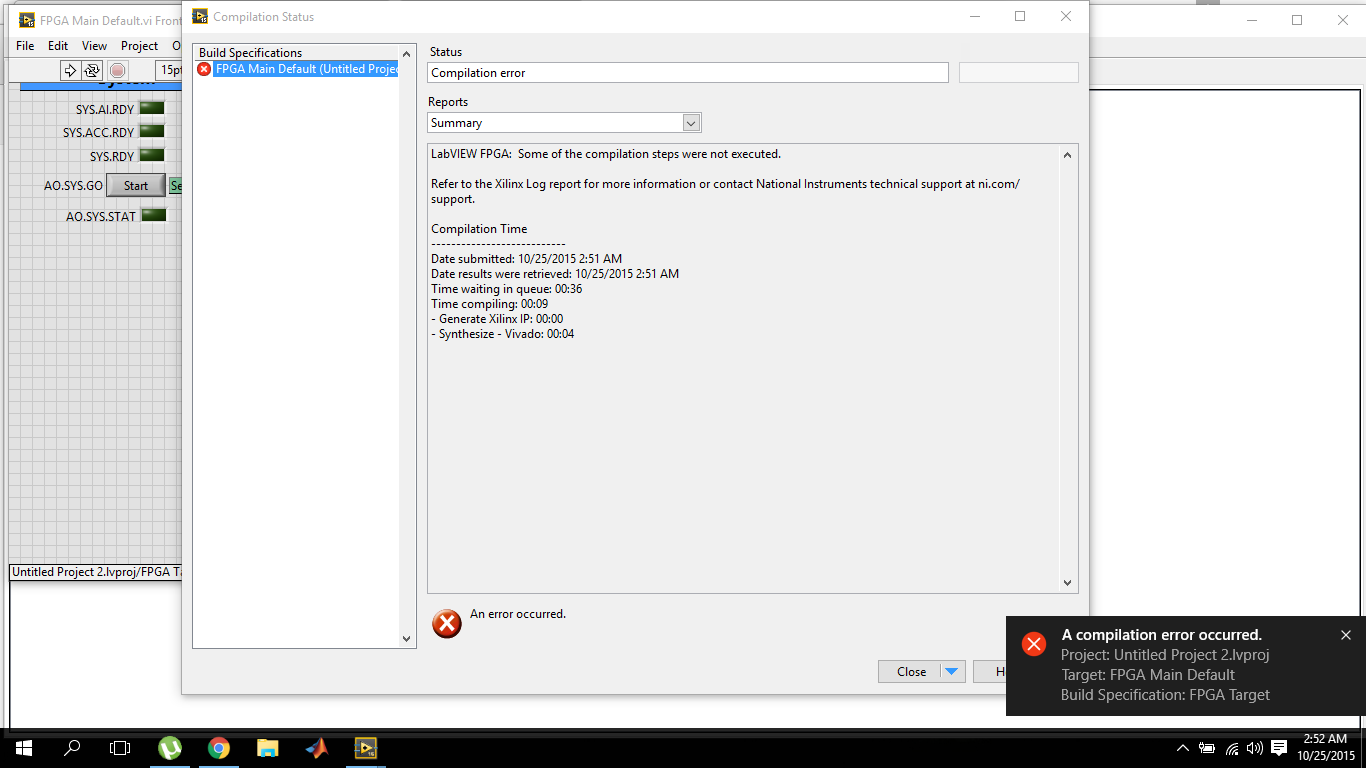

FPGA Compilation fails because of the mistake of Xilinx

My FPGA compiles and I cannot understand why. There is nothing crazy in my FPGA VI of really, it seems strange to have this type of problem. I can't reach the code because its owner, but it's pretty simple because it reads all channels from a single module and records them in a data FIFO. I have compiled successfully any FPGA code on this computer, so I should definitely have everything needed to compile.

My system consists of one NOR cRIO 9030 with a single module 9220. Below is the Compilation of summaries.

---

LabVIEW FPGA: Compilation failed due to an error of Xilinx.

Details:

ERROR: [Synth 8-1031] knidmahighspeedsinkbase is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:295]

ERROR: [Synth 8-1031] knidmahighspeedsinksize is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:296]

ERROR: [Synth 8-1031] knidmahighspeedsinkbase is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:301]

ERROR: [Synth 8-1031] knidmahighspeedsinkbase is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:302]

INFO: [Synth 8-2810] pkgshimswitchedlinkdmaportifc unit ignored due to previous errors [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:68]

---------------------------------------------------------------------------------

Development of finished RTL: time (s): UC = 00:00:07. delay = 00:00:31. Memory (MB): peak = 798.605; gain = 204.203

---------------------------------------------------------------------------------

ERROR: [Common 17-39] 'source' is not due to previous errors.

INFO: [Common 17-83] release license: synthesis

3 info, 0 Warnings, 0 critical warnings and 4 errors.

synth_design failed

: ERROR: [Common 17-39] 'source' is not due to previous errors.When running

«source - notrace.» /. Xil/Vivado-6035-ip-10-60-203-176/realtime/toplevel_gen.tcl ".

called inside

«synth_design-top "toplevel_gen" - part "xc7k70tfbg676-1"-"full" flatten_hierarchy "»»

(file "/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/synthesize.tcl" line 21)

called inside

"source" / opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/synthesize.tcl "" "

exit #.

INFO: [Common 17-206] exit Vivado at Tue Mar 24 23:58:54 2015...Compile time

---------------------------

Introduction date: 24/03/2015-16:46

Date recovered results: 24/03/2015-17:00

Waiting time in the queue: 00:24

Compilation of time: 13:22

-Generate a Xilinx IP: 00:00

-Summarize - Vivado: 01:27Compilation has restarted on

24/03/2015-16:57---

Any help would be much appreciated!

Thank you

James.Morris wrote:

Okay, so it seems that I get the error with a project from scratch and an FPGA with a single command and an indicator.

I download the latest FPGA 2014 SP1 installation and I hope that will solve my problem.

Well I'll mend, which fixed the problem! Somewhere along the line, my install FPGA must be corrupted.

Thanks for the help, guys.

-

decriptare codice vhdl generato da labview FPGA

Salve,

Quello che sto cercando di rates e di open a file vhd generato da labview FPGA during the United Nations VI, per vedere come viene scritto codice di compilaizione of it. Questo pole mi'd of poterlo confrontare con UN identico codice scritto directly in vhdl...

Salve,

non e possibile access al codice vhdl generato da LabVIEW FPGA compile durante.

LabVIEW e stato been proprio per evitare di codice vhdl texts scrittura/analysis.

-

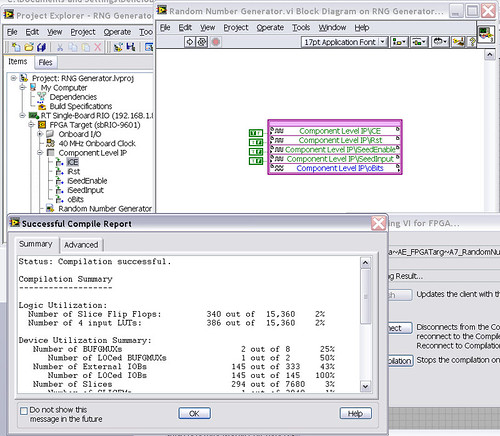

LabVIEW FPGA CLIP node compilation error

Hello NO,.

I work on an application for my Single-Board RIO (sbRIO-9601) and faced with a compile error when I try to compile my FPGA personality via the ELEMENT node. I have two .vhd files that I declare in my .xml file and all at this point works great. I add the IP-level component to my project and then drag it to the VI I created under my FPGA.

Within the FPGA personality, I essentially have to add some constants on the indicators and entries CLIP to my CLIP out and attempt to save/compile. With this simple configuration, I met a compilation error (ERROR: MapLib:820 - symbol LUT4... see report filling for details on which signals were cut). If I go back to my VI and delete indicators on the output (making the output pin of the CLIP connected to nothing), compiles fine.

I've included screenshots, VHDL and LV project files. What could be causing an indicator of the output of my VI to force compilation errors?

Otherwise that it is attached to the output ELEMENT, a successful compilation...

After that the output indicator comes with CLIP, compilation to fail...

NEITHER sbRIO-9601

LabVIEW 8.6.0

LabVIEW FPGA

Windows XP (32-bit, English)

No conflicting background process (not Google desktop, etc.).Usually a "trimming" error gives to think that there are a few missing IP. Often, a CLIP source file is missing or the path specified in the XML file is incorrect.

In your case I believe that there is an error in the XML declaration:

1.0

RandomNumberGenerator

urng_n11213_w36dp_t4_p89.vhd

fifo2.vhd

This indicates LV FPGA to expect a higher level entity called "RandomNumberGenerator" defined in one of two VHDL files. However, I couldn't see this entity in one of two files. If urng_n11213_w36dp_t4_p89 is the top-level entity, edit the XML to instead set the HDLName tag as follows:

urng_n11213_w36dp_t4_p89 Also - in your XML, you set the 'oBits' music VIDEO for output as a U32, however the VHDL port is defined as a vector of bits 89:

oBits: out std_logic_vector (89-1 downto 0)

These definitions must match and the maximum size of the vector CLIP IO is 32, so you have to break your oBits in three exits U32 output. I have added the ports and changed your logic of assignment as follows:

oBits1(31 downto 0)<= srcs(31="" downto="">

oBits2(31 downto 0)<= srcs(63="" downto="">

oBits3(31 downto 0)<= "0000000"="" &="" srcs(88="" downto="">Both of these changes resulted in a successful compilation.

Note: The only compiler errors when you add the flag because otherwise your CUTTING code is optimized design. If the IP is instantiated in a design, but nothing is connected to its output, it consumes all logic? Most of the time the FPGA compiler is smart enough to get it out.

-

Please help me for this problem "error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

Look for the error on the Web site of or or on the forums. Take a look at the following links:

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=381394&requireLogin=false

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=205754&requireLogin=false

-

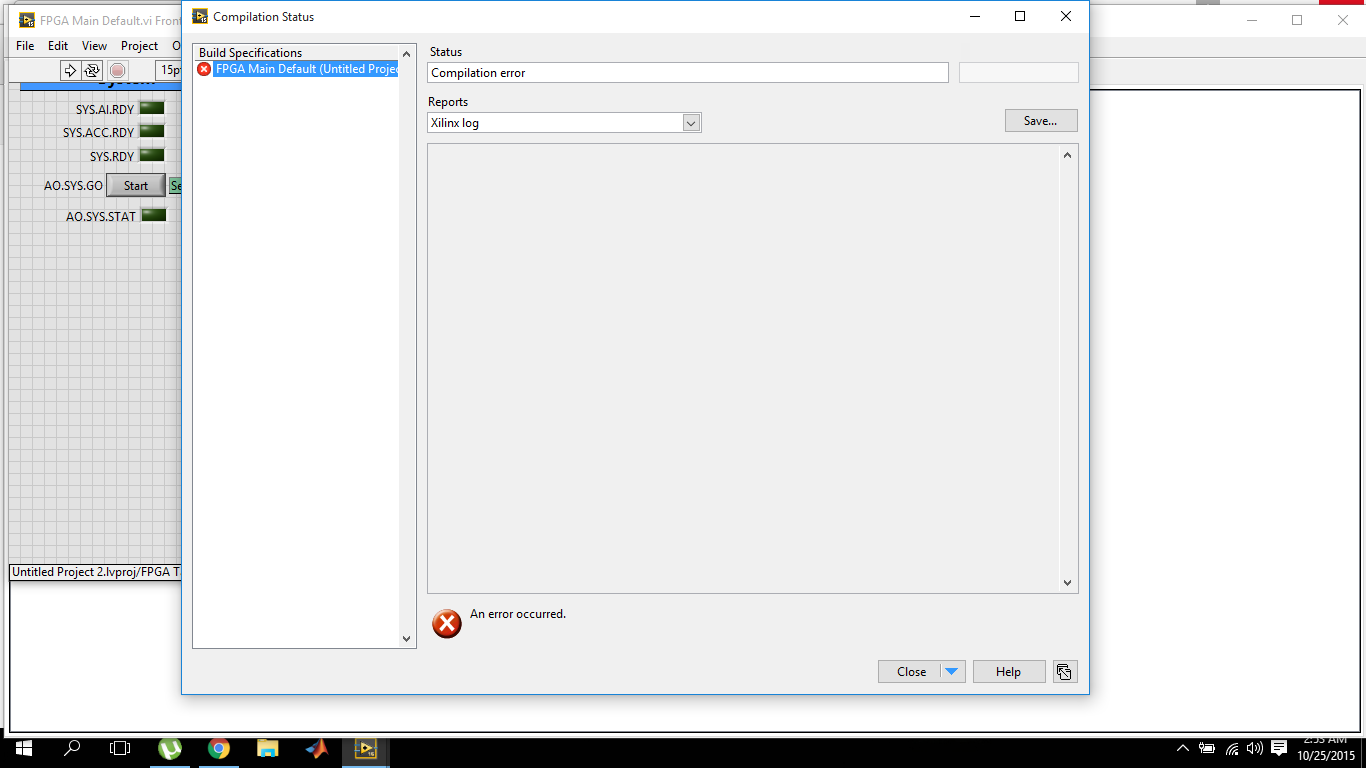

LabVIEW FPGA, 2015 compilation error

I've recently switched to LabVIEW 2015 and I'm working on OR myRIO. So also installed myRIO 2015 bundled software. The problem I have is that the compilation of fpga fails within 10 seconds.

and the target Xilinx journal report is empty

The first time when I tried to compile on 2015 version, it failed and the message box that failed came alongwith the avast antivirus warning for malicious activity. I reported it as wrong and now I tried several times with avast shield disabled control, but the results are the same. While the version of labVIEW 2014 works very well.

Now, I'm sure that there is something wrong with the installation of Vivado because this dll is part of it. The dll must be default in the2014_4\lib\win32.o directory C:\NIFPGA\programs\Vivado if you are using an operating system for 32-bit AND also in C:\NIFPGA\programs\Vivado2014_4\lib\win64.o If you use a 64-bit operating system. If the dll is not here, it is probably that the anti virus (I've never seen what happens to Xilinx but I have for other stuff).

I'm emphasizing the 2014_4 because LabVIEW 2015 uses Vivado 2014_4 while 2014 LabVIEW uses Vivado 2013_4. Since you have also installed LabVIEW 2014, you must have 2013_4 as well and if it works, you will find the dll I just wanted you make sure you check the correct directory for the Vivado 2014_4.

Download and install (reinstall or repair if already installed) 2015 LabVIEW FPGA Module Xilinx tools Vivado 2014.4. You can also use the DVD Setup if you have. It would be a good idea to do the installation with the disabled and even anti-virus try the first compilation the same. Try and let me know if the problem persists.

Kind regards

-

LabVIEW FPGA: Problem compiling look-up Table

Current versions of software:

LabVIEW 2014 SP1

LabVIEW FPGA 2014

Xilinx Vivado

I'm having a huge problem in trying to compile my LabVIEW FPGA code.

Some recall of the code:

It's all in a SCTL.

I am streaming in a FIFO DMA and comparing it with the values previously stored in the shift registers (which are initialized to 0 at the start of the loop) in the SCTL.

The results of the comparison are then piled into a U16 and loaded into a lookup table (I use the LUT - 1 d), and I'm so help this LUT to decide what value will be charged to travel to record for the next iteration of the loop, which, in any case, would be either the current values of the flow, or the post previous registry value.

(It's a triage loop)

I am able to run very well in simulation mode code, but when I try to compile, I get this error:

"The selected object has a built-in shift register that makes the output on a particular loop iteration correspond to the entries in the previous iteration."

Connect the outputs of the object directly to a minimum number of nodes of Feedback or uninitialized shift registers. You cannot connect the outputs to another object.

See using LabVIEW for more information on the objects with registers embedded offset. »

Someone at - it ideas why this happens, and what might be the possible solutions?

I'm tempted to break it down into separate loops, but I prefer not to because it is now a loop (and working in my simulation).

I found my problem.

Any time that a LUT is in a chain shift register, it cannot:

1. be part of a string of shift register that has a variable initialized

2. follow-up to no decisive structure, like a box structure.

I just moved the position of LUT and it works.

-

Violation of compilation-Timing error FPGA

Hi all

I've been LV around for years, but I am a complete newbie when it comes to FPGA. I'm working on programming for a 9651 (SOM) using the Dev kit. I'm starting by small steps, but already tripped. I have a simple VI which retrieves a value from a FIFO and passes it réécrirait a different FIFO. When compiling, it gives an error of timing violation, and I don't know how to study. The VI is attached.

If background for the curious... I'm working on the side of our application to signal processing. I'm passing data from a prerecorded TDMS file to a FIFO. I want to send the FPGA, treat it and send it back. Eventually, it will come of I/O, but for now, I just want to work on the processing of the signal. Before starting work, I thought I'd just make sure I can transfer data to the bottom and back. Once I get this job, I'll start to developing processing screw for between the two.

Thank you!

Hi thutch79,

You can specify the version of LabVIEW you use and implementing CLIP half bridge that you use for the IO DevKit?

It was a timing violation introduced between LabVIEW 2014 and 2015, given the way the compiler Xilinx handled VHDL which takes in charge the second port Ethernet on SOM. If you use a CLIP half bridge that has been generated before 2015 LabVIEW (as the example of the expedition which I think begins with a CLIP called "DevKit"), then you can get a timing error. There should be a second sample CLIP called DevKit2, I think, which was regenerated with compatibility for 2015 of LabVIEW and later versions.

This problem has been discussed here: https://decibel.ni.com/content/thread/42711

You can check your half-bridge CLIP in the project by ensuring that you have selected the version called DevKit2 if you have a version of LabVIEW FPGA which is 2015 or newer.

Kind regards

-

LabVIEW FPGA error - Urgent please

Hello

I had this problem for a while and it drives me crazy. When I try to program my 3rd Spartan fpga Board, I get a message, it compiles successfully. Then, I get an error indicating that

"Labview called another component of software and that componen returned ther following error:

Error code = - 2147483648

2147473648 error occurred at nilvcseInitChain.vi

This error is not defined. No one has provided a description for this code or you could have wired a number which is not an admission of error code error code. »

Help, please!

1. what version of LV run you, 8.5 or 8.6? What operating system do you use? XP, Vista (32/64-bit?)

2. go to the Device Manager (click right tab of my computer/hardware). You see a category called "Programming wires" and the Xilinx Board is listed under it?

Reid

-

FPGA compilation I get error & quot; ERROR: ConstraintSystem:58 & quot;

I use the Xilinx LogiCore IP generator for generating DSP IP for my FPGA.

The problem is that the names of the generated components are for a long time.

On the Web site or http://digital.ni.com/public.nsf/allkb/F810E4289A420FE68625796600764C66

He described a problem very similar to what I have ID issue 309260 "compilation error (ERROR: ConstraintSystem:58) when compiling a LabVIEW FPGA VI which contains a generated from a DSP graph VI.»

I followed the suggestions and changed my IP to names such as 'A' and 'B '. As a first step, that it did not work, only to spend the entire project to another shorter path of directory did this job.

Now, when I regenerate the IP address of 'Tools' > 'FPGA Modules' > "Regenerate the node IP" this will rename my IP with an additional random name at the end. So, if I look in my case not only that I have "A.vhd" but now, I'm also having 'A_F27AB4F7464E508DCCB219B2C4271B18.vhd '.

It's very repetitive, and you should be able to replicate that.

It's havoc with our software and with our software process control tool. Our database of software can accommodate only names of files of a certain length, and this violates. Also, I now have files with the exact same content but with different names.

Do you have a fix for this problem as stated on your website?

Kind regards

I ended up using LogiCore externally. If you do a search in your LabVIEW FPGA tools folder, you should find "\Xilinx12_4\ISE\bin\nt\coregen.exe" (in the case of the specific version of Xilinx tools you have), it's the Xilinx Logicore exe without the National Instruments candy wrapper.

I created all of my external LogicCore to LabVIEW (it actually makes life easer, the LogicCore tool has a better Manager to track all your IP LogicCore in any case) and then used the IP LabVIEW nodes to access the intellectual property.

This has prevented the long names, and now I can better handle the INVESTIGATION period because I can put the code in a folder I want without breaking of LabVIEW.

-good luck

-

Internal software error of LabVIEW FPGA Module - 61499

I get the error next (in a pop-up window) in the phase of sompilation for the FPGA target with a vhdl IP. This error continues to occur even after restart LabVIEW and the PC. Someone at - it solved is this kind of problem before without having to re - install the software?

Here is the error information:

Error-61499 occurred at niFpgaXml_GetValue_String.vi<><><><>

Possible reasons:

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has occurred. Please contact National Instruments technical support on ni.com/support.

Additional information: lack the tag required XML (/ CompileServerList)

As a first step, I can compile the vhdl IP node successfully. However, once when I'm running a VI with the FPGA, the bureau stop working. After that I restarted by force, it cannot perform the build of a vhdl IP node. Even without connecing to the jury of LabView, he pointed out errors before the end of the sompilation.

Interestingly, the screw which also includes nodes IP vhdl that I properly compiled before, I can still run the VI to the Commission and it works correctly.

Thank you

Looks like your ActiveJobsList somehow has been corrupted. I saw occur when computers are hard stop or blue screen during compilation. I don't have that LabVIEW 2014 installed on my machine, so your path will be a little different, and the file extension will be a .txt or .xml instead of .json, but try this:

Move the file "C:\Program Files (x 86) \National Instruments\LabVIEW 2014\vi.lib\rvi\CDR\niFpgaActiveJobList.json" (or your equivalent) out of the above directory (back it upward and delete essentially) and restart LabVIEW. Must regenerate the file and resolve the problem.

Maybe you are looking for

-

Financial software for IPad Pro

I currently use a Windows version of Quickbooks Pro 2014 in Boot Camp on my MacBook Pro for business and personal accounting. I would like to be able to access or even set up my personal accounts via IPad Pro accounting software and synchronization b

-

Satellite Pro 480CDT: Wave Device for Voice Modem

I reinstalled Windows 98SE on Satellite Pro 480CDT and it seems to work ok. But when I go into the Device Manager there is a yellow exclamation point in front of > Wave Device for Voice Modem Do I need to install a driver for it? Could you describe o

-

Hi all, I recently bought the laptop mentioned above, first thing I did was clean the hard drive and install a dual boot with windows and linux, linux works 99% in some small problems, but nothing serious. However, windows 7 is a different story, I s

-

Hi all I'm building a small DLL (for use from matlab) for acquisition of data. One of the functions may take several hours: streaming over 1 million samples in a file. So for this particular function, I want (read: I'm trying) to run it as a backgrou

-

OfficeJet Pro 8600 will not feed photo paper. post 'message of paper '.

I went through all the troubleshooting steps. Clean the roller, etc. the printer will be fine plain paper feeding, but not the photo paper. I use new paper, shiny and Matt brand HP. Suggestions? I n ' t had this printer a year yet, but it's out of wa