LabVIEW FPGA error - Urgent please

Hello

I had this problem for a while and it drives me crazy. When I try to program my 3rd Spartan fpga Board, I get a message, it compiles successfully. Then, I get an error indicating that

"Labview called another component of software and that componen returned ther following error:

Error code = - 2147483648

2147473648 error occurred at nilvcseInitChain.vi

This error is not defined. No one has provided a description for this code or you could have wired a number which is not an admission of error code error code. »

Help, please!

1. what version of LV run you, 8.5 or 8.6? What operating system do you use? XP, Vista (32/64-bit?)

2. go to the Device Manager (click right tab of my computer/hardware). You see a category called "Programming wires" and the Xilinx Board is listed under it?

Reid

Tags: NI Software

Similar Questions

-

Internal software error of LabVIEW FPGA Module - 61499

I get the error next (in a pop-up window) in the phase of sompilation for the FPGA target with a vhdl IP. This error continues to occur even after restart LabVIEW and the PC. Someone at - it solved is this kind of problem before without having to re - install the software?

Here is the error information:

Error-61499 occurred at niFpgaXml_GetValue_String.vi<><><><>

Possible reasons:

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has occurred. Please contact National Instruments technical support on ni.com/support.

Additional information: lack the tag required XML (/ CompileServerList)

As a first step, I can compile the vhdl IP node successfully. However, once when I'm running a VI with the FPGA, the bureau stop working. After that I restarted by force, it cannot perform the build of a vhdl IP node. Even without connecing to the jury of LabView, he pointed out errors before the end of the sompilation.

Interestingly, the screw which also includes nodes IP vhdl that I properly compiled before, I can still run the VI to the Commission and it works correctly.

Thank you

Looks like your ActiveJobsList somehow has been corrupted. I saw occur when computers are hard stop or blue screen during compilation. I don't have that LabVIEW 2014 installed on my machine, so your path will be a little different, and the file extension will be a .txt or .xml instead of .json, but try this:

Move the file "C:\Program Files (x 86) \National Instruments\LabVIEW 2014\vi.lib\rvi\CDR\niFpgaActiveJobList.json" (or your equivalent) out of the above directory (back it upward and delete essentially) and restart LabVIEW. Must regenerate the file and resolve the problem.

-

Error when create control LabVIEW FPGA CompactRIO

I have error when you try to create a new model of LabVIEW FPGA CompactRIO control project. I tried with LabVIEW 2014 and 2014 SP1 update. This error always occurs.

Please help me with this.

Kind regards

Thang Nguyen

Hello

I fix the problem by removing LabVIEW 2014 SP1 and reinstall again. After the reinstallation of LabVIEW, I create the project template.

Kind regards

-

Please help me for this problem "error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

Look for the error on the Web site of or or on the forums. Take a look at the following links:

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=381394&requireLogin=false

http://forums.NI.com/NI/board/message?board.ID=170&message.ID=205754&requireLogin=false

-

Please convert LabVIEW 2013 urgent please

Please convert LabVIEW 2013 urgent please

You can go there.

-

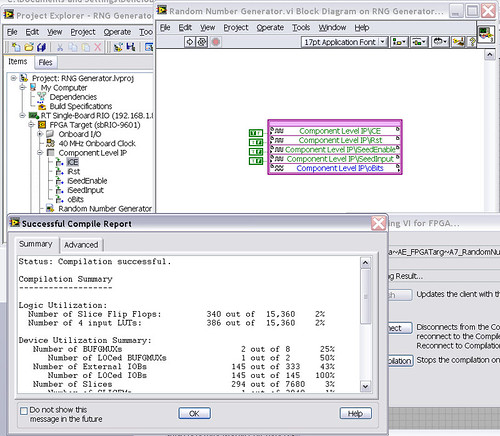

LabVIEW FPGA CLIP node compilation error

Hello NO,.

I work on an application for my Single-Board RIO (sbRIO-9601) and faced with a compile error when I try to compile my FPGA personality via the ELEMENT node. I have two .vhd files that I declare in my .xml file and all at this point works great. I add the IP-level component to my project and then drag it to the VI I created under my FPGA.

Within the FPGA personality, I essentially have to add some constants on the indicators and entries CLIP to my CLIP out and attempt to save/compile. With this simple configuration, I met a compilation error (ERROR: MapLib:820 - symbol LUT4... see report filling for details on which signals were cut). If I go back to my VI and delete indicators on the output (making the output pin of the CLIP connected to nothing), compiles fine.

I've included screenshots, VHDL and LV project files. What could be causing an indicator of the output of my VI to force compilation errors?

Otherwise that it is attached to the output ELEMENT, a successful compilation...

After that the output indicator comes with CLIP, compilation to fail...

NEITHER sbRIO-9601

LabVIEW 8.6.0

LabVIEW FPGA

Windows XP (32-bit, English)

No conflicting background process (not Google desktop, etc.).Usually a "trimming" error gives to think that there are a few missing IP. Often, a CLIP source file is missing or the path specified in the XML file is incorrect.

In your case I believe that there is an error in the XML declaration:

1.0

RandomNumberGenerator

urng_n11213_w36dp_t4_p89.vhd

fifo2.vhd

This indicates LV FPGA to expect a higher level entity called "RandomNumberGenerator" defined in one of two VHDL files. However, I couldn't see this entity in one of two files. If urng_n11213_w36dp_t4_p89 is the top-level entity, edit the XML to instead set the HDLName tag as follows:

urng_n11213_w36dp_t4_p89 Also - in your XML, you set the 'oBits' music VIDEO for output as a U32, however the VHDL port is defined as a vector of bits 89:

oBits: out std_logic_vector (89-1 downto 0)

These definitions must match and the maximum size of the vector CLIP IO is 32, so you have to break your oBits in three exits U32 output. I have added the ports and changed your logic of assignment as follows:

oBits1(31 downto 0)<= srcs(31="" downto="">

oBits2(31 downto 0)<= srcs(63="" downto="">

oBits3(31 downto 0)<= "0000000"="" &="" srcs(88="" downto="">Both of these changes resulted in a successful compilation.

Note: The only compiler errors when you add the flag because otherwise your CUTTING code is optimized design. If the IP is instantiated in a design, but nothing is connected to its output, it consumes all logic? Most of the time the FPGA compiler is smart enough to get it out.

-

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has Unknown

Sir/Madam,

Note Labview 2012 SP1 installed about 2 weeks ago.,.

Accident occurred during the compilation of an fpga vi who worked satisfactorally in the past.

When I restarted and went to the message recomplile "LabVIEW FPGA: an internal software error in the LabVIEW FPGA Module" see attached picture of popup.

I reinstalled Labview in its entirety and backed out the changes I made to the vi but still get the same message.

Thanks in advance

Daryl

It turns out that the question was in the VI and not of LabView FPGA module as the message may indicate. I created a vacuum vi, cut and pasted items in this from the vi error and recompiled and it ran very well.

Somehow the vi has been corrupted internally.

Thank you it's fixed.

-

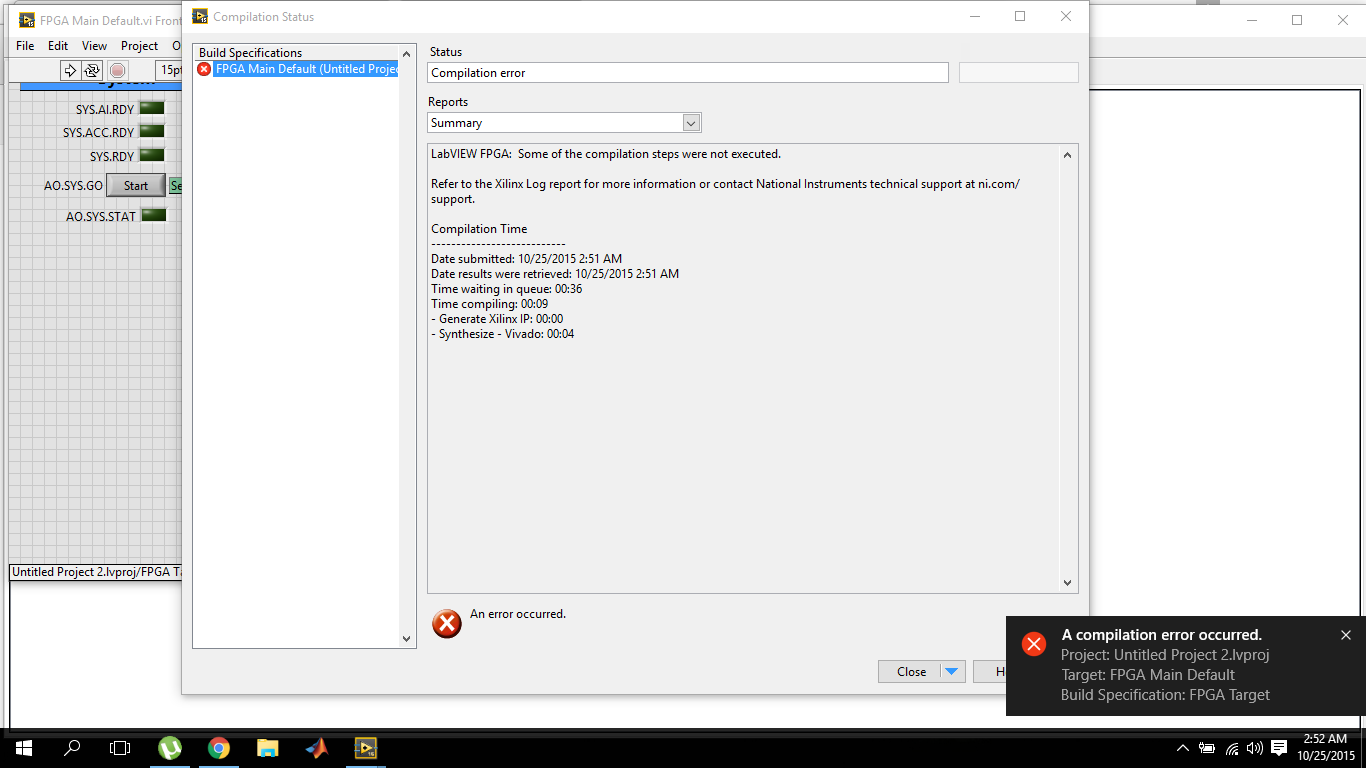

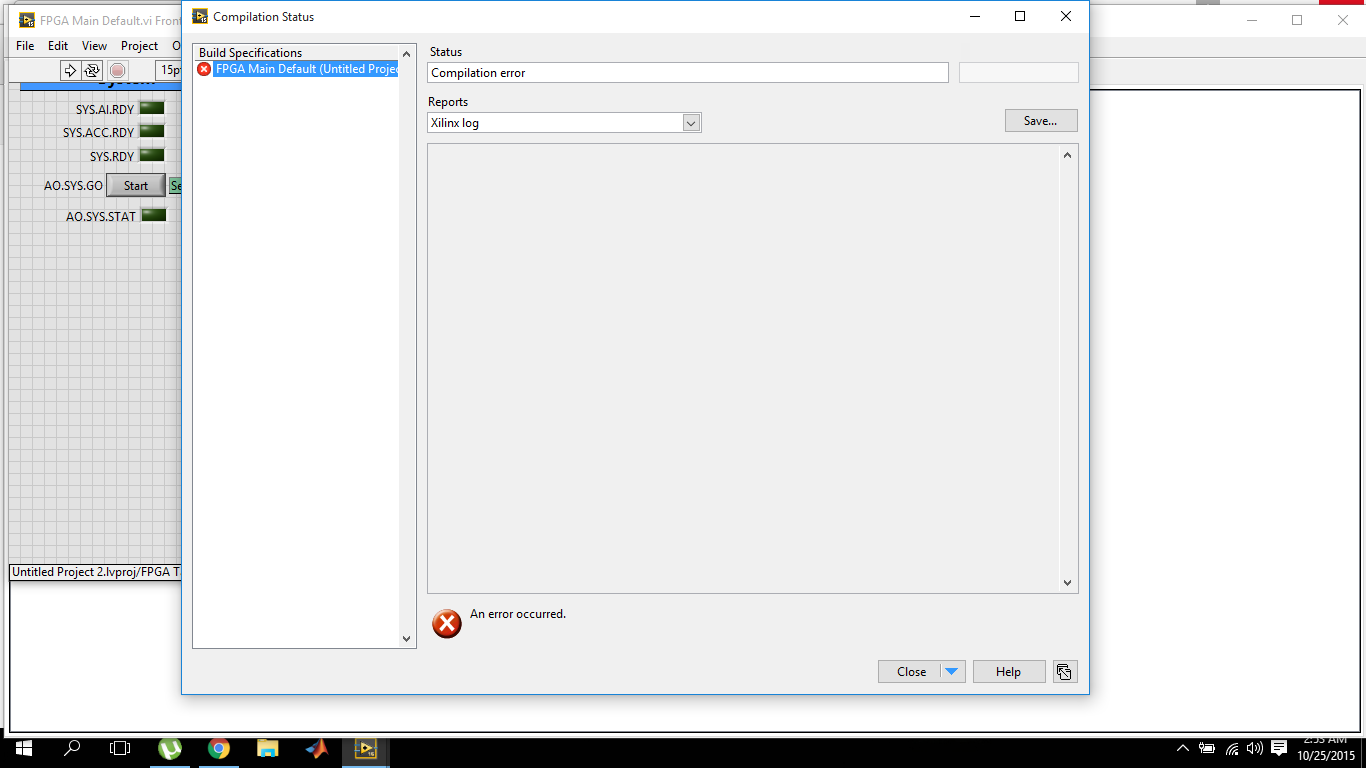

LabVIEW FPGA, 2015 compilation error

I've recently switched to LabVIEW 2015 and I'm working on OR myRIO. So also installed myRIO 2015 bundled software. The problem I have is that the compilation of fpga fails within 10 seconds.

and the target Xilinx journal report is empty

The first time when I tried to compile on 2015 version, it failed and the message box that failed came alongwith the avast antivirus warning for malicious activity. I reported it as wrong and now I tried several times with avast shield disabled control, but the results are the same. While the version of labVIEW 2014 works very well.

Now, I'm sure that there is something wrong with the installation of Vivado because this dll is part of it. The dll must be default in the2014_4\lib\win32.o directory C:\NIFPGA\programs\Vivado if you are using an operating system for 32-bit AND also in C:\NIFPGA\programs\Vivado2014_4\lib\win64.o If you use a 64-bit operating system. If the dll is not here, it is probably that the anti virus (I've never seen what happens to Xilinx but I have for other stuff).

I'm emphasizing the 2014_4 because LabVIEW 2015 uses Vivado 2014_4 while 2014 LabVIEW uses Vivado 2013_4. Since you have also installed LabVIEW 2014, you must have 2013_4 as well and if it works, you will find the dll I just wanted you make sure you check the correct directory for the Vivado 2014_4.

Download and install (reinstall or repair if already installed) 2015 LabVIEW FPGA Module Xilinx tools Vivado 2014.4. You can also use the DVD Setup if you have. It would be a good idea to do the installation with the disabled and even anti-virus try the first compilation the same. Try and let me know if the problem persists.

Kind regards

-

Acquisition of data in LabVIEW FPGA

Hello

I'm working on LabVIEW FPGA where I need to acquire data from a source and take the average. One way to do that is to continue to add each new signal to the oldest f sum and then averaged.

However, I would like to keep all of the incoming values in a file and save it. But when I tried it doing so, it gives an error message saying "table size cannot be changed. With this constraint, I am unable to write the data to a table.

Please suggest.

Thank you.

You need different acquire data, pass it to the RT, then sign in here. Impossible to use build table the FPGA as FPGA will not allow dynamic allocation of memory like that. You must preallocate the table then use replaces the subset of the table. A better way is to use DMA FIFOs. Have a look at the FPGA examples in LabVIEW for data flow. Then, on the RT, you can simply add in your files logging functions.

-

When I compile a labview fpga VI, (my version of labview fpga is 2014), I get the not found error Xilinx 10.1 build tools.

But for 2014 labview, version 14.7 Xilinx is the only compatible and that I installed. But it is still asking for Xilinx version 10.1. I tried both with configured CompactRIO and also a vi without hardware. The same is repeated each time.

What can be the problem? Please help me.

Elodie

What FPGA target do you use? I think for Virtex 2 target Xilinx 10.1 tools are used.

-

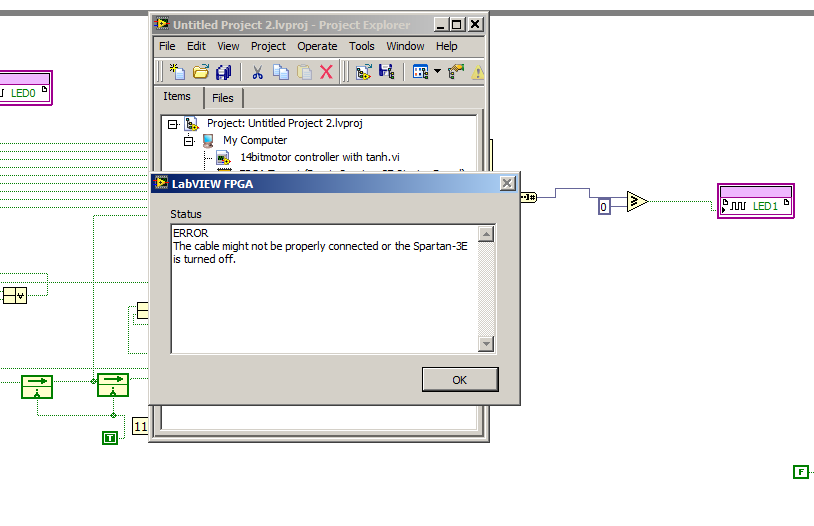

Hello

I'm trying to interface labview fpga to 2012 with Spartan E 500

I am facing two problem

a first in the figure below when I try to download Flash memory of Spartan E?

I run vi on Spartan works well but when I download it the error appear

also there is no "" "run when loading" "button which are available in a previous version of labview.

Please help

I don't have a LVFPGA version with the support of 3rd Spartan installed in front of me, so I'm working from memory here, but the option to run the VI on charge moved to the target property page (available on a right click on the target'Properties) of the standard build for the VI (as shown in your own message here)

-

Integration of IP node evil in LabVIEW FPGA

Hi all

I am having trouble with the integration of LabVIEW FPGA IP option and was hoping someone could shed some light here.

I use a simple VHDL code for a bit, 2: 1 MUX in order to familiarize themselves with the integration of IP for the LabVIEW FPGA.

In the IP properties of the context node, the syntax checking integration says:

ERROR: HDLParsers:813 - "C:/NIFPGA/iptemp/ipin482231194540D2B0CC68A8AF0F43AAED/TwoToOneOneBitMux.vhd", line 15. Enumerated value U is absent from the selection.

but I'm still able to compile. Once the node is made and connected, I get the arrow to run the VI but when I do, I get a build errors in Code Pop up that says:

The selected object is only supported inside the single-cycle Timed loop.

Place a single cycle timed loop around the object.

The selected object in question is my IP integration node.

I add a loop timed to the node, but even if I am able to run the VI, it nothing happens. the output does not illuminate regardless of the configuration.

I would say that I tried everything, but I can't imagine would be the problem might be at this point given that everything compiles and the code is so simple.

I have attached the VI both VHDL code. Please let me know if any problems occur following different boards of the FPGA.

Would be really grateful for the help,

Yusif Nurizade

Hey, Yusif,.

Looks that you enter in the loop timed Cycle and never, leave while the indicator of Output never actually is updated. Try a real constant of wiring to the break of the SCTL condition. Otherwise, you could spend all controls/indicators inside the SCTL and get rid of the outside while loop. You can race in the calendar of meeting bad in larger designs without pipeling or by optimizing the code if you take this approach, however.

-

How to import codes Verilog in LabVIEW FPGA?

I tried to import the Verilog code by instantiating followed education in http://digital.ni.com/public.nsf/allkb/7269557B205B1E1A86257640000910D3.

but I can still see some errors when compiling the file VI.

Test file simple Verilog is as follows:

==============================

module andtwobits (xx, yy and zz);

input xx, yy;

output reg zz;always start @(xx,yy)

ZZ<= xx="" &="">

end

endmodule==============================

and after you follow the above link, we have created the instantiation as file

==============================================

Library ieee;

use ieee.std_logic_1164.all;mainVHDL of the entity is

port)

xxin: in std_logic_vector;

yyin: in std_logic_vector;

zzout: out std_logic_vector

);

end mainVHDL;architecture mainVHDL1 of mainVHDL is

COMPONENT andtwobits PORT)

ZZ: out std_logic_vector;

XX: in std_logic_vector;

YY: in std_logic_vector);

END COMPONENT;Start

ALU: andtwobits port map)

ZZ-online zzout,

XX-online xxin,

YY-online yyin);end mainVHDL1;

==============================================

Sometimes, we observe the following error when we put the flag on the output port.

ERROR: ConstraintSystem:58 - constraint

TNM_ChinchIrq_IpIrq_ms; > [Puma20Top.ucf (890)]: INST

"* ChinchLvFpgaIrq * bIpIrq_ms *" does not correspond to design objects.

ERROR: ConstraintSystem:58 - constraint

TNM_ChinchIrq_IpIrq; > [Puma20Top.ucf (891)]: INST ' * ChinchLvFpgaIrq * bIpIrq. "

does not match design objects.and Interestingly, if we remove the indicator from the port of exit, he sucessfully compile on the LabVIEW FPGA.

Could you take a look at and please help me import Verilog to LabVIEW FPGA?

I followed the basic steps of the instantiation on the link above, but still it will not work.

Please find the attachment for all files.

-andtwobits.v: original file from Verilog

-andtwobits.ngc: file UCS

-andtwobits.vhd: VHD file after translating a simulation model

-mainVHDL.vhd: master of the instantiation

Since there is no sample file for Verilog (VHDL file, there but not for Verilog), it's a little difficult to do simple execution on LabVIEW FPGA, even for examples.

Thank you very much for your support, and I'm looking forward to seeing all your help/answer as soon as possible.

Records,

The best instructions we have for integration Verilog IP in LabVIEW FPGA can be found here: using the Verilog Modules in a component-level design. My suspicion is that you did not uncheck the option 'add the IO buffers' in the Xilinx ISE-specific Options parameter when running XST (see page 8 of the .pdf)

-

LabVIEW FPGA SP1 2012 & EVS1464RT FPGA IO

Hello

There seems to be problems with the new Labview FPGA 2012 SP1 in combination with an EVS1464RT embedded Vision system, which took place only after upgrading to SP1 2012 Labview:

- While trying to compile our code for the EVS1464RT FPGA or (Vision system embedded with e/s based on a FPGA Virtex-II FPGA) Xilinx tools (V10.1, since it's a Virtex-II FPGA) has reported an error saying that the compilation work has tried to set the property 'Data (output events)', which does not exist, so the Xilinx tools just quit with an error.

A complete uninstall and reinstall 'clean' do not solve the problem.

Research has shown that there is a property correct for Xilinx tools, called "done (output events)." An extended search in the Labview upwards 'incorrect data (output events)' some text files in 2 files "resource.xml" in the directories '...\National Instruments\LabVIEW 2012\Targets\NI\FPGA\IMAQIO\IMAQIO-1 "and '...\National Instruments\LabVIEW 2012\Targets\NI\FPGA\IMAQIO\IMAQIO-5' (and nowhere else).". " Change these 2 texts to 'Done (output events)' corrected the error and allowed to compile the code again.

- Another problem is that you can not start the VI FPGA-interactive (for example by clicking the Run button). This product just another error message saying that the VI '...\National Instruments\LabVIEW 2012\vi.lib\FPGAPlugInAG\IMAQIO-5\niFpgaOpenAndRun_IMAQIO-5.vi' could not be found (and there really is not anywhere on the hard drive).

The FPGA VI can be started from an another VI on the target host by using the function "Reference open FPGA". Then it works without any problems, so the bitfile has been obviously compiled correctly.

All of this worked out of the box without any problems on my old installation of Labview (before 2012 SP1 update).

The first problems now seems to be a simple typo, and using the function "Open FPGA reference" is a workaround for the second problem. But I'm very angry that National Instruments does not seem to test their software before releasing. A service pack should never break things that worked before.

Find these alternatives cost me 3 days, which, in my opinion, could be acceptable for open-source software, but not if you pay hundreds of euros per year for a "Standard Service program. For that kind of money, I expected NOT to test all the changes that they do well.

Best regards

Dr. Merlin Welker

Hello Mr. Welker.

First of all, thank you for your comments. I'm really sorry that you stumbled on this issue. Please let me give you some background information on it.

You are right that the update for the versions of service pack is to address reported problems and he should never break things that worked before. Unforunately, a change in LabVIEW FPGA exposed an underlying issue with e/s NOR-IMAQ driver FPGA compilation. We have identified this issue and addressed it in the Acquisition of Vision Software communicated in February 2013, including e/s NOR-IMAQ 2.6.1.

It is now available in the Update Service of NOR. We also found and addressed the issue with the FPGA Open running and run interactively in the thatsame release.

We recommend the upgrade to use the latest version of driver, whenever you upgrade from versions of LabVIEW, to ensure better compatibility between them. Please note that whenever you upgrade LabVIEW FPGA or Vision Acquisition Software, you should also recompile your LabVIEW FPGA projects.

While these issues were found and corrected in the latest version, we are now reminded our development and testing processes for future versions. Please accept our apologies for the inconvenience. National Instruments is committed to your satisfaction and to maintain your confidence in our products.

Thank you

Elmar

- While trying to compile our code for the EVS1464RT FPGA or (Vision system embedded with e/s based on a FPGA Virtex-II FPGA) Xilinx tools (V10.1, since it's a Virtex-II FPGA) has reported an error saying that the compilation work has tried to set the property 'Data (output events)', which does not exist, so the Xilinx tools just quit with an error.

-

NEITHER 9512 with Labview FPGA Interface

Is it possible to use the NI 9512 stepper with Labview FPGA interface drive unit or is it only possible to use it with the interface of scanning? When I try to add the module to a FPGA target, I get an error telling me that Labview FPGA does not support this module with the latest version of NOR-RIO, but I have the latest version of OR-installed RIO.

Hi Checkit,

You're right - the 9512 cannot currently be used in FPGA. There is an error in the documentation. The 9514 and 9516 can, however.

Maybe you are looking for

-

Same image several times in a project?

Can someone explain to me how I can use the same image several times in the same project?

-

Actually, I meant on the left side. I've just updated to Firefox 5 and the left vertical column with my favorites have disappeared. That's how I walk across the web. I can't find a way to put it back.

-

@ Startup error: < root Windows > \system32\hal.dll.

A "highly recommended" malware free program apparently deleted a file system. After the reboot, I received this message at startup: Windows could not start because the following file is missing or corrupt: \System32\hal.dll. Please reinstall a copy o

-

I recently bought a Nikon Coolpix P90 camera. I have installed the software provided with the camera, but the ViewNX program that is suppose to allow me to edit, adjust my willingness to images etc... does not. I get an error message saying that Vie

-

Host process for Windows Services has stopped working

Signature of the problem: Problem event name: APPCRASH Application name: svchost.exe Application version: 6.0.6001.18000 Application timestamp: 4a481bab Fault Module name: svchost.exe Fault Module Version: 6.0.6001.18000 Timestamp of Module error: 4a