Limited to 127 for FPGA PID gain

Hello

I have tow questionq the first technical is the second commercial is.

1 * for an FPGA with PXI8108 and PXI-7841R application I want to insert a value of "2100" so greater than 127, but module of pid gain is limited to 127.

How can I do. Thanks for your help :/

2 * I want to buy another product like target FPGA PXI-8108 for other applications, but I need PXI7841R with LABVIEW FPGA and RT I only move forward without other complementary modules to insert. Is the chassis necessary?

I can't find other versions like PXI7841R do the same job with the same performance with PC but cheaper (no chassis & PXI-8108)? i ' am, search the Web, OR, but I have not found so can you offer me any product desired OR

Thanks for all your response.

Riadh WILSON.

(2) the chassis has the RT controller. You can get cards to USB (no RT) R series FPGA / PCI / PCI-Express that plug into an ordinary PC. You can install LabVIEW Real-time on a PC, but it requires some hardware configurations so that it can be supported. Have you considered a device of RIO as a CompactRIO / sbRIO? These are materials NI Compact integrated a RT and FPGA which are cheaper than the PXI controller.

Tags: NI Software

Similar Questions

-

I use the PID advanced VI to a pressure regulator and had tried to vary the winning entry proportional to the VI using an equation based on other settings, such as the behavior was similar to gain scheduling, only contiguous versus by steps. Unfortunately, it seems that PID VI cannot handle the PID gains that are continuously variable from iteration to iteration. The result is zero, and dig in the block diagram of the PID VI, it is barely readable, but seems to do something different in case of a detection of a change in gains of PID. So my question is, is there a simple way to do what I'm trying to do with the provided screw OR, or am I limited to fixed PID gains? I couldn't works around the problem by allowing the calculated algorithmically proportional gain will persist for a number of iterations before allowing an update?

Hello

Yes, you can.

Don't forget: create your own copy of the VI before you change! Never change live in vi.lib!

-

Synchronization of multiple FPGA PID loops

Hello

I am the design of a PID controller for each of the three axes (X, Y and Z) of a piezoelectric stage using the FPGA module and a cRIO. I used the example of project "Using Discrete PID - cRIO.lvproj" (labview\examples\control\pid\fpga.llb\CompactRIO) as a starting point and I've basically added two PID loops more on the FPGA VIs to the other two axes. I can get the controller to work for an axis at the same time (in simulation mode), but whenever I try to run all three controllers simultaneously, only one works. In order to synchronize between the host and the FPGA VIs, I used three interruptions for each PID loops, but it seems that a single interruption works when I run the code... No idea how to synchronize the three loops of PID with the host VI?

Kind regards

Shin

I think that it is an expected behavior, by the documentation: "VI the interruption is a shared resource, so multiple uses of it induce a further delay and jitter due to arbitration." If you are waiting for the interruption to see, then the other loops cannot continue because interruption VI does not work. On the FPGA if you want all the PIDs to operate at the same speed of loop, put them all in the same loop and use only a single interruption. Or use another synchronization mechanism (set to a boolean of the host, wait it is defined and then erase it on the FPGA). The interruption is only for purposes of simulation, in any case, since the 'central' is running on the host computer. In a real system, the plant works continuously and FPGA directly reads the sensors and outputs, the readers so the only value provided by the host is the set point and is not required for synchronization.

-

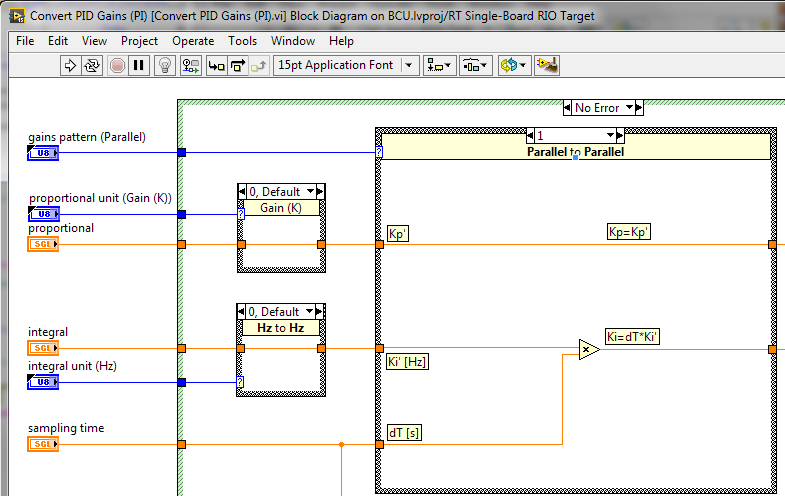

documentation error: convert the PID Gains

There is an error in the documentation for the Convert PID Gains VI. In the table explaining the calculations for the parallel form, the documentation says

(Ki = Ki') but the calculation of the VI is Ki = dT * Ki':

(Ki = Ki') but the calculation of the VI is Ki = dT * Ki':nathand,

I filed 595523 CAR to solve the conflicting equations.

Daniel C.

Technical sales engineer

-

How to implement point filters fixed for FPGA

Hello!

I am applying the bandpass filter Butterworth for FPGA.

I managed to develop filters of fixed point that suits my needs, but I don't know how to implement on a table in a project after the FPGA code generation. I tried to understand it in the examples, but I was not very successful.

My time to finish what runs, any help would be really appreciated...

Any suggestions?... some examples?

Thanks in advance

I've already done that and solved the problem.

In any case thank you and have a nice day

Ljubica

-

I recently discovered that browser Konqueror for Linux can help the user to limit the CPU usage while visiting a Web site using flash technology by changing the settings in the Flash section and by adjusting the slider settings VERY HIGH to HIGH and AVERAGE and so on. It actually works and it doesn't have a direct impact on the overall performance for flash player, but it can lead to conflicts if other such extensions that add blocker or click-to-flash are also enabled.

Maybe you can add a similar setting in Firefox in the browser or just as a useful addon or extension option section.

Hi Michael,

I love the sound of that. I found an add on which has Visual for the CPU usage as well as can be usefulTopic: memory page also contains a detailed report that breaks down each process that occupies this space. I wonder if it is a supplement that taps by limiting these

Something like limiter window and tab -

Band bandwidth SMU for FPGA chassis

I'm specing on material for an FPGA FlexRIO system. The module FPGA and adapter, we will use has already been defined, a 7975R and a 5782. For our application, we will be streaming 2 inputs analog on a RT controller attached. From my understanding, these samples will be single precision floating point numbers, each of which is a piece of 4 bytes. Assuming that the 5782 max sampling rate is used, 250 MECH. / s, I think that I will need 2 GB/s of bandwidth on my SMU chassis.

Here my question, then, what SMU chassis should I consider? The SMU-1082 has "up to 2 GB/s per-slot dedicated bandwidth", but it is a real or theoretical number? Normally, I would just get the next thing that high, just to be sure, but there is a significant price difference on the way to the SMU 1085, which is also much larger I need. So I would like to save space and several thousands of dollars if I could get away with a 1082. Sampling does not quite to the max modules of adaptation would be acceptable, but I would be interested to know where about my maximum sampling speed would be.

Thanks in advance for your help.

The 1082 has more than enough bandwidth to stream data at a time to the analog inputs of a 5782. The 5782 has a 14 bit ADC with two channels that sample to 250 ms/s. These samples are returned as an I16 with the two least significant bits filled with zeros.

So assuming that you transfer all I16, rather than packing the 14 bits of data, you would have the following bandwidth requirements.

2 channels x 2 bytes/sample x 250 mega-samples per second = 1 GB/s

The 1082 a 2 GB/s of throughput dedicated per slot. The 7975 accommodates up to 1.6 Gbps streaming. I would recommend calling chat with someone, if you are looking for a recommendation on what type of chassis to purchase, but based on the requirements of streaming that you're fine with the combo 7975 and 1082, you thought. Just make sure you get a controller which can accommodate streaming speeds you're looking for. The 8840 is a good candidate.

-

For the PID variable time interval

Hello world

I measure the ph and control the flow of co2, so I decided to use the useful PID screw like I do for my temperature control.

the difference and so my question is, I have not want (/ power) to run the PID in a timed loop, in fact my intervals of measurement (eg. every 30 seconds ~ or ~ 60) may vary in the second range, because of the way I acquire data and how I put the valve in co2.

so my question is: is this a without problem?

I'm not sure weather the internal timer or providing the dt will explicitly be responsible for this?

(and I can't test it on atm equipment)

thx for your time

Shouldn't be a problem. Don't wire dt, let the PID to use its internal clock. Could make it more difficult to tune the PID, since you will have to account for the worst cases (longer delays between updates).

-

I am trying to stream as quickly as possible from the to a FlexRIO 7966 5154 digitizer. From the example "NISCOPE fetch Forever" in LV2012, I can implement the acquisition on 5154 @ 40MS/s, 50 k of data I8 piece and the graphical indicator seems to keep well indefinitely.

I tried then write data to an FPGA - FIFO target host, and it chokes. With FIFO write the method inside the loop of 5154 fetch the 5154 ends in error because of the "overwhelming memory" (it fills its on-board memory until the HOST is reading). With FIFO writing in a parallel consumer (queue conduit) loop, the queue overflows just because he can't write that as fast as the 5154 FIFO provides samples in the queue. What Miss me? The 5154 uses a PCI DMA bus (I think), so I think that if he could hold, the host to the FPGA PCIe bus must be capable.

There is another factor, that I have not taken into account? Sorry I can't provide the VI since the installation of the LV is on a PC not connected to the network. Any advice or suggestions would be appreciated.

Thank you

Mark Taylor

For future reference, I ended up resolving this by moving the implementation on the actual FPGA. I had run in mode "on the development computer with i/o simulated" and no matter what I did with the start-up or sizing FIFO sequence, it just doesn't work.

After compiling and running on the FPGA, all right. Maybe it's the basic knowledge, in fact I remember somewhere in my travels reading that don't accurately represent timing problems when running to the old fashion, but LV FPGA has kind of us painted into a corner with the compromise of simulation/compilation. They do not include Modelsim, which is the only tool that enables co-simulation do functional and verification of the timing set (we Questa, unfortunately) and independent VHDL simulation captures the interaction host with precision (and software processing/timing is impossible to quantify!). In my situation, the only way to operate at speed is in the FPGA, but then I can't see all of the things that I need to see to debug... ARGH!

Additional links and resources always will welcome (on debugging of FPGA LV and design in general). I found a couple of things below, which was somewhat useful:

"NEITHER powerful LabVIEW FPGA Developer's Guide"

http://www.NI.com/Tutorial/14600/en/

I found a link to an "FPGA Debug Reference Library": http://www.ni.com/example/31067/en/, but my installation does not seem to have this available.

And it looks like 2013 may add functionality to help alleviate some of this via the node of the execution of office referred here to the 'Test and debug LabVIEW FPGA Code'

-

The initialization of the lut for FPGA

I am currently generate a waveform on an FPGA using a program to initialize a look-up Table (LUT). When I select call VI of initialization, and then select the path and click OK, Labview begins to consume a lot of time CPU, but nothing seems to happen--none of the buttons except the open dialog box file and the close icon (red box with an x in the upper right corner) is grayed out. Someone at - it ideas? Maybe I'm doing something wrong, but there is very little documentation on this function. I have attached the VI that I use to try to initialize my table.

Any thoughts would be great.

Cheers, Matt

This must have something to do with the complexity of the LUT VI initialization. As a work around, I simply wrote the data in a file that I then read for the initialization of LUT. I have attached the screws again.

The lack of reactivity is a problem, but also the absence of any indication of an error.

-

Write for FPGA Boolean control RT... He switch or lock?

I have a reset button in my FPGA code that I am trying the RT. Once this button has been programmed, do I need to "pop" back out when the FPGA reads it? The switch/latch function parameters make a difference? If I put it to lock, it will manage the return false, once it is read, for me?

There is no lock. I think if there was, it would be much easier application handshaking with Boolean values.

-

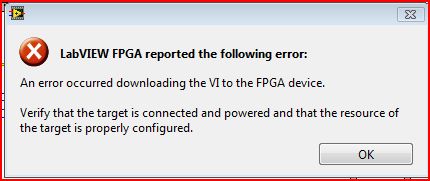

How can I disable the firewall of windows for FPGA

I tried to compile an FPGA vi. Towards the end of compilation, asked me if I wanted to disable something in the windows firewall (probably to allow for communication between my computer and my PXI-7854R). At the time, I had no administrative privilege and couldn't do anything but cancel this request. Of course, nothing that I compiles now runs. How to get back to the point where I can disable the firewall?

A picture of the error message is attached.

Thank you

Stephen

Hello Stephen,

Thank you for posting what solved your problem - it helps other users who stumble on this troubleshooting page. So that they can see what position fixed, could you please go ahead and mark the message as a "solution" and give good Bravo?

Thank you!!

-

LabVIEW community support, we need your help.

We found this question on a discussion of embedded design forum. A verilog programmer plans to LabVIEW FPGA to update his project. We feel that his question perhaps justify a wide discussion of real users of LV FPGA so that we have here on our forum and created this thread. There the LabVIEW programmers who could offer some advice? See the question below.

Yours truly,

The media NOR social team

Welcome to the community of LabVIEW FPGA. We will need more information about your project needs specific to suggest the current material, but in general, NOR has a wide variety of reconfigurable hardware to choose from. LabVIEW FPGA can also target several academic councils of the Xilinx University program.

LabVIEW FPGA does not support Verilog directly as a top-level for the import file. However, if you wrap the verilog in a thin fascade VHDL, it will work since Xilinx knows how synthesize/simulate mixed models.

-

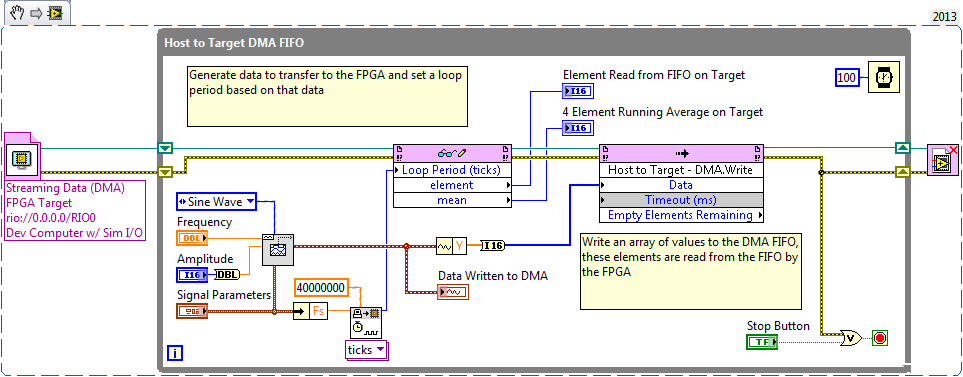

Hello

I've seen a lot of examples on how to stream from the FPGA for a crowd of RT VI.

I'm interested in doing the exact opposite. I have data, (table SGL) in a VI of host of RT that I need to deal with on the FPGA.

Directions on how I can do this?

I tried shared variables and a DMA FIFO with no luck.

-Eldrich

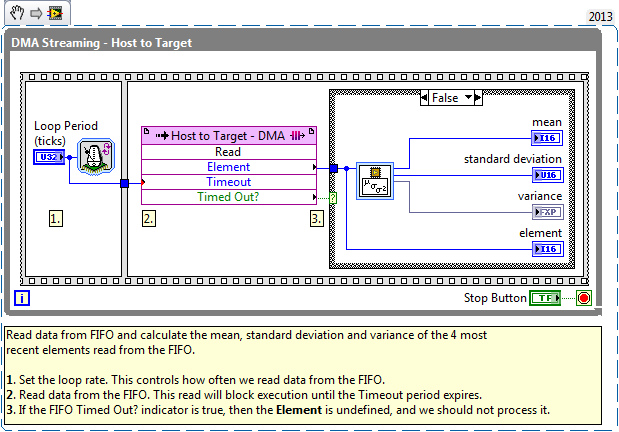

If you use a LabVIEW 2013, there should be a simple example in the Finder for example of OR. It's under CompactRIO-> data transfer and storage-> host target DMA-> Streaming data .lvproj (DMA). If you are not running to 2013, here is a screenshot of the diagrams (very simple).

Host:

Target:

-

Driver Epson Stylus NX 127 for

I am trying to install a printer Epson Stylus NX 127, I bought earlier this year, when I bought and installed everything was ok without difficulty, but after some use, but I unplugged the printer and has continued to use my previous printer who was a canon MP 530 series copy 1 because I had little ink and wanted it to end , Now I'm trying to re install my Stylus NX 127 cannon and told me that they don't have a driver for this computer and the only for Epson they have is a driver AL 2600 and Epson Stylus NX 125/127 has been installed with this driver.

When I went to printers and drivers, I noticed that a printer was there on the screen named AL 2600, when I put the mouse on this printer, I noticed that the name of the printer was 2600 Epson but the name of the manufacturer is Canon and the State showed that it5 was ready to print, when I went to print a test page My Sytlus NX127 has not moved,I tried everything to disconnect Canon MP 530 of the port, but after that, I was told they can't interrupt them this printer from this port, which was TCP / itI went to try and install Stylus NX 127 to a new port and was successful and received the DEVICE of PROTOCOLRaw of port9100m; "TYPE of PORT Wpson NAME Epson Stylus NX ADJUSTER 127; Network printer.I still can't my printer to begin with, please LET ME KNOW WHAT I CAN DOaNTHONY gAJADHARTry to connect to the printer that you want to use, download and run:

http://support.Microsoft.com/mats/printing_problems/

Also try to update and restart your PC.

If the problem has NOT been resolved, then contact the manufacturer support.

Maybe you are looking for

-

Bad video memory - Satellite 5200

I have a scrambled on display problema Toshiba Satellite 5200. The adapter isNVIDIA GeForce4 460 Go, 64 MB, integratedRAMDAC. A test of Micro-Scope shows a badvideo memory. How to solve the problem(change the video, or only video memory cardor is it

-

Recommend me a scanner with OCR good & speed reasonably good scan.

Hello I used to have HP F2200 printer/scanner, OCR has been fantastic. It scanned perfectly. The user interface is so intuitive. In front, the OCR of this old model even beat the current Canon scanner. I bought the scanner Canon only returned because

-

Somehow, an e-mail address has been added to my popup list slot (to :) in the Messaging window create for hotmail. I didn't add that email address. It is not listed in my contacts, but appears in the drop-down list only. I've found no way to remov

-

Windows backup fails with 0 x 80080005

You try to start Windows backup fails with the following error: The backup application could not start due to an internal error: Server execution failed (0 x 80080005). Please help, thanks.

-

ListItemComponent data type c ++

In my application, I have a ListView that displays a ListItemComponent I have reproduced a slightly simplified version here as I'm sure you don't want to see all the containers that show that more than data. ListView { objectName: "alarmList" id: ala