NEITHER 9512 with Labview FPGA Interface

Is it possible to use the NI 9512 stepper with Labview FPGA interface drive unit or is it only possible to use it with the interface of scanning? When I try to add the module to a FPGA target, I get an error telling me that Labview FPGA does not support this module with the latest version of NOR-RIO, but I have the latest version of OR-installed RIO.

Hi Checkit,

You're right - the 9512 cannot currently be used in FPGA. There is an error in the documentation. The 9514 and 9516 can, however.

Tags: NI Hardware

Similar Questions

-

Model a block synchronous dual-port RAM with LabVIEW FPGA

This question caught my attention recently.

I am trying to model a particular design element called "RAMB4_S8_S8" with the LabVIEW FPGA module. This element is a block synchronous dual-port RAM allowing simultaneous access to two ports independently from each other. That being said, a port can perform read/write operation to this RAM while at the same time, the other port might be able to do the same thing. There are two opportunities of possible port conflict, however. The first is when both ports are trying to write to the same memory cell. The other scenario is when a port writes in a cell memory while at the same time the other port reads from it. Other than that, everything should be a legitimate operation.

In order to reproduce this I select memory block that is integrated into my FPGA target. An interface is configured to be the playback mode, and the other is set to write fashion. For the option of arbitration, I let the two interfaces to be "arbitrate if several applicants only. Then I got a compiler error when I tried to run my FPGA code for this model in a SCTL. The error message is something like "several objects to request access to a resource through a resource configured with option interface" arbitrate if several applicants only ", which is supported only in the single-cycle Timed loop if there is only a single applicant by interface.

This error goes away if I replace the SCTL with a simple while loop, but not what I would like to implement. So I wonder if there is a better solution to this problem, or is it just the limitation of the LabVIEW FPGA module.

Thank you.

Yes, you can use a form of conduct to perform the operations you want in the generations clock cycles, but all the code is inside a single SCTL. Basically, read the first address and storing in a register in a single cycle and then read the second address in the second clock cycle. This would allow you to two readings of valid memory every clock cycle 2. I have included a crude extract to illustrate the concept. The case selectors are identical with address A being connected to the memory in the true case, B in the case of fake address. Your biggest model memory dual port will be intact, but it will operate at 1/2 rate.

Take a look at the white paper that provides more details on the construction of memory:

Data on a target FPGAS (FPGA Module)

The ball on the memory block indicates that memory block double port cannot be applied in a configuration of reading, which is a double ROM. access read/write port must be imitated with custom code.

-

HELP - FPGA SPARTAN 3E-100 CP132 WORKS WITH LABVIEW FPGA?

HI EVERYONE, GET ON IM TRYING TO USE MY FPGA WITH LABVIEW, BUT I DO KNOW THAT IF ITS COMPATIBLE, I INSTALLED THE DRIVERS, MODULE FPGA AND LABVIEW 2012, IM USING WINDOWS 7 32 BIT, AND AFTER I COMPILED ITS SAYS:

LabVIEW FPGA called another software component, and the component returned the following error:

Error code:-310601

NOR-COBS: Impossible to detect the communication cable.

Check the communication cable is plugged into your computer and your target. Also, verify that the proper drivers are installed.Thank you.

=)

Hi dvaldez2.

LabVIEW FPGA offers no support for any material to third parties, other than the 3rd Spartan XUP Starter Kit. These are probably the drivers you downloaded.

http://digital.NI.com/express.nsf/bycode/Spartan3E?OpenDocument&lang=en&node=seminar_US

However, this driver supports only the Starter Kit Board itself (http://www.digilentinc.com/Products/Detail.cfm?NavPath=2, 400, 790 & Prod = S3EBOARD). You may not use the driver with any other Xilinx FPGAS.

I hope this helps.

-

Laser digital lock with Labview FPGA?

Hello

Sorry to bother if you are not interested in this issue of digital signal processing. We are looking for a possible digital solutions to our problem locked frequency cavity closed-loop laser (see attached PDF file for more details). The goal is to flatten the PZTs transfer function (cancel the resonances and anti-resonances and their phase shift matching) in the frequency domain, in addition to the normal PID control. Input/output necessary voltage signals are small (we have our own amplifiers high power for the PZTs), and their bandwidth must be at least of 50 kHz (100 kHz would be optimal).

Among various OR hardware/software (DSP, FPGA, cRIO etc.), would anyone recommend a cost-effective solution for rapid prototyping?

Thank you!

I would like to look at the FPGA PXI cards nor 7854r. I rate of 750 kHz, 1 MHz AO. According to the involved treatment, you might expect between 200 and 750 kHz closed control loop. If the treatment is very intense, it's probably something less than 200 kHz.

That said, the key to these performance levels is not trivial and great care and attention to detail must be used in the coding of the FPGA.

Good luck

-

CPU register accessible in LabView FPGA FlexRIO

Hello people, I wonder if it is possible to get the following behaviors of Labview. I think that it is not.

Description of the system: application of CVI which communicates with SMU FlexRIO via controls and indicators.

Problem: The design of a CPU-FPGA interface specification which lists the "books" as a combination of reading and reading/writing-the bit fields.

Example:

According to the specification, there should be a 32-bit register. 31: 16 bits are read-only, and 15:0 bits are read/write, from the perspective of the CPU. In the world of labview, I would just do a uint16 control and indicator of uint16 and do with it.

However, to meet the specification (written for microprocessor buses) traditional, a reading of 32 bits of an address should read back the full content of the 32-bitregister to this place (implemented as flops on the FPGA, with appropriate memory within the FPGA device mapping). In the same way a 32 bits of an address entry must store the values in this registry (properly masking wrote at 31: 16 bits within the FPGA device).

Is it possible for me to have a unique address (basically, a component unique labview block diagram) that will allow me to accomplish this behavior? It seems to me that the only solution is to pack my records with bit fields that are all read, or all the read-write in order to register in the paradigm of labview. This means that the spec should go back and be re-written and approved again.

Thanks in advance,

-J

Thanks for the detailed explanation. I am familiar with the reading and writing in the FPGA registers - I did a lot of work non-LabVIEW recently with an Altera FPGA. I haven't, however, used the CVI to LabVIEW FPGA interface, I only used the LabVIEW interface. I'm not sure if your question is about the CVI, LabVIEW FPGA interface or both.

JJMontante wrote:

Thus, a restatement of my original question: y at - it a mechanism with the use of indicators of controls where both the FPGA AND the CPU can write to the same series of flip-flops in the FPGA? If I use an indicator, the FPGA can write to the indicator, but the CPU cannot. If I use a control, the CPU can write in the control, but can't the FPGA. Is this correct?

On LabVIEW FPGA, a control and indicator are essentially identical. You can write a check, or read a battery / battery, using a local variable in the FPGA code. It is common to use a single piece of front panel to transfer the data in either sense, and it's okay if it's a command or an indicator. For example, a common strategy uses a Boolean façade element for handshake. The CPU writes a value to a numeric control, and then sets the value Boolean true to indicate that the new data is available. FPGA reads this numerical value, and then sets the Boolean false, which indicates the processor that the value has been read. The LabVIEW FPGA interface (side CPU) covers also all elements of frontage on the same FPGA whether orders or the lights--they can be as well read and written.

That answer your question at all?

-

Version of the C API for LabVIEW FPGA 2011

What is the version of the C API that will work with LabVIEW FPGA 2011?

I guess as this one: http://www.ni.com/download/fpga-interface-c-api-2.0/2616/en/

Version numbers seem to start by 2012 years. It's the latest version I could find before 2012 and he was released in August 2011. This time coincides with the annual festivities of the NOR week where a large part of the software/hardware is released. It's a small download, so it shouldn't be difficult to download it and try it.

But, you'll still need LabVIEW FPGA development according to this white paper: http://www.ni.com/white-paper/9036/en/

-

How to use bidirectional I/O in the CLIP of LabVIEW FPGA?

How to use or define two-way i/o for CLIP with LabVIEW FPGA? I want to use 1-wire communication inside the kernel CLIP, the function will be implemented to read and write as I/O inside the CLAMP.

The XML Generator (CXG) 1.1.0 ELEMENT does not support.

Thank you

Supawat

Work after separate IB pin (bidirectional) at the entrance and exit. Thank you.

-

The President complied,

Is LabVIEW FPGA support for numbered kit ML-505 (Type FPGA: Virtex 5 LX110T) available or not? If Yes, where is it?

The only FPGA that is supported by LabVIEW FPGA is included in National Instruments hardware. You can't target the other with LabVIEW FPGA kits.

-

Spartan - 3 driver and Labview FPGA 2009

Hello

Do we need a new Spartan-3E driver to work with Labview FPGA 2009? And, if so, is it provided by National Instruments?

Thank you

Walid F. van

Hello everyone

The driver for the Spartan 3rd WHAT XUP Starter Kit are now on the site OR here:

http://digital.NI.com/express.nsf/bycode/Spartan3E?OpenDocument&lang=en&node=seminar_US

Just click on the link to get driver.

Kind regards

John Harvey

-

Error-63101 when executing the FPGA Interface C API Generator in LabVIEW 2012

I'm using LabWindows CVI 2012 and 2012 LabVIEW FPGA module. I try to use the FPGA Interface C API generator and I get the following error from a freshly generated .lvbitx bitfile. I use the local server compiles on my PC.

Error-63101

NOR-RIO: A valid .lvbitx bitfile is required. If you are using a valid .lvbitx bitfile, the bitfile maybe isn't compatible with the software you use. Determine which version of LabVIEW was used to make the bitfile, upgrade your software to this version or later, and then try again.

The problem occurs when executing CVI or LabVIEW. I was able to do this earlier when I was compiling the FPGA in LabVIEW with the API generator 2011 downloaded from the Web site.

A bit of weirdness in my setup, it's that I charged it off downloads from the website (latest files after 2012 NIWeek) rather than the normal distribution DVD. I installed LabVIEW, so NI RIO, then the Xilinx tools compatible with 2012. It works very well when you talk to the FPGA to a LabVIEW vi running on my Windows PC to the host.

Any suggestions?

Problem solved. I had to download FPGA Interface C API generator 12.0. It works now.

I would have thought that if a product was called on the menu in LabVIEW 2012, it would be prompted to upgrade to a compatible version, when I installed LabVIEW. The old version is not compatible with version 3.0 bitfiles, as identified on the following lines at the top of the .lvbitx file:

3.0 -

LabVIEW FPGA failure with compiler Xlinx?

I'm in LabVIEW FPGA 8.6 with NOR-RIO 3.0.1 (to 8.6). When I compile a simple program, I get the notorious:

«Error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

I checked the FPGA compile server and I ran the utility fixTlink.VI with no improvement. This produces two identical PC, neither one having a FPGA installed card.

Any ideas?

After further analysis, the problem was to be in our facility in LabVIEW FPGA 8.6. Using the correct Installer of NEITHER solved the problem.

This thread is now resolved.

-

The project-centric issue of peer to Peer with an external compiler in LabVIEW FPGA

Hi all

FPGA OR Version: 14.0

I have an application developed in LabVIEW interfacing FPGAs developed in LabVIEW FPGA making of peer to peer Communications.

Everything works fine.

I try on the port to Visual Studio 2013 (on the same PC) and am able to communicate with the FPGA very well using the C API.

However, I have a problem now with the help files or the peer supported external compiler peer.

I get these errors:

1. cannot open the file source 'PublicIncludes/nistreamCommon/prefix.h '.

2. impossible opening the file source 'PublicIncludes/nistreamCommon/postfix.h '.

in

c:\Program Files (x 86) \National Instruments\Shared\ExternalCompilerSupport\C\include\nip2p.h

in my project...

I looked in the folder c:\Program Files (x 86) \National Instruments\Shared\ExternalCompilerSupport\C\include\ and the PublicIncludes\nistreamCommon folder does not exist.

What I am doing wrong?

Hello!

It seems that you have worked with another engineer of Applications on this issue. For the love of documents, the nip2p library is not supported in CVI. There has been cases where users were able to get this work to comment on the two header files.

Thank you!

-

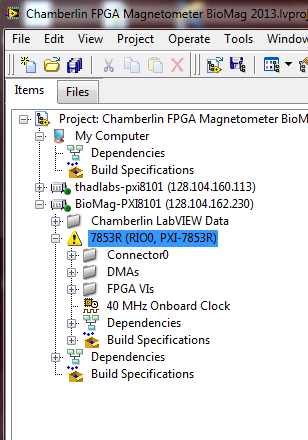

Software FPGA with LabVIEW 2013

I have a system with a rotating computer "development" under Windows 7 and an NI PXI-1036 chassis with a PXI-8101 controller as well as a card FPGA PXI-7853R. Recently, I upgraded to LabVIEW 2011-2013 of LabVIEW. I kept LabVIEW 2011 installed just to make sure everything is still working on the new LabVIEW.

Now, when I open my project in LabVIEW 2013 Project Explorer, my FPGA comes with a warning triangle yellow next to him (see attached photo). The warning says:

"Software support for this target FPGA is not installed on the computer. You can view and copy elements into the project, but you can not compile any screw under the FPGA target, until you install support for the target. Refer to the documentation of specific material for more information on the proper drivers and for more information about the installation and configuration of the target FPGA ".

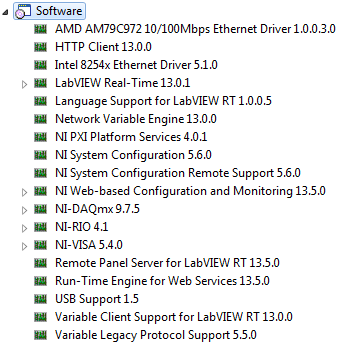

Regarding the installed software, I have LabVIEW SP1 of 2013, 2013 of LabVIEW FPGA Module SP1, SP1 of Module 2013 LabVIEW Real-time, and Xilinx Compilation tools 14.4. On the chassis of the TARGET (with the PXI-8101 controller), I have attached a list of installed software.

Interestingly, when I open the project in LabView 2011, no errors or warnings are present with the FPGA card. It is only under LabVIEW 2013 I see the warning. Did anyone see a glaring omission of software that could be the cause of LabVIEW raise this error? Thank you for your help.

Best guess is that're missing you the driver for your FPGA device. Try to install the latest version of NOR-RIO (or at least the version supplied on your 2013 SP1 install disks). Have you installed device drivers at the time that you have installed SP1 2013 LabVIEW?

-

Change the path open the initial sequence of the operator Simple of TestStand with LabVIEW Interface

Hello

I use an Interface with LabVIEW TestStand operator similar to the TS IO Simple example.

But I want to change the path when you click the button open the sequence file, I want a specific path.

Any help is apreciated.

Kind regards

Daniel Coelho

Daniel, you might be interested by this Knowledge Base:

How can I change the default directory for the open file dialog box in TestStand?

I searched ni.com for teststand of dialog box open the file and it was the fifth or so link.

-

A UDP connection target FPGA with LabVIEW

Hello

I have an FPGA with Ethernet connected to my HOST PC, now I would like to connect the LabVIEW FPGA target and access to its records. Please suggest me.

Kind regards

Chetan

Hi Cheetah,.

don't know, because I do not know your format or the manual of your FPGA...

Maybe you are looking for

-

Installed FF 16, 17, 18. Does not open in the normal administrator account, or with "Run as Administrator" but will be in SafeMode to W7. Changed the permissions (normal connection had to do in Mode without failure of W7, would not allow (connected a

-

When I turn on the camera in win8 application, I get the camera, but there are only 3 controls:Mode options, timer and video from the camera.I want to be able to take a picture to record a video and save it, but these 3 controls don't let me do.I jus

-

Updated ReadyNAS 316 OS, returned with the DNS error

I've recently updated as well to my NAS 6.5.2 devices and since doing so, the VA started sending notifications, update attempts failed. When I investigated further, I discovered that none of the functions of the update seems to work. For example, whe

-

Round a number to 2 decimal places

Hello I have a calculated value that returns 10 more digits after the decimal, example: 2.2482352941176. What is the best way to change this value in TestStand to return a number which is rounded to 2 decimal places (2.25)? Thank you best regards &,.

-

Someone been able to pair a headset bluetooth with the Xoom? I have the WiFi Xoom and Motorola S10 - HD bluetooth headset. I can get the headset to pair with my Droid phone, but my Xoom cannot see them. Does anyone have any suggestions? I know the wo