Synchronize the clocks on M-series via DDK

Hello

We are in a new cycle of development and require the clocks on our maps of the series M (6259, 6225) to synchronize. I searched the docs of NOR and the Forums for more information, but am coming short on details to implement synchronization.

Firstly a bit of history... Two cards by computer. The captain 6259 samples 24 HAVE 2000 s/s using a rate of Conversion 49140 Hz and the slave 6225 12 samples HAVE 200 s/s with a Conversion rate of 2457 Hz.

My understanding of the synchronization process follows. On 6259 mask, the 10 MHz reference clock is exported via a RTSI line. The slave 6225 matter 10 MHz reference clock and activates its PLL. 6259 sampleclock HAVE is exported via a second line RTSI and divided by 10 to trigger sampling HAVE on the 6225.

How did the 10 MHz reference clock available in the DDK? How the PLL get activated in the master and slave? The AI SampleClock can be divided into bottom directly before the export or import on the slave? Or the division shall take place via one of the counters of GP? Are there examples of code?

Thank you!

Gord

Just a quick update on this issue. We were able to help get the operational application. The main issue was the PLL_Control registry was not written correctly. Which should have been as follows:

PLL_Control (454)<==>

PLL_Multiplier is 8

PLL_Divisor is 1

PLL_Enable is 1

PLL_VCO_Mode is 3

Tags: NI Products

Similar Questions

-

Synchronize the clocks of 2 PCI cards for analog inputs with e/s digital reference

I'm trying to synchronize the clocks of reference of 2 PCI cards so that the analog inputs are synchronized. However, my appilcation has also digtial e/s on two cards, and who apparently made the mistake DAQmxErrorResourcesInUseForRoute_Routing. This discussion describes a similar problem, but the solution was to just put the reference clock to the slave device, who had no other tasks running on it, so what mine does.

Is there way I can synchronize the clocks of refernce without interfering with the digital I/o?

Thank you!

PS: My application is in C++.

The reference clock is really a lower-level component that is shared by all resources on a given device. All tasks on a given device must use the same reference clock. So if you use DAQmxSetRefClkSrc for a task, you can use it to set the same value for your other tasks.

Best regards

-

synchronize the clock of your computer with your local time?

synchronize the clock of your computer with your local time?

Windows 7 must be configured by default to set his time using windows.time.com as an NTP server. Double-click the clock in the taskbar, and then select the time tab Internet. A source of time NTP is configured?

Brian Tillman [MVP-Outlook]

-

I don't want my Virtual Machine to synchronize the clock of the host

I'm using VMWare Workstation 7.00.203739

My PC is Windows XP SP3

My Virtual Machine is Windows XP SP3

I don't want my virtual machine is synchronized with clock 'the real machine', then reading here and there I put these lines in Windows XP SP3.vmx

tools.syncTime = "FALSE".

Time.Synchronize.continue = "FALSE".

Time.Synchronize.Restore = "FALSE".

Time.Synchronize.Resume.Disk = "FALSE".

Time.Synchronize.Shrink = "FALSE".

Time.Synchronize.Tools.Startup = "FALSE".

However, after 30 minutes I work inside the virtual machine, I see that comments clock synchoronizes with the host country.

What have I forgotten?

Thanks for your advice

When this occurs after the virtual machine is in place, for a while, I guess that you have activated the service 'Windows Time' - it disabled via services.msc

___________________________________

VMX-settings- Workstation FAQ -[MOA-liveCD | http://sanbarrow.com/moa241.html]- VM-infirmary

-

Synchronize the clocks of PCI I / AO with multiple AI in parallel

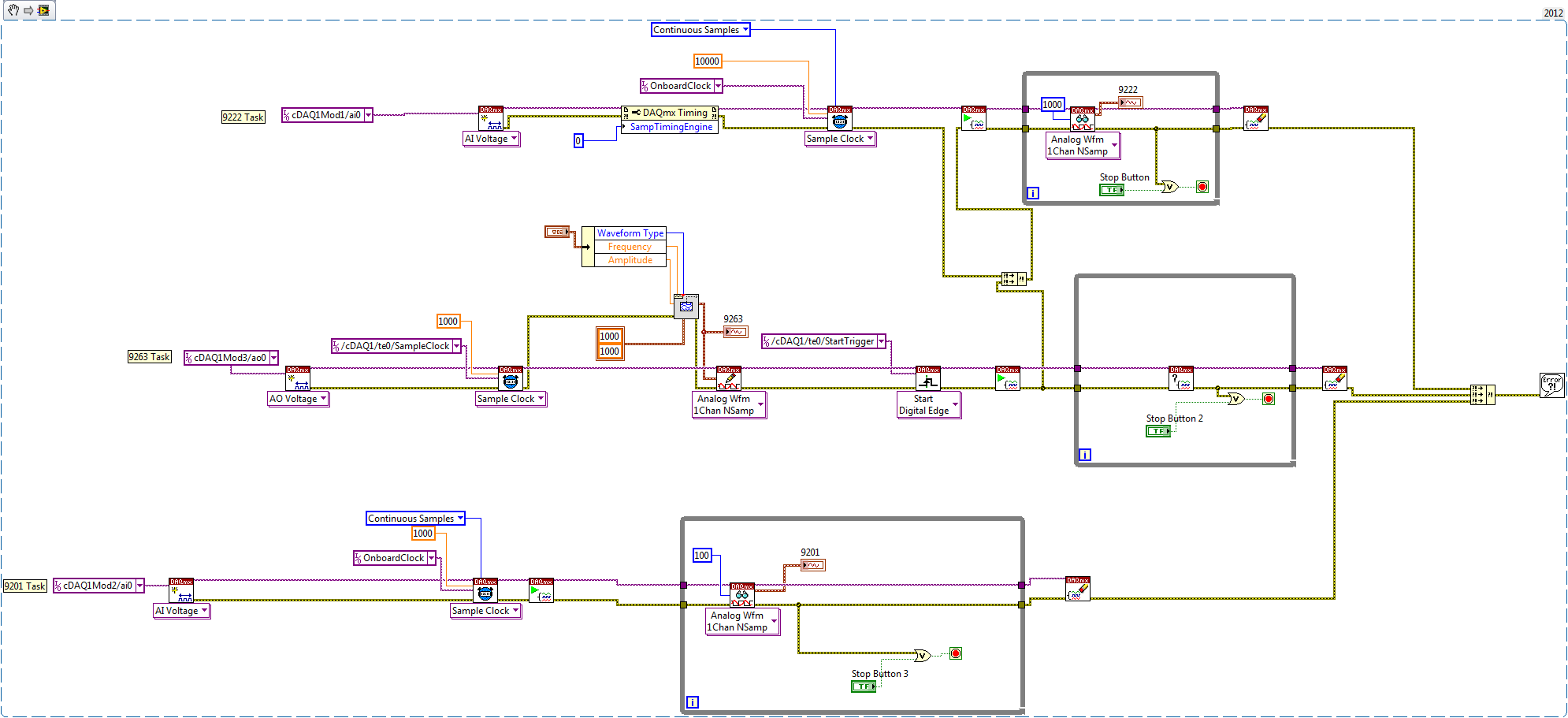

I want to synchronize my HAVE and AO to run on the same clock and have my AO beginning with a relaxation from the beginning of IT. All works beautifully except when I have another process running in parallel. I use the cDAQ chassis 9178 and I have a low resolution HERE (9201) that runs in the context of monitoring for alarm conditions. I want to run in parallel to my DAQ vi.

In the vi DAQ begins AI (9222) and triggers the AO (9263), the AO clock is referenced to Dev1/AI/SampleClock and start trigger is referenced to/Dev1/I/StartTrigger

The problem seems to be that if the 9201 collects data HAVE then my AO is actually running at that frequency of clock instead of the 9222 (since the 9201 is always launched in the background, the OD has seen this first)

How can I tell the AO (9263) to run with the AI 9222 clock and trigger rather than the AI 9201? I think that I do not understand how the chassis works with modules...

Gracias.

Hello Telleurium,

The quick answer is call specifically on the timing engine and relaxation of timing engine. This will ensure that the 9263 and the 9222 are synchronized. Please take a look at the example below what I call specifically on the timing engineof teo.

A more detailed explanaiton of what happens is that the 9201 seizing first the timing of AI engine (which means that it is now associated with the AI and AI trigger sample clock) so you see the 9263 is synchronized with the 9201.

Best regards

Izzy O.

Technical sales engineer

National Instruments

P.S. on further notice, that it would probably be easier to point the 9201 on a different timing engine.

-

Synchronize the FPGA clock for clock RT?

Hello

I use a sbRIO-9612. Data are acquired for several weeks, and the problem is that the clock of RT of derivatives. I found a technical document to synchronize the clock of RT with SNTP server:

http://digital.NI.com/public.nsf/allkb/F2B057C72B537EA2862572D100646D43?OpenDocument

But I do not find anything on the FPGA clock. My data are acquired by the FPGA, my question is: How can I synchronize my FPGA clock with my RT clock or the SNTP server? (this is probably a stupid question, but she clearly explains my problem) SbRIO is suitable for my needs? Should I waive any 'acquisition of FPGA based' and use a different hardware architecture to perform data acquisition synchronization?

Thanks in advance for any help.

Julien

Hi Julien,

Take a look at "RT masters FPGA synchronization Example.vi" on the FPGA Timekeeperpage. There's a Subvi, which uses a timed writing periodically present to the FPGA so that the FPGA can have a domain time synchronized with respect to RT if you have questions about this example, try to publish to category of Discussion of the project.

-Steve K

-

[FlexRIO] Start-up to synchronize several clocks sample

Hello

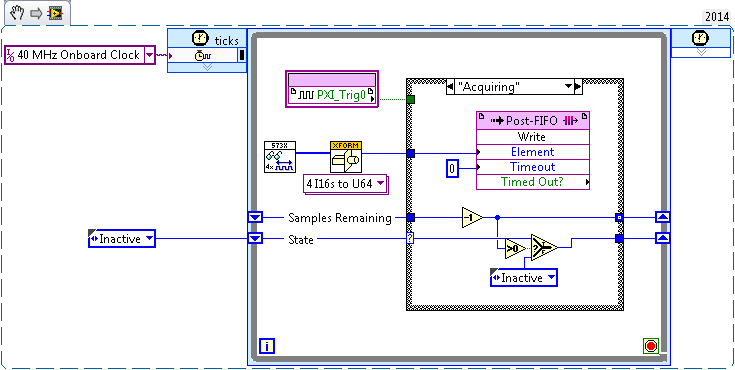

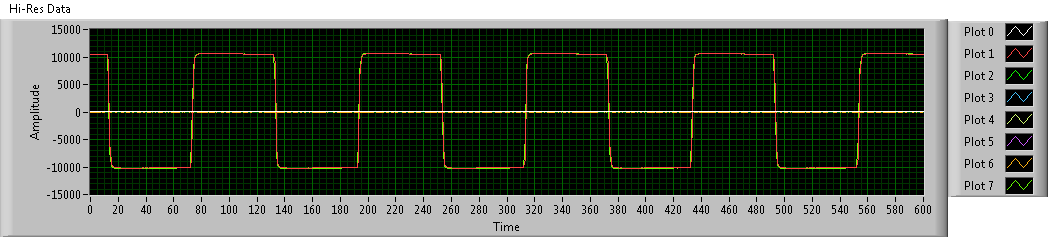

I tried before, two different (SMU-7962R + OR-5734) FlexRIO card reading in the '40 MHz Onboard Clock' or 'PXI_Clk10' areas of clock. Trigger has been achieved by simply looking for a rising edge on PXI_Trig0:

This produces seeds, but there has no inclination (or constantly tilt at least) between the two FlexRIOs - I sent a pulse train duplicated in the two cards, and the triggered-acquired waveforms were still at the stage:

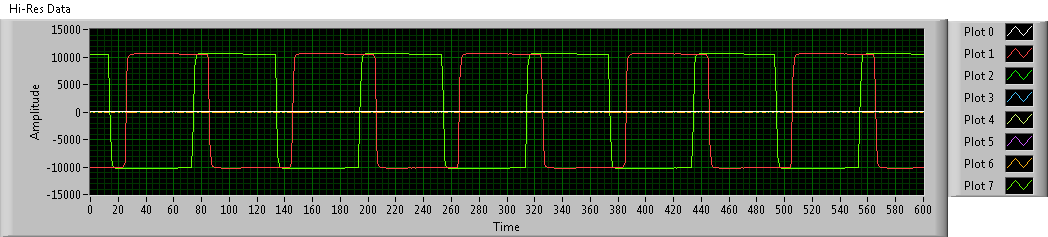

To avoid problems, I went to examples of clock (IO Module clock 0). Unfortunately, the clocks of the sample between the two FlexRIOs had nothing in common, so the acquired waveforms have been is out of phase. Worse still, the phase difference changes with each release:

Looking at the implementation of the library of the synchronization of the FIDL, the classic technique for synchronization of multiple cards FlexRIO seems to be built around synchronization master-slave (my observation is correct?). I was wondering: is there a way to simply share a sample clock shared between cards (like what the 40 MHz embedded clock was doing before), as described in http://www.ni.com/white-paper/11369/en/ ? (I think I understand the disadvantages associated with sample clock synchronization, but I'm willing to try for now).

Thanks in advance!

Hi JKSH,

Page 9 of the Manual 5734 described the different synchronized methods that can be used the 5734. You can synchronize either sample clock of each module to a clock available through your chassis backplane (for example, DStar_A) by allowing the IOModSynClk in 5734 properties (available the Details category) or use an external clock through the Clk port on the module. Activation of IOModSyncClk is probably the best approach and will lead by examples of clock on each module e/s being PLLed on the clock of the town - which must synchronize the clocks of the two sample together.

Let me know if you have follow-up questions.

Kind regards

-

Problem with congregate and synchronization of clocks

I have connection problems of my laptop and desktop at a home group. When I look at the clocks, the office is always a few seconds faster than the laptop and somewhere I read that the clocks must be synchronized for the home group to work.

What's odd about all this, I just did a fresh install of Windows 7 on the laptop a few days ago group home worked fine for about a day, then he stopped.

I tried to use the time Internet sync to synchronize the clocks on the desktop and laptop. I used 4 servers of different times, but whenever the real-time is a couple of seconds between the office and cell phones. Nothing I've tried will get them to sync.

Any help that you could give to fix this problem would be greatly appreciated.

Hi Profrock,

First of all, try to run homegroup troubleshooter built into windows 7 and check if it helps solve the problem of residential group on your computer. Access the link below and follow the steps to run the troubleshooter in homegroup. http://Windows.Microsoft.com/en-us/Windows7/open-the-HomeGroup-Troubleshooter

If the problem persists, you can try to start the computer in safe mode with network and check if you can access the homegroup. To boot to the desktop in safe mode with network keep tapping key F8 during restart. Once you see the option to start it in safe mode with select network and press ENTER.

Access the link to learn more about how to start the computer in safe mode: http://windows.microsoft.com/en-US/windows7/Start-your-computer-in-safe-mode

You can also try to temporarily disable the security software of the computer and check if you can access the homegroup. If you are able to access, you can contact the manufacturer of security software and check if you need to change the settings. Later, re-enable the security software.

Also note that there is no case of residential group doesn't work not based on the clock.

I hope this helps. Let us know the results.

Thank you and best regards,

Srinivas R

Microsoft technical support.

Visit our Microsoft answers feedback Forum and let us know what you think.

-

Series LV examples do not work with the series via USB unlike HyperTerminal

Hello

I have a camera with that one way to communicate - series via USB. With Hyperterminal, it works as expected, but none of the examples of series that come with LV gets no response. When highlighting the execution, Write function will return no error (but apparently not send anything - no visible reaction from the device), and then the Read function gets nothing (late just then, judging by the experience with Hyperterminal).

Would be grateful for any suggestion useful.

Thank you.

Indeed, they have been included; as example intends to send "* IDN? \r\n", \r\n were taken directly from there.

-

How to generate the clock 8,192 MHz on the labview FPGA 7854R series card?

Hello

I use the NI PXI-7854R series card that has 5 FPGA from Xilinx Vertex on him. I'm drifting clockwork 8,192 MHz to 40 MHz on board the FPGA clock. But he ended up giving me a single clock 8 MHz. is it possible to access the PLL located on FPGA Xilinx?

Concerning

If you are familiar with VHDL you can make your own "component-level IP' (aka CLIP) with a PLL Xilinx inside. There are topics for help and examples of how to define a CLIP. Here's one that shows how instantiate a DCM (similar to a PLL) in a CLIP:

http://zone.NI.com/reference/en-XX/help/371599F-01/lvfpgahelp/fpga_clip_clock_ex_code/

-

What is the relationship of synchronization between the input MUX and the clock to convert DAQmx

My application requires both long settling for the analog input. I can slow down the clock to convert in order to increase the interval without but I would like to learn more about the internal synchronization and synchronization between the switching of input MUX and the clock to convert. Data acquisition is USB-6225.

Thank you

Neville

wet'nwild,

You have reason in the observation that hold all the impulses of the event happening 180ns after convert rising edge clock, regardless of the period of the clock to convert.

This is the process:

1. the clock Convert generates an impulse to start the ADC conversion.

2. a period of time (in your case, 180ns) after the clock pulse to convert, the complete signal hold impulses. This indicates that the data are "required" by the Active Directory Connector. It is now OK for the MUX switch to the next channel. It is important to note that the ADC conversion is not complete when the pulse hold full occurs.

3. at this stage, the MUX will pass and the device will wait for the next clock pulse to convert for the start of the next conversion.

In summary, this means that when you change the period to convert clock signal, the complete signal hold flashed always the same fixed amount of time after the edge of signal clock convert. The complete signal Hold'em is not a good indicator of break-in; the width of the period to convert clock must be waiting time indicator (which looks you determined you're previous posts). A good application for the signal keep complete would be for an application where there is an external multiplexer and the multiplexer needs a signal indicating that it is OK to switch the inputs.

I hope that helps clear up any uncertainty that you have about how it works!

Kind regards

Aaron

-

Active Sync iPad ssl Client certificate

How do I configure the iPad2 to synchronize the iPad-Mailclient with Exchange 2010 via Active Sync using the certificate SSL client and name of user and password?

Hi Ewoki,

Your question is more complex than what is generally answered in the Microsoft Answers forums. It is better suited for the TechNet Exchange forum. Please post your question in the Forums TechNet in Exchange Server.

-

synchronize the computer's clock, failure

My computer clock will not synchronize what can I do?

It has been my experience that if too far, the clock is not synchronized that the automatic update will often fail. Manually set the clock, then automatic update again. It should work this time.

-

BlackBerry Smartphones Can I synchronize to a server MS Exchange via the Internet Service of BB?

I am looking to buy a "BOLD" to synchronize my email to work thanks to an MS Exchange Server. Since it is also a personal phone, my company is going to make me pay the license fee to connect via the BB Enterprise Server. My question is if the Enterprise Server is the only way to synchronize emails from MS Exchange Server, or can I synchronize my email, contacts, calendar, and tasks using Internet Service, BB?

Thanks for the help!

You cannot synchronize your emails without Exchange Server.

To synchronize the calendar, contacts and memos, you don't need the Exchange, only with BIS is sufficient.

-

Synchronize the ctr1 at ctr0 (generate outputs freq) via the signal of export

I need help to configure the output channels of meter on my card pxi-6723. Here's what I'm trying to do:

-have the possibility to synchronize the ctr1 exit toward ctr0. Note: ctr1 must begin on edge increase or decrease output ctr0.

-be able to change idle, freq. etc for each of these outputs

A sample that I worked on is attached. It works except the ctr1 output is trolling by cycles of 1 to 1.5 (according to a State of rest, edge selections). This delay is due to me having to put the slave (ctr1) task run after the masters. Note: The reason for this was the task of enforcement of crt0 (master) was the origin of the false triggers when exporting the trigger signal.

Its there a way of software trigger ctr0 OR delay its release until both (ctr0 & ctr1) 'perform tasks"have been launched?

Hi groz,.

I have not tried, but I expect the following sequence to prevent false triggers:

DAQmx control Task (ctr0 task, Commit)

DAQmx Start (task ctr1)

DAQmx Start (ctr0 task)

Principal ctr0 has it on its state of rest.

Also, I think you can do this trip without using a PXI_Trig line. To Start.DigEdge.Src the ctr1 task, specify "Ctr0InternalOutput". (To make the Terminal Ctr0InternalOutput appear in a Terminal of DAQmx e/s constant, right click on the constant, select "I/o name of filtering...) ("and put a check mark next to"Include the advanced terminals").

Brad

Maybe you are looking for

-

I just want to know where to find the information/instructions about the feature in gmail tasks.

-

I'm looking to upgrade my SDRAM on my iMac early 2009. I'm comparing sources and I was wondering if anyone has experience and/or recommendations with Axiom and Crucial manufacturers that you can share?

-

27-n140nz Pavilion: Crusher 4 g-motherboard - number of SATA connectors

Hello does anyone know how SATA connectors there are on the card mother 4g of Crusher? Change the disk hard for one ssd but would like a second internal drive if possible while maintaining the optical drive... see you soon Andy

-

There were 68 'important' or 'recommended' updates automatically installed since 03/09/09. What concerns me, is the amount of disk space I'm dedicated to these updates. Replace the previous updates or are they cumulative? How do I know what to do th

-

When I select the control panel user accounts, it is empty, no account showing, not even mine