Use of FPGA references in a class

Hi all

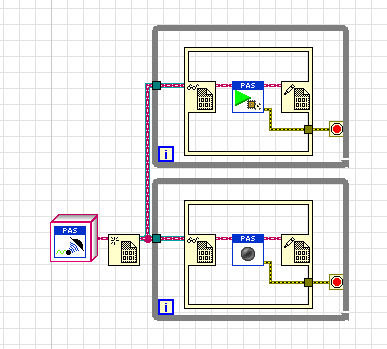

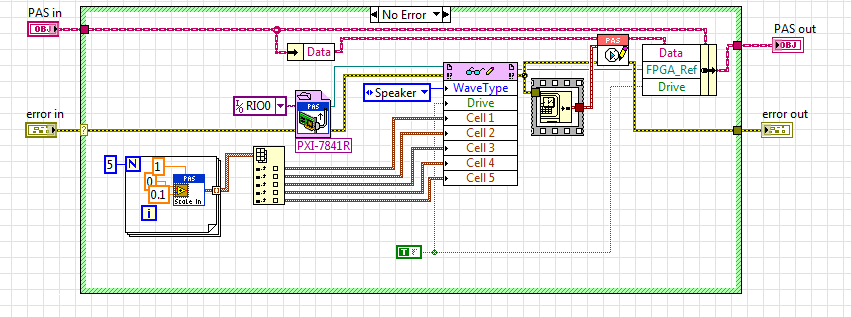

I found a work around for a question I had but it's not quite as elegant as I would like, so I thought I would post this question that I have. I am running a RT system on a PXI chassis. The system responds to commands from the user sent via TCP/IP. Much of the architecture is based on object-oriented techniques. In addition to the RT system, I have a card of the R series that I use for DIO and AO. For communication between the two loops (one that queries for the interaction with the user and the other that runs continuously measures), I use a data to encapsalate my main class reference. (simple example below)

In the main class, I maintain a reference to the FPGA session which I ungroup when necessary to change the settings on the FPGA. The reference is bound to strictly control type def' ed. I can manage to open the session for the FPGA (upper loop; vi below)

However, when I try to access the FPGA session open in the loop at the bottom, I get an error saying that the session is not open or is not valid.

I know it can be difficult to understand (I show the full set of screws, but they are large enough so those simplified should be enough), but someone has any ideas on this topic? I've linked the reference to a def of strict type for reference FPGA as for 2009, but I still get this error. Maybe there's something that I am missing?

Any thoughts would be much appreciated.

Peace, Matt

OK - I'm sorry. It works fine when group you in a class and use the reference data as described above. I came just to be able to close the reference where I expect it.

Peace, Matt

Tags: NI Software

Similar Questions

-

Can I use an XControl reference in a class?

LabVIEW help stipulates that "a private data control cannot contain an XControl or an XControl refnum", while previous reviews have shown that the problems occur in a built application, but not in the development environment: http://forums.ni.com/t5/LabVIEW/X-Control-Distribution-Bug/td-p/1132058 this question seems to have been given the CAR #210033 http://forums.ni.com/t5/LabVIEW-Idea-Exchange/Allow-X-Control-X-Control-Reference-as-a-Class-Data-Me... with the note that it only covers the XControl reference , not the XControl himself, as a member of class private data.

I just tried a simple application with a XControl reference in the private data of the class, and it seems to work without error in the application built in development (2012 f3 (12.0.1f3) SP1 32-bit LabVIEW). I have looked through the last few lists of bug fixes and cannot find this CAR in one (2011 or 2012), even if the documents say they list only a "subset".

Can anyone confirm if the #210033 CAR has been fixed? I don't want to go too far down this path if she will introduce problems at some unknown point.

According to the database of the CAR, this CAR has been corrected in LabVIEW 2010.

-

Open FPGA references change to no. target when compiled with executable in time real start

Hello again you useful forum fans! I have a problem that I hope someone can give me a hand with.

I have a project that has a Windows component and a component of the target in real time, that are running on a hypervisor type NI PXI-8110 system. Communication both sides between them using shared variables.

On the real-time side, I have four FPGA targets who are reading and writing various analog and discrete inputs and outputs. I several periods loops which opens a reference to one of the FPGA targets during the first call, then pass this reference in several subVIs that read and write to panels prior to the FPGA. The loops the FPGA reference thus made available and reuse it in the next iteration through the shift registers. Each FPGA target has only a single reference open to him. One of the loops is using the FPGA reference directly and does not pass it in any subVIs.

It all works very well in the development environment, I can read and control inputs and outputs FPGAS via the front panel of the application of the side Windows. It also works very well if I start the game real time in the development environment, and run the code of windows as a stand-alone executable file.

However, when I compile the code in real-time in an executable startup and deploy it to the target, it does not work. I enabled debugging on the executable, and when I connect to it via the operation-> debug executable in the menu, I see an arrow broken at execution. Further investigation shows that each of the four open screw reference FPGA is now empty, the text under them is "no target" and the thread for reference on their part to my first Subvi is broken. I need your help to understand how to operate as it does in the development environment.

I followed the instructions of these two knowledge base articles to compile and download the bitfiles FPGA on the FPGA target and execute on start or restart:

http://digital.NI.com/public.nsf/allkb/39795847AC67296D862575FB0046944F

http://digital.NI.com/public.nsf/allkb/BC513C2A0DC29C89862574BF0002B0B9?OpenDocument

Open FPGA reference screw are configured for the FPGA to build specifications that I created for each target in the LabVIEW FPGA project.

I called technical support, NO phone, and yet were able to determine this one out, so additional "brownie" points if you do!

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.Please let me know if you have any ideas regarding what is happening! I appreciate it.

Jon,

I'm always up for the challenge. Have you tryied recompile the FPGA VI that accesses the RT VI? I also suggest to try and open the bitfile instead of the FPGA VI. You run in dynamic mode (this is not a suggestion, it's just a question)? There is no difference if you try to open the FPGA VI reference outside the while loop, then past the reference to use inside the while loop without shift registers, then close the reference to the FPGA VI outside the while loop?

Let me know if these suggestions makes no difference.

-

No screws listed for option VI in 'configure the FPGA reference open '.

I have a cRIO and I used the function reference FPGA opened to load a bitfile by specifying the name of VI. It worked very well.

I've been compiling all day, and I just deleted a control and then changed to a DMA FIFO data type. When charge and ran the FIFO calls returned an error. So I tried refreshing the specification of VI, but now when the dialog box is displayed, there is no listed screws.

No idea what's not here.

(1) I put comment the FIFO when I compiled (forgot to turn it back on to the it); This is why the error occurred. Oops.

(2) I still don't know why I could not navigate to the VI, but I was able to drag and drop.

-

I'm learning the FPGA. I have a few simple question.

1. I tried to use the open FPGA VI reference configuration. I selected the file bit on my PC, and I checked the run option VI FPGA. Why I select the bit file on my PC? The file bit is not supposed to be on my FPGA target?

2. once I open FPGA VI reference, I fed to an invoke node, but it won't. It is said that the sources and sinks have given different type, but he also says that they are both FPGA interface. I'm a bit confused.

Please see attached picture.

jyang72211 wrote:

1. I tried to use the open FPGA VI reference configuration. I selected the file bit on my PC, and I checked the run option VI FPGA. Why I select the bit file on my PC? The file bit is not supposed to be on my FPGA target?

Not quite sure what you're asking here. A FPGA target has no local storage. When you open the FPGA VI reference, LabVIEW support the bitfile on the FPGA. The VI that calls open FPGA VI reference is one that opens the bitfile, the bitfile must be local to this VI (in this case, on your PC).

jyang72211 wrote:

2. once I open FPGA VI reference, I fed to an invoke node, but it won't. It is said that the sources and sinks have given different type, but he also says that they are both FPGA interface. I'm a bit confused.

The FPGA reference on the Panel before you must match the configuration of the reference that you're passing to it. Right-click on the front panel control and configure the FPGA reference to point to the same bitfile you open. Better than that, bind the FPGA VI reference open to a Type definition and the place that the category definition on the Panel the Subvi front. Note that if you do this, it works at the back of what you would expect. Update of the baseline open FPGA VI changes the type definition; you never directly change the type definition.

-

Several loops of RT; A single FPGA reference

I have three loops using the same reference FPGA.

Loop 1 - reads most of the data in the FPGA for display on the HMI

Loop 2 - using the information made available to the loop 1 as well as some additional data that is read from the FPGA to perform the functions required by the HMI controls and writes for the FPGA.

Loop 3 - uses data from Loop1 as well as additional data read the FPGA to run commands fuctions and wrote security for the FPGA.

My questions are:

The FPGA Refence points to a single memory block where all three loops are looking at the same data?

I need on While loops shift registers to keep data updated correctly?

I need to run the three sons reference FPGA close While loops to close the reference correctly?

Yes. N ° N °

I assume you mean wire reference FPGA entering a node that reads the FPGA reference you speak or write in the Panel control or indicator that is part of the VI running on FPGA.

-

Good way to stop and run again a FPGA reference

Hi guys!

I have some problems when I try to stop, and then rerun an FPGA vi, I explain.

I have two DMA FIFO to send data to the FPGA of the CPU and the CPU for the FPGA. When it receives data, the FPGA treats them and sends them to the CPU, and according to the result of the CPU does something. For example, it can be turn on LEDs or to rotate a motor continuous.

But to do these actions, I have to use a "personality FPGA", i/o pins and LEDs appear to be managed by the FPGA core. So I have to close my reference vi FPGA in charge to receive data from the CPU, make my power on LED and then after raise again my FPGA VI once again, if I don't do LED blink or stay without effect rotation motor... But close and start again the FPGA VI creates problems when running, especially for the previous reading on the FIFO DMA awaiting... I tried to intercept errors on the FIFO to restart the FPGA VI with a good time but nothing... I am lost and I think Miss me something, concept, or something else.

I can't share my code because I work for a company, but I would like to know if you have VI with this type of structure: a FPGA reference that must be stopped to allow interaction of material with the FPGA default personality then run again, all with good timing...

I hope I'm clear, but if it is not the case, I can rephrase if necessary.

Thank you very much for the help!

Afghow.

I do not understand why you need to change the bit file is loaded in the FPGA. Why you cannot add code that handles the inputs/outputs to your FPGA processing? Why do you still need to send data to the host (CPU)? Just having the process FPGA data and change the output directly.

-

FPGA reference questions between the station development and execution? 63195 error code

I will do my best to describe the problem, I was see. Note, I tried a few other messages that kind of touch on my problems, but they never seem to have a definitive solution.

Background-

I have 3 screws:

VI 1) opens / runs the bitfile FPGA reference and stores the reference to a global file so that I can call the reference of other screws I need to do this as opposed to the opening of a new reference because I use the FPGA for digital communications and it adds about 100 ms to to open a new reference whenever I need to read/write in the target FPGA to host (100 ms are long in the) digital world!). Some people use Shift Registers. I finally called my whole army FPGA screws of TestStand to run a test automated, so it was easier to break up of my functions for open/close/read/write.

VI 2) called the global reference of the file for FPGA, then going to a read/write node to change the settings of the target, then passes the reference out of the node back to the global reference of the file read/writable

VI 3) calls close reference FPGA and the function is passed the global reference of the file.

Question-

I understand not why this method works fine when I run either of TestStand with station options defined for the development (not running) mode or when I open VI which calls these 3 screws individually in sequential order but IS NOT working when I try to run these screws individually (Run VI 1 - open-> write Ref to the global reference of the file-> Run VI 2 - read global file reference-> playback control function / writing-> error-63195) or when I have run in the same sequence TestStand but together with station for execution options. Maybe I need to change the TestStand sequence to load all the modules at startup?

Why the reference becomes lost when global failover between development and execution and why labview cannot drop keep the reference stored? Is there a work around?

Finally found a solution. I do not understand why it is necessary during the reading of the FPGA and not what writing (in fact I do not understand why it worked at all) but I ended up changing the properties of the step in my TestStand sequence for the step calling my DTL_READ.vi to be properties-> Run Options-> Unload Option-> "Unload after executing the step. That seemed to do the trick to get my test TestStand sequence to work in runtime.

I still don't understand why this was not required when you run the same sequence in the design environment and why it is not when I call my DTL_WRITE.vi.

The DTL_READ.vi and the DTL_WRITE.vi pass the parameter labveiw global.vi 'Reference FPGA VI"of a node in read/write. I don't know if the root of the problem is in my host TestStand and LabView FPGA VI...

Thanks for all suggestions from you guys! I'm happy I work but I am still confused by the solution.

-

Open FPGA reference fails to run

Hello

I apologize if this is covered elsewhere; I found nothing relevant.

I have a fair size RT application that calls the vi FPGA reference open as the second point during initialization. The FPGA is compiled and worked fine before with a simpler application of the RT. When you run the program I probe the wires of the error as well as highlight the execution and the program is just stuck on that vi.

The vi is configured to point to the FPGA vi in the project. I tried pointing to the bitfile and the same behavior occurs.

The goal of the RT is a sbRIO 9631 with NOR-RIO installed 3.5.1 (without scan interface). I reinstalled it during my troubleshooting.

So with that, any suggestions? Otherwise, I can be on the phone with TOMORROW and will post whatever I learn.

In the same vein, it would be possible that the user interface is simply not updated because you use too many resources on the RT controller. Especially with probes and highlight the running, the transformation of the network might be causing a problem. In the measurement and Automation Explorer or distributed systems manager, you can view the sbRIO here memory/CPU usage:

http://digital.NI.com/public.nsf/allkb/8C7B655978C8ADFB86256AAE004AD261?OpenDocument

I would try also to Flash the sbRIO then reinstalling the 3.5.1 drivers on the device and try again. If you had a different version on the target as 3.5, it may have been a fix that resolves this.

Finally, try to have the FPGA vi to run when load/run when starting the crio by following these KBs:

http://decibel.NI.com/content/docs/doc-3076

http://digital.NI.com/public.nsf/allkb/BC513C2A0DC29C89862574BF0002B0B9?OpenDocument

Thank you

D Smith

-

Data transmission between screws using call of reference without actually executing the vi

Hi, I was wondering if you can pass data between the screws by using call of reference without actually executing the vi (ie: not having the façade appears during execution). Is this possible?

While I'm here I might ask as well on the transmission of data between the screws I'm trying to pass a flag to a vi value to another. Because of the way the program is setup, I can't wire this value directly. Y at - it another (fast/efficient) way to pass data between two screws during execution (other than shared variables). For what it's worth this application will be built into an executable file, so data transiting will have to work for it as well.

Thank you

Vlad

Vlad P wrote:

While I'm here I might ask as well on the transmission of data between the screws I'm trying to pass a flag to a vi value to another. Because of the way the program is setup, I can't wire this value directly. Y at - it another (fast/efficient) way to pass data between two screws during execution (other than shared variables). For what it's worth this application will be built into an executable file, so data transiting will have to work for it as well.

You have the choice:

- shared variables (as you mentioned)

- global variables

- queues

- notifiers

- control references and properties of the value

- action motors

- ...

Tell us a little more about your applications. What should do?

-

Use an external reference to AOchannel

Hello

Using a device of 6259, I try to generate two analog outputs in a task. However, one of the outputs analog must use an external reference (using APFI1 for example).

The problem is that I can't find a way to indicate the external reference to a single channel.

Even though the documentation says that the AOChannelCollection was a member of the public "Item", this is not the case.

According to the manual of the 6259, it must be possible to assign the internal and external references per channel: "you can use one of the OD <0..3>signals as the AO reference for a different signal of AO. However, you need to externally connect this channel to APFI 0 or 1 APFI. ' - Manual usage of the series of the M, 5-2.

Thank you.

Hey,.

I tested it with the following code by using two channels, each with a different external reference:

myTask.AOChannels [0]. DacReferenceSource =

AODacReferenceSource.External;

myTask.AOChannels [0]. DacReferenceExternalSource

= "/ Dev3/APFI0";

myTask.AOChannels [0]. DacReferenceValue =

10.0;

myTask.AOChannels [1]. DacReferenceSource =

AODacReferenceSource.External;

myTask.AOChannels [1]. DacReferenceExternalSource

= "/ Dev3/APFI1";

myTask.AOChannels [1]. DacReferenceValue = 5.0;Hope this helps,

Christian

-

Cluster for the FPGA reference constraint

I have a cluster of clusters. One of the internal piles went 25-29 items, but I forgot to update several of my Subvi reflect. I remember before when I did, I got a broken line not executable VI, but now the result is a constraint. You can really force a cluster with multiple items to a cluster with fewer items? My outdoor group consists of some FPGA with clusters of register references.

Hi Adams,

FPGA reference is the special data of type "FPGA dynamic reference", which includes a cluster of records, elements, and associated with the referenced FPGA personality FIFO dynamically. Dynamic data types do not follow the same rules of coercion expected of them a defined data type statically to follow. The dynamic nature of reference FPGA son allow wire any FPGA reference in the entry of an order of read/write, regardless of whether the control of read/write was created explicility for the FPGA reference. This makes it much more practical FPGA programming.

-

Can I use data value references with a functional overall?

Can I use data value references with a functional global? I am trying, but it causes problems: I run the attached VI with "new DVR" selected. Then I run it again with "return array" and I get the error 1556: "The reference is invalid. This error might occur because the reference has been deleted." It seems to have forgotten the DVR, but I thought it should be stored in the shift register. Another odd thing: In my VI, if I try to connect the wire shown in "something strange", then the type changes (from U16 array to DBL), i.e. it doesn't recognize the type referenced by the DVR. I want to pass a very large 4-dimensional array between parallel loops with a functional global. To avoid memory problems, I want to use a DVR and in-place element structures. If that's not allowed in Labview, I will try passing it through a user event or notifier. Any problems with those alternatives? Thanks.

I received a response from an engineer applications OR on this subject, and it seems that it is perhaps a problem with Labview. They are working on it, so I'll go ahead and close this discussion.

Thanks for the help,

Allan

-

Trouble when using the FPGA to record data on PDM

Hello world

I encounter something strange with the use of FPGAS to save data to the disk. I use 4 channels and allows saving data PDM. I use 4 different graphs to observe each channel and no bad thing. But when I check the data stored in PDM, they are not saved in the order that they are supposed to be. Each column in the PDM should represent 1 signla of a channel, but the result shows that the data seems to fill a single column, then another. I do not understand how it becomes like this. I have attached a few photos for your information.

The data of the FIFO.read must be 1 d table, right? So when it passes through the form 'table' in my VI, it should become a 2D of the 4 column table. Each column represents the data for each channel. I don't see any problem with this Vi. Why PDM data are not saved in the right direction?

Thank you

In my opinion, that you simply return your dimension sizes. The number of rows should be 500 and your number of columns must be 4.

-

Impossible to check the FPGA reference with "not a number/path/Refnum?

How can I check if an FPGA interface refnum is valid? It seems (LabVIEW 2009) that "Not a number/path/Refnum?" always returns true when connected to the output of open FPGA VI reference. I write code that needs to be able to run without an FPGA for testing purposes, so I wrapped all calls to the FPGA in a case structure that I thought would run only if the FPGA reference is valid. Turns out that they run ever, even when the FPGA reference is valid (probe shows it has a numerical value, and the FPGA VI is running). I guess it's sort of similar to semaphore and appointment of references that have their own special function to verify the validity, but I do not see such a function for FPGA. I have to cast to int and check if it is not equal to zero?

Maybe you are looking for

-

Upgrading RAM on Satellite M40

I have a Satellite M40 and I can't seem to understand where is the second location of the RAM upgrade Thank you

-

Satellite M45-S355 and DVD burning

I have a Satellite M45-S355 laptop and never tried to burn DVDs so far. I know it's a rug * a pilot/burner UJ - 831 s.I am not able to find any DVD x 16 for their speed. How can I burn on these types of DVDs? When I try to format a disk, etc., the co

-

Motherboard replacement for a Presario all-in - One SG2 - 210UK

Wonder if anyone can help solve the apparently impossible task of stock up to a card mother SP #619968-001 Privas MC11 for my SG2-210uk Presario A-I-O... HP UK have quoted more than £400 for the repair of a machine of at least 2 years (dead graph). I

-

Need help to update BIOS on Satellite L30-113

Hello I just downloaded the latest update of the BIOS for my Satellite L30-113 (PSL 33) and I was about to install when I remembered that I actually downgraded to Windows XP(this notebook is originally with WIndows Vista).My question is it will produ

-

Error 80070643 Windows Update the 13 April 2010. Seems to be the update to the office only.

The Windows update 04/13/2010, problems since then it never ends the Office updates. Download KBN 981715/981433/980470,980729 start install and error 80070643. Whenever I start a component Office, then it goes to the Windows Installer box takes 15-30