Optimisation of the FPGA pls help

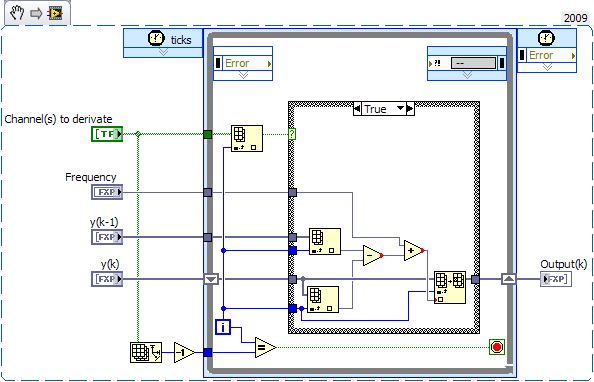

Hello, I am a new player in the programming of FPGA and LV. I've set up a project, but using FPGA is more than 150 percent too high. I've read a lot about optimization, but I think that I always do anything much wrong. Please check my code and tell me where the dog is buried. I joined only a few VI.

Please download the project as a zipfile, directly to this forum. I, at least, will not download files from unknown foreign sites.

charlie87 wrote:

at nathand : I do not understand the idea of making SCTL acting as the loop. Do you have some examples?

I thought that Hight Throuthput math is better then standard digital mathematics. If this isn't the case, please explain.

I need feedback node to store the previous value to the derivation and integration where I now the difference. I know no better way how to do it. Do you have?

Comment nodes are fine for this purpose, I was just trying to understand if there was a mathematical need for them or if you were trying to use them for some sort of pipelining.

The math broadband are not necessarily better than the standard numerical calculation. Please see Help for "the use of Math functions broadband. This document: "National Instruments recommends to use the LabVIEW digital unless you need the benefits that offer the features high-speed mathematical."

Here's how you can implement a loop as a single cycle timed loop. Will not compile on my machine, although - you need to solve problems with excessively across the point values fixed first, as dan_u noted.

Tags: NI Software

Similar Questions

-

HP pavilion h8-1230: how to access the bios pls help

How to access the bios and I got windows 7 but to give birth to windos 10 with the thing free upgrade I got Pls Help

Immediately after pressing the power button to turn on to start by pressing the F10 key.

-

FSX delux and aceleration

Hello

The question you posted would be better suited in the Flight Simulator community site.

You can see the site:

http://www.Microsoft.com/products/games/FSInsider/community/pages/default.aspx

-

After the union, I want a row by omitting null Pls help

Sorry, I changed the outputCREATE TABLE T (chr1 VARCHAR2(20),chr2 VARCHAR2(20)) INSERT INTO T VALUES('XX','YY'); INSERT INTO T VALUES('AA','BB'); CREATE TABLE T1 (VAR1 VARCHAR2(20),VAR2 VARCHAR2(20)) INSERT INTO T1 VALUES('A','B'); INSERT INTO T1 VALUES('X','Y'); SELECT CHR1,CHR2 FROM t union select var1,var2 from t1 OUTPUT A B AA BB X Y XX YY IS IT POSSIBLE FOR ME TO DISPLAY CHR1 CHR2 VAR1 VAR2 XX YY A B AA BB X Y

Pls help

S

Published by: a beginner Sep 9, 2010 12:24 AM

Published by: a beginner Sep 9, 2010 12:31 AM

Published by: a beginner Sep 9, 2010 12:40 AM

Published by: a beginner Sep 9, 2010 12:42 AM

Published by: a beginner Sep 9, 2010 12:42 AMSELECT chr1, chr2, var1, var2 FROM (SELECT chr1, chr2, ROWNUM rn FROM t) a, (SELECT var1, var2, ROWNUM rn FROM t1) b WHERE a.rn = b.rn-Kaila Manu

-

I get this message when I turn my macbook pro on "there is no set of application to open the document"stream_000b.strings ". "How can I get rid of him. pls help

Check preferences system/users and groups to see if this item is in your login items. If so, select it and use the sign less to remove.

If she is not there, see if you can find the file by using one of these programs. If you go Finder/display/show bar path, it will show you where it is located. You can then remove it.

-

My Fire Fox download video in support not detected on you tube. It is always shows only the first video that i was downloaded.pls help

I don't think there is much you can do about it outside the use of workaround to reload the page until this problem is corrected.

There is this bug on this problem:

I don't know if other extensions download suffer from this issue, as well, so you can try a little more try the website of the add-on and if possible use a different format like WebM, if they are available.

Also note that not all videos are downloaded and registered correctly. Some may have a size of 0 bytes and fail to download, so, best is to check in downloads of the toolbar Manager in the drop-down list to make sure that the file size is correct (i.e. neither 0 bytes, but a more likely size).

YouTube streaming makes changes to the code and the way its web pages work, so extensions can fail at any time.

-

I don't understand why I can't login my account using mozilla but with googlechrome fb, I am able to do... Mozilla can load the fb site but cannot access my fb account... I'm uncomfortable with the use of mozilla as my browser... pls help thanks

- "Clear the Cache": Tools > Options > advanced > network > storage (Cache) offline: 'clear now '.

- 'Delete Cookies' of sites that cause problems: Tools > Options > privacy > Cookies: "show the Cookies".

Start Firefox in Firefox to solve the issues in Safe Mode to check if one of the Add-ons is the cause of the problem (switch to the DEFAULT theme: Tools > Modules > themes).

- Makes no changes on the start safe mode window.

See:

-

pls help me to reset the password on the Board in my atom mini hp intel CNU9244BN4

pls help me to reset the password on the Board in my atom mini hp intel CNU9244BN4

Hangs.

Check your other post.

REO

-

HP pavilion 15-p153nm: I can't find the second slot of memory RAM... pls help

So I bought the new laptop (hp pavilion 15-p153nm), in the shop where I bought it says that this laptop have two memory slots, so I buy the new 4 gb ddr3 ram card and wanted to put in the free memory slot, but when I opened the laptop that I couldn't find free one slot... so my question is where is this second slot... I use other products (printers and laptop computers HP etc.) for 10y and if this is an hp error and they didn't put the second slot in this notebook, I'll be very disappointed.

And yes I find manual for this laptop, I opened this laptop from this manual and he drew two memory cards but its all is said about memory cards. I have pictures of the laptop and everything and I will put them here.Configuration software Specy

It says that I have a free slot? but I still don't see.

Now I'll put pictures of the laptop inside

under the keyboard

Other side of the main card

Under the motherboard

So pls help me to solve this mystery of the second memory slot.

And sry for my English isn't my main language.

TNX for helping me. Good bye

There is no second slot of memory in this model specification.

You need to replace the module installed with a capaity module above uppgrade the memory capacity.

On the three t pageit the manual describes two locations only on some models. It does not describe what models they are.

-

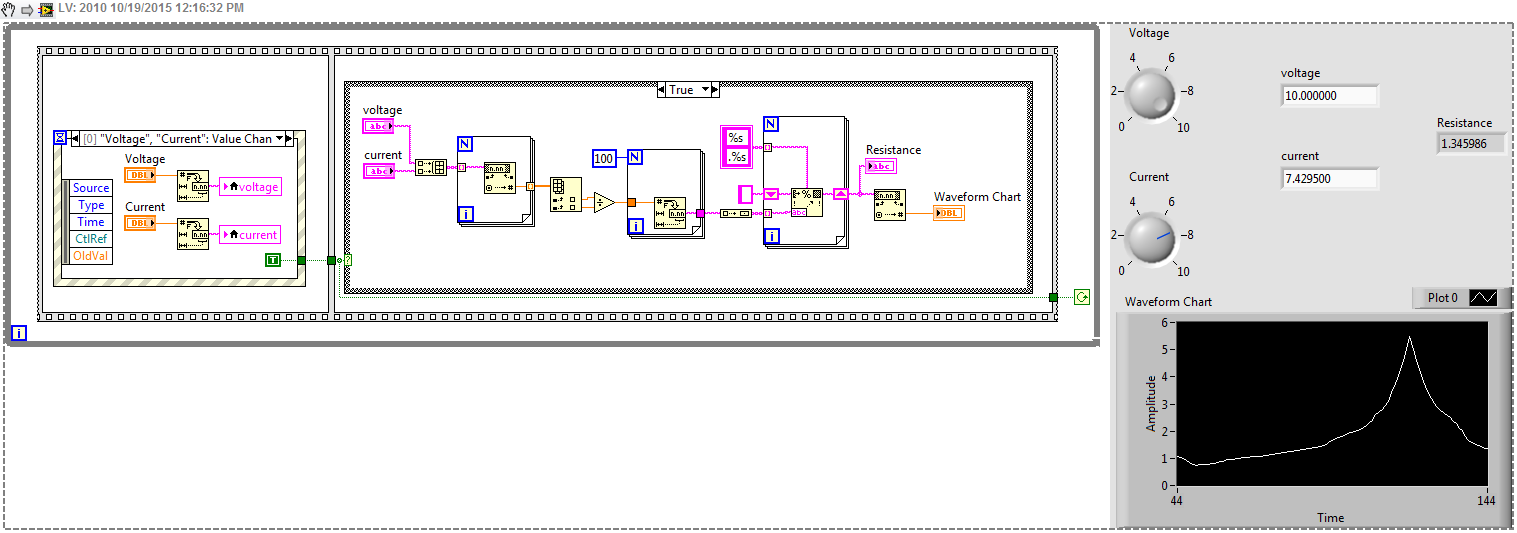

Hey someone create a labview program that uses the current and voltage to find the resistance. I also need a chart and buttons for aesthetic purposes. PLS HELP A GAL!

COME ON GUYS. HELP A GAL JAVA!

HERE YA GO, GAL.

-

activation of the xp SP3 after reinstalling on the same laptop computer. pls help

Original activation key (removed product key) helps to activate the xp SP3 after reinstalling after formatting C:\ due to the virus on the same laptop computer. pls help

To analyze and solve problems for Activation and Validation, we need to see a full copy of the report produced by the MGADiag tool

(download and save to the desktop - http://go.microsoft.com/fwlink/?linkid=52012 )

Once saved, run the tool.

Click on the button continue, which will produce the report.

To copy the report in your response, click the button copy in the tool (ignore the error at this stage), and then paste (using r-click and paste or Ctrl + V) in your response.

-* in your own thread *, pleasePlease also state the Version and edition of Windows cited on your COA sticker (if you a) in the case of your machine (or inside the battery compartment), but does NOT quote the key on the sticker!

http://www.Microsoft.com/howtotell/content.aspx?PG=COAPlease DELTE YOUR KEY - before it gets stolen and subsequently blocked.

-

my printer was asking a password am not able to find the password or reset an another pls help

I've used it since December when I bought the printer, but I just changemy internet company

It was when he said ask for password which i don't remember not pls help.

I can be paid to [personal information deleted]

Hi @funmi09

I want to help you set up your printer for your internet company recently changed. This document provides the steps necessary to find the WEP key or WPA or your wireless network password.

Once you retrieve your password, the following will help you to configure the printer; Connection of the printer after you have changed your wireless network.

If you still can't find your password, you will need to contact your ISP (internet service provider).

I hope this helps.

-

Failed to create the required registry key: vmware, Inc. error: 2 when installing the vm 7 wareinwin and the installation of any software of a few errors in registry pls help...

Hello mnaveen.kumar,

Search the registry to see if this key was created. Sometimes, the installation program does not have permission to this key.

HKEY_LOCAL_MACHINE\SOFTWARE\VMware, Inc.

You can try to manually create the key to see if this will help.

Please reply back and let us know if this can help.

Sincerely,

Marilyn

Microsoft Answers Support Engineer

Visit our Microsoft answers feedback Forum and let us know what you think -

I bought the original windows 7 os profeessional of outlets of my locality.but because of some problems technical I format the hd 2 - 3 times, so now my key is not registered. I'm a very poor people, it is not possible to buy the os again.pls.help me...

Have you tried to restart by phone?

How to activate Windows 7 manually (activate by phone)

1) click Start and in the search for box type: slui.exe 4

(2) press the ENTER"" key.

(3) select your "country" in the list.

(4) choose the option "activate phone".

(5) stay on the phone (do not select/press all options) and wait for a person to help you with the activation.

(6) explain your problem clearly to the support person.

http://support.Microsoft.com/kb/950929/en-usAfter you have reactivated, make an image of the system, in the future, when you want to reinstall Windows 7, restore you the image.

-

How to install lexmark 6170 to windows 7? I used the disk and still cannot print anything pls help

pls help

If your printer is the Lexmark x 6170 Lexmark tips (Windows 7 information link on the page http://support.lexmark.com/index?productCode=LEXMARK_X6170&page=product&focusedTab=DOWNLOADS&locale=EN&userlocale=EN_US#1 >)

is to use Windows Vista to Windows 7 drivers.

Printer drivers Windows Vista basic is available via the page above - he explains what you get in the driver package to the download link. Make sure that get you drivers 32 or 64-bit according to your version of the Windows.

* To see if you're running 32-bit or 64-Bit Windows click:

Start-> Control Panel-> system

Then look at where it says, "System Type".

Maybe you are looking for

-

Windows 10. Control user account each time to the home page. STINKS! Is there a solution?

Windows 10. Control user account each time to the home page. STINKS! Is there a solution?

-

Qosmio X 500 does not hear me using speech recognition / microphone

Hello! I often use the voice recognition feature Win7 Ultimate.However, since a few days, the computer does what I say more. Now, the built-in microphone is very insensitive: I have to get as close as in 10-15cm from the microphone in order to get ac

-

HP Compaq has a black screen at power up... The BIOS Corruption failure?

I have a Compaq Presario CQ61 product: VM9496Q2X model: CQ61-319WM series: [edited by moderator serial number], which has a black screen when I turn on. The wifi button stays red and the caps lock flashes twice. I think that it indicates a BIOS cur

-

I have the FBI Cyber Virus locked on my administrator account my pc & need to know how to remove it immediately without having to pay to do. I already know that he is infected with this virus, even if Microsoft Securities said that the pc is in gree

-

Cisco Secure ACS 4.2 on VMware ESX 4.0.

We must move from ESX 3.5 to ESX 4.0 a virtual machine running Cisco Secure ACS for Windows version 4.2. This solution is compatible and supported by Cisco? Thank you. Andrea