An SMU - 8133 RT or SMU - 8106 RT (only with Intel) is possible dual Bootable?

I'm looking for the development of a system flexible but high end standard PXI Express.

Flexibility includes (1) Dual Boot option and (2) options for the PXI Express modules and standards.

It will be much appreciated and will be a great help if an expert can answer my questions.

(1) an SMU - 8133 RT or an SMU - 8106 RT is possible dual Bootable? I am interested in Intel processors only.

(2) at - it another possible option with equivalent performance as the two above specification? Please also indicate an Express chassis with more or less 8 slots.

Thank you.

A1: Yes, the SMU-8133 is possible dual bootable. The SMU-8106 does not support RT (only the PXI-8106 (not express) package has been published as a RT controller).

A2. I'm not aware of any other option with equivalent at this time, as the SMU-8133 is our highest performance PXI Express controller, by a little bit. Learn the technical details a few comparisons of the 8133 for the 8108: http://sine.ni.com/ds/app/doc/p/id/ds-222/lang/en. You should look in the SMU-1082 NI for your chassis.

Tags: NI Hardware

Similar Questions

-

SMU 8262 streaming performance with HDD-8264 on an SMU 1062 q chassis

Hello

I have a SMU 1062 q chassis, Win XP, running with a 8262 connected to a HD8264 and two SMU 6537 installed, all three pension being on the express slots (3, 4 and 5). The application of benchmark to test the speed of streaming (Win32FileIO) I get something like 100 Mbit/s with data of pieces about 4 MB and about 140 MB/s with 64 piece Mr. Comment can improve these results to the limit off the coast of 600 MB / s? Y at - it a software/driver tip to apply?

And, in case, which is the best way to exploit the 8262 written c++ from the code (using the libraries OR)? Is there something similar to the Win32FileIO library? I tried to use the RAID system in program c ++ test, and performance seems very poor, whereas I would need, if not the 600 MB/s rate, at least something around 200 MB/s of diffusion continues.

Thanks in advance,

Piero.

Hi Neil,

I actually have a 8130 controller, and in fact, this was not the problem: I found the problem was the file interpreted by Windows file system caching. If you use standard fstream calls of C source code you can not get around, but using Windows native call (CreateFile (...), WriteFile (...) API) and definition of the indicator for no data cache or buffering inside the call, I managed to get the full bandwidth of 600 MB/s.

In any case thanks for the quick response!

Piero

I guess you have a controller that only supports PCI Express 1 x. The SMU-8130 is our highest bandwidth controller, with links to four x 4 goes on the chassis. In the case of the 1062, each of the locations, 3, 4 and 5 get a dedicated link to the controller. x 1 links on about 200 MB/s max and x 4 maximum at 800 MB/s.

So your first step is to use an embedded controller or MXI-Express x 4 instead of x 1 back to a host computer. The SMU-8130 is the best for data transfers broadband, the SMU-8106 should also suffice your needs.

If you want data streams on an SMU-6537 drive, it is already integrated into DAQmx. You simply specify a file name and the data are intended to drive. If you want to stream * of * disc, you will need to do it yourself. Here is an example of C/CVI for broadcast disk using a C API scanners and Windows file IO functions.

Neil

Senior Engineer

National Instruments

-

Can SMU x 1 Council works in locations x 4 SMU?

I have a controller SMU-8106 and an SMU-1062 q chassis. The SMU-1062 q basket bottom two edge hybrid location, two of them are directly x 4 PCI Express Link. CAN SMU x 1 Board works to, hybrid peripheral location, SMU x 4 slot?

If it is Yes, then, is there any setting I have to config on my x 1 on board or on the backplane 1062 until I plug my x 1 embark on this x 4 slot SMU?

Thank you very much...!!!

x 1 advice should work correctly in a chassis SMU-1062 q. It will form just as x 1. Maybe it's not true if there were x 4 redrivers in the system, but the controllers OR and chassis do not use them for background links basket.

For a not connectable card hot, let SUITE # disconnected, but bind PWREN # and PRSNTLY # bottom. Pull the MPWRGD to + 3, 3V.

Good luck with your design.

-Robert

-

RF Mux PXI-2546 driver stops working when DAQ SMU-6259 is used.

Hi, I am experiencing a very strange thing. I have a system with two 1065 equipped chassis with about 15 different instruments.

It was working fine and has done for several years. Today the SMU-6363 DAQ crashed, I tried to replace it with a spare DAQ SMU-6259. I started with switching just the daq spare in but then the computer crashed every time during the installation of the pilot SMU-6259. So I thought that I need a driver update and installed DAQmx 15.1 (previous version was 14.5). It has not made any change. Computer always crashes constantly. Finally I found that if I remove the PXI - 2546 Rfmux in the SMU-6259 DAQ system will install and work properly. But now Rfmux PXI-2546 will not work when acquiring data SMU-6259 are installed on the system. I can get the Rfmux to work if I take the DAQ and vice versa.

Why is it like this and what can I do to solve?

I do not understand why a PXI-2546 Rfmux and an SMU-6259 DAQ interfere with one another.

/ Erik

Hi Anton, thanks for your answer!

Yes, it's very strange. I narrowed down it to these two devices. I got the blue screen during the installation of the Windows driver. So I tried first update the driver OR DAQmx. Who did not have any change.

Then I tried to roll back the NOR-DAQmx driver to a previous version. Crashes stopped then, but I could not both devices to work simultaneously. In the windows Device Manager, he showed a problem for the NI DAQ PXI-2546 peripheral device. I don't know why a mux is considered DAQ hardware either. The description of the problem says "some free resources". If I could get the Rf mux to work if I unplugged the daq and vice versa.

For the last two days, I was reinstall the system from scratch. I'm not done yet because it takes so much time to do this, but it seems to be ok now. But what a pain. I started with just the driver Rf Mux (Switch).

To do this I had to download almost 3 GB! For a 2 x 4 x 1 Mux driver. Then, the driver for the installed switch some NOR-DAQmx which I had to then update and download even more.

I think that NEITHER makes it very complicated with the pilot stuff. Instead of having these huge drivers packages which supposed to cover everything, it would be better with the smaller specific device drivers that could be easily found on the web under each device.

In any case I hope it should work ok now. I wonder what will happen when I get home my repaired SMU-6363. Should I plug it in or simply do not bother because I could face the same problem again?

/ Erik

-

Where to find connectors for map plugin SMU

Can anyone help with information on the XP4/XJ4 connectors for SMU: numbers of appropriate provider type?

We want to make a personalized card to plug into a chassis SMU-1071 - but only a need the 3.3V power supply to the chassis. But after a long search, I was unable to find a number type for this connector. XJ4 is the smallest but of course all types of connector will do as they have all of the power pins.

Hello the heel.

I searched in our internal documents, and according to my findings we use ERNI as a manyfactor for our connectors.

Also, since you want to design for own PXI card, you might be able to find useful information in the PXI specification.

I hope you can use this information.

-

How to trigger SMU - 6363 AI with the PXI-4142

Hello

SMU-1082

SMU-6363

SMU-4142

LabVIEW 2012 SP1

Hello

I'm trying to trigger action (SMU-6363) analog input with my SMU (SMU-4142). The API OR-DCPower has a VI called VI of Signal to export, that I could use to export the trigger signal in a specific line when 'Complete the event Source' comes up on my EMS.

The problem now is that i ' v tried several lines to transfer the signal to the SMU-6363, but unfortunately I still have an error of DAQmx. Has anyone tried similar before sync? Which internal lines I have to use to get this working? I'm just not producing a moment of tension at the time that the EMS (Single, Point). After SMU has defined the level it must send the trigger for SMU-6363 who would then measure the external signals constantly.

Thanks in advance!

-henkkaHello

I solved the problem of routing measure relaxation of SMU with Signal.vi export online PFI0 of SMU-6363 (SMU 3 channel). Then I started every other SMU channels (0:2) with this signal to trigger by using the configuration digital edge measure Trigger.vi (the VI input terminal is PFI0).

I configured the data acquisition sample clock to use the PFI0 as a source of the clock. With this method I am able to measure sinus 2 kHz generated with four channels EMS individually with my DAQ without no phase shift (0.1 degrees) between own EMS measurement and data acquisition.

Hope this helps anyone with the same kind of problem.

Best regards

-Henry

-

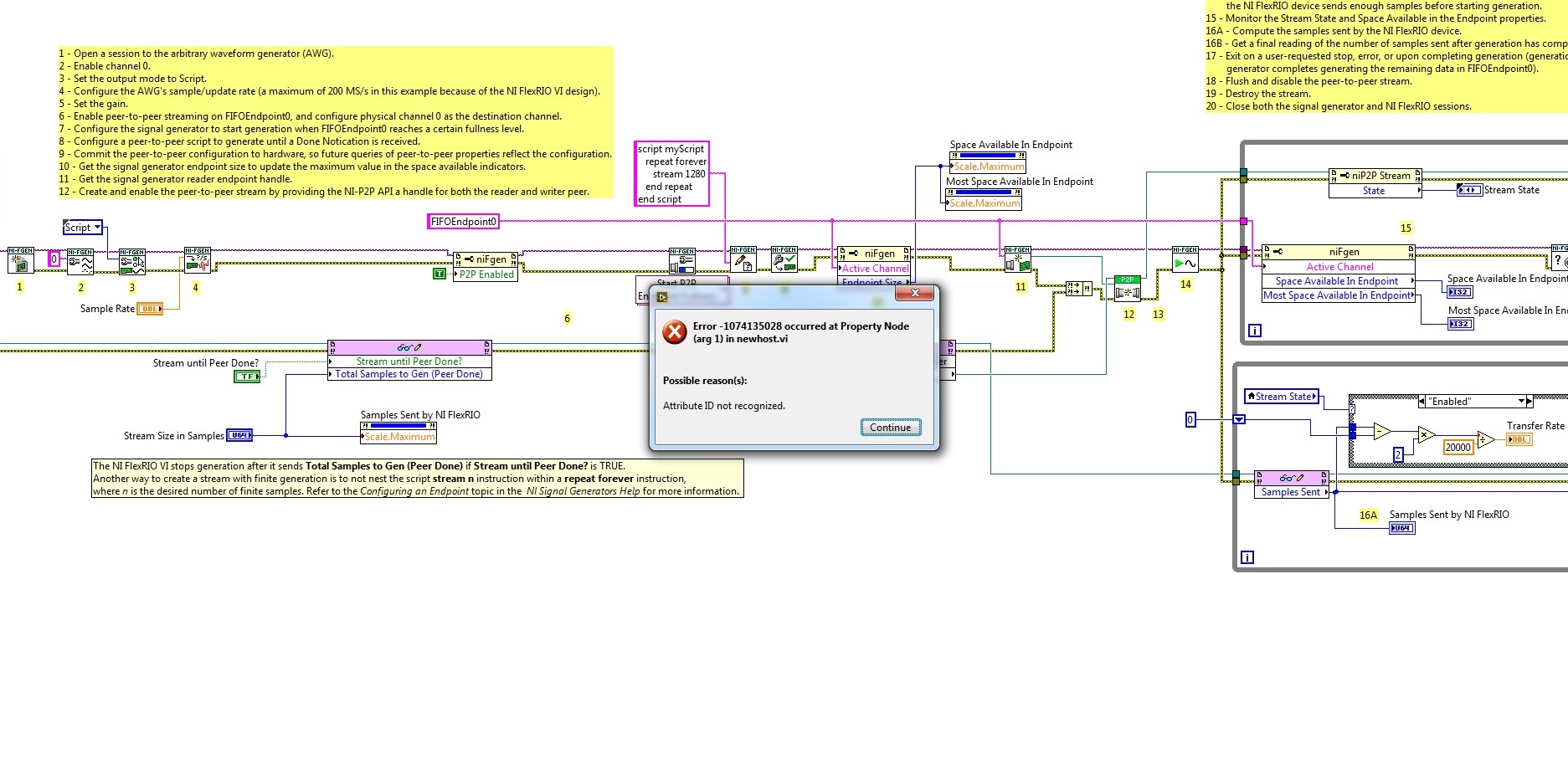

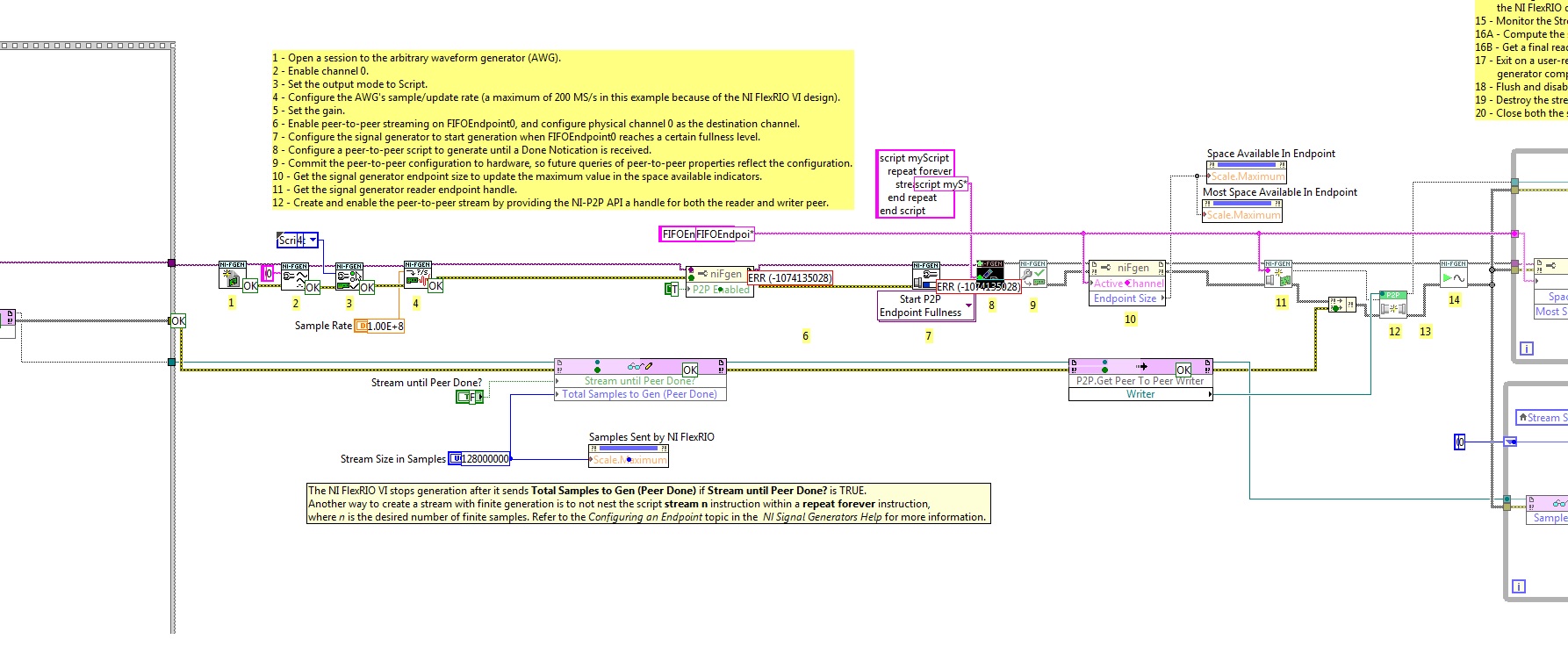

Peer to peer between SMU-5451 and SMU-7966R

Hello

I would like to connect two devices - SMU-5451(waveform generator) and SMU-7966R(NI FlexRIO) with the P2P streaming. I want to transmit data from FPGA to the generator and I took the example of NOR-FGEN. When I started host-vi, there is an error (see photo).

What I am doing wrong?

Try to set the Active Channel property before the active P2P. Property nodes run from top to bottom, so the Active Channel property must be set before calling the property Enabled of the P2P.

-

Wake On LAN for 8133 Pharlap running

Study the various options related to guard dogs and control of the external power supply and came across a white paper which talks about Wake On LAN (activate the controller via the Ethernet port). I see the instructions for Windows, but I use a race 8133 Pharlap. This feature is available with this platform/OS combination? If so, are there instructions for WOL with Pharlap? Thank you.

GSinMN

Unfortunately, the Wake On LAN feature is not supported by Phar Lap ETS. So that the WOL work, the ethernet for the operating system driver must be configured such that it can receive the wake-up signal. While it is possible in Windows, Linux and Mac, Phar Lap does not support this configuration. I apologize if our documentation was not clear and for confusion resulting in lack of clarity.

Kind regards

-

How to operate continuously the ' frequency with digitizer step-down converter external vi "?

Hello

I use SMU-5663 on SMU-1075 chassis. My goal is to use "step-down with digitizer external .vi" in order to run the SMU-6901 frequency continuous step-down converter. To do this, I added a while loop to the provided sample (see file attachment). The problem is that the while loop does not change; the program stops as soon as its launch.

Is there anyone who can help me with this you problem?Hello

The 'get frequency response' VI aims to help correct the answer of the step-down in the acquired data. The response of the step-down changes only with frequency and reference level. In your VI, you are in a loop when you call 'Get frequency response' but do not change the frequency or level baseline for the release of the VI will not change.

To use the external digitizer, you want to adjust the center frequency and level in DAMA reference, read the frequency response and frequency step-down converter win in DAMA, to acquire data starting from the external digitizer and correct using the frequency response of the step-down, and win. You can loop through the acquisition and treatment portions until you change the central frequency or reference level.

-

Salvation;

I have an SMU-1065 with the following modules: PXI-6529, PXI-6280, PXI-5114, & PXI-6713. I have 3 questions:

1. how the RTSI is launched?

2. how this trigger can be monitored?

3. How can I create a task is triggered RTSI?

I'm fairly new to LabVIEW but I work with other more experienced programmers.

Thanks for any help.

4BoysDad

Hello 4BoysDad,

Before talking about your questions, I will provide some information about the cards you because I think it will help me to answer the questions completely. First, the PXI-6529, the PXI-6280, PXI-6713 uses the DAQmx driver but the PXI-5114 is a digitizer and uses the driver NOR-Scope. Knowing this, I would focus on the passage of relaxing between 3 maps DAQmx first before thinking about the PXI-5114.

At the same time, you have an SMU-1065 chassis. With this chassis, there are 3 segments of trigger bus essentially dividing backplane. If one of these cards is in a different segment, you'll have to correct bus together segments to spend relaxation through the bottom of basket. To see how backplane it broken up, please look at the Datasheet for the SMU-1065. I would recommend that you put them on a PXI trigger bus segment.

With that in mind, here are my answers to the questions:

1.) how is initiated the RTSI trigger? How to create a task is triggered RTSI?

Before doing so, you will need to select a master device to the other slave devices. If the master device is a DAQmx device and you are passing to an another DAQmx slaves, here's a example of how to implement this. The relaxation will be initiated by the master device and in this example, the trigger is a beginning arm (for more information about this, please see the DAQmx help). Looking at this example, the RTSI trigger is managed in the synchronization of tasks - Trig Skew correction. With outbreak RTSI, this VI also allows you to synchronize the clocks of reference for each of the devices. Given that this example provides detailed notes as well as step-by-step instructions how it works, I will not repeat the information here.

If you want to synchronize the card extended with DAQmx device or multiple devices, you will need to export the signal to the other card. This example explains how to implement the scope as a master and the DAQmx device as slave. As others explain, it provides a general explanation how to achieve this as well as step by step instructions how to implement this.

2.) how this trigger will do?

Regarding surveillance of relaxation, I looked in the DAQmx and the pilot of scope but also consulted with my colleagues, and it is not a function, we found who will tell you that the shutter has been sent. We found one way to check this is to use the timeout for task/sessions to see if they started. If they have not the trigger has not yet been sent to the other device. You are looking for this feature for debugging purposes or will you for use in your program somehow?

If you have other questions about this, feel free to post.

-

Transmission of data to the host of RT to the FPGA via DMA FIFO

Hello

I try to write data from a host of RT on target FPGA using DMA FIFO and then process these data and read then return of the FPGA target to the host of the CR through an another DMA FIFO. I'm working on the NI SMU chassis 1062 q, with the built-in NI SMU-8130 RT controller and target FPGA NI SMU-7965R.

The problem I face is that I want to send three different tables, two of the same size and the third with different size, and I need one more small to be sent first to the FPGA. I tried to use encode dish with two executives in the FPGA VI. In the first image, I read and write the first table in a while loop which is finite (that is, a finite number of iterations). The second frame contains the process of reading and writing the second two tables (of the same size) in a while loop that can be finite or infinite (depending on a control). The problem is that it does not work. 2 arrays are displayed on the front panel of the RT VI host and works well, however, the table that should have been read in the first sequence does not appear on the front panel of the RT VI host. It is not sensible because if it is not passed from the host to the fpga and vice versa then the second image should not have been executed. Note that I'm wiring (-1) for the time-out period to block the while loop iterations until the passage of each item is completed. So the first while loop has only 3 iterations. Could someone help me undersdtand why this happens and how to fix this?

I enclose a picture of the host and the fpga vi.

Thank you.

If you vote for my idea here and it is implemented, you can even omit the loop FOR fully.

(I also propose the RE / IM divided inside the loop FOR and perform operations on complex table before the loop the transpose and reshape .) In this way, you only need one instance of these operations. You might even save some unnecessary allocations table in this way)

-

Unknown channel or feature name repeated

Hello

I want to connect NI SMU-5451(waveform generator) and NI-SMU-7966R(Flex RIO) with peer-to-peer technology. I took an example of NOR-FGEN, which works perfectly, but when I use it in my project there is a mistake takes place - the "unknown channel or feature name repeated" What should I do to fix this?

Hello

I saw this post in another place, and there was a proposal to reorganize the properties in your node as well as "Active Channel" is the first. As mentioned on this post, property nodes run top down and you may need to specify the channel before enabling the peer to peer. Did you get a chance to try this yet? You still see the same error?

-

Generation of series in multiple channels

Hi forum, I need to ask a few questions. Any help is appreciated.

(1) I need help with the generation dynamic series in several channels. Here, we can see how the dynamic data set generated by a single channel. But I can't find anywhere, how to generate several series signals in multiple channels.

(2) what is the limit for this generation series? I think it depends on the material, but I don't know, what is the limit. My hardware is SMU-6544.

(3) it is possible to generate different signals in different channels using scripts? and to start the production in these channels at the same time? the example given in the script generation labview is unfortunately only for the generation of a channel.

Thanks in advance,

Kind regards

Yan.

Hi Yan,

Produce on several channels with multiple data is difficult without a tool to view the data, or series of each channel bitstream concatenated into a software ADE and transposed before be downloaded into memory. To make Visual things here, I'll assume that you want to generate a pattern of 3 bits on sample of channels 0, 1 and 2 is 8 wide. Assume the following models of the series bit for each channel:

ch 0: 0101 1010

CH 1: 0000 1111

CH 2:0100 1101

So the question now is, how do you load this in the SMU-6544(or any other HSDIO hardware)? Of the two options, you can use Digital Waveform Editor (NEWS) to create visually and save to a file type HWS then load a DJ using the API HSDIO. It is the easiest in my opinion.

The second way is construction examples of data based on a basic example. I want to say is you take it all binary streams and built a 2D table so that it looks like:

01011010

00001111

01001101

An array of 3 x 8 and then transpose the table that turns into:

000

101

000

100

111

011

110

011

Here you can see we have 8 lines, each line is a sample, and in the form of U32 read in decimal, you get 0, 5, 0, 4, 7, 3, 6, 3. That's what you can load into our niHSDIO U32 function write a waveform. I hope you can see how this translation occurs and how it looks like in terms of load on the jury. Each sample usually contains data for all channels, where each bit in the U32 is one of the 32 channels available on your device. So if you want to write a '1' on Channel 5, you would load a value of 0000 0000 0000 0000 0000 0000 0010 0000 in the form of sample, where the 5th bit is 1 and all the other bits 0. In decimal, you would write '32' value.

With regard to the limitation of the size of series, if your flow rate is slow enough you can disseminate and make an almost endless stream, but assuming that you are running at the maximum rate, your series of waveform size is limited by the size of your on-board memory. Since each sample generation is 32-bit, which is 4 bytes for example, if a memory size of 32 MB will correspond to 8MS bitstream series max.

For any questions or comments are welcome. Thank you.

-

PXI: Request username and password

The deployment of the system definition file PXI system asks user name and password. Is there a way to bypass or confirm that programmatically? Can I disable this Max?

VeriStand and LabVIEW 2015 with SMU 1071

OK, with this method I can solve it: set the empty password. https://forums.NI.com/T5/LabVIEW/remove-password-from-RT-controller/m-p/3183622#M921345

-

acquisition of data high-speed and simultaneous sampling

I'm quite familiar with the coding for NOR-DAQ boards in Labview. What worries me with labview, is that each tick is about milliseconds. I intend to retrieve the data simultaneously from 32 channels at 2 MS/s/chan using SMU 6368 s. Wouldn't not possible to enter data, on average 20 to 50 samples to get a unique value, perform simple algebraic manipulations on it and send it to the PC / software to approximately tens of kHz? We already have labview code to perform similar tasks, but it is quite slow and limiting the rate of experience. I said that Simulink is slightly better than Labview in this regard, but suffers a poor user interface and that if something C/C++ offers the ability to perform at high speeds with the same cards OR data acquisition. Could someone advise me please on this issue?

You can use your PC! You can use a PCI/PCI-e card as the interface to your computer and it should work perfectly. Take a look at these pages (http://sine.ni.com/nips/cds/view/p/lang/en/nid/10389) for more information.

Maybe you are looking for

-

Compaq Presario sr1720 nx goes directly to the recovery & mouse & kyboard is unresponsive

The compaq Presario sr1720nx is directly to the recovery even if I hit the F6 key or the escape key start-up of the pc to the top. Once on the recovery screen, there are three choices that are not accessible because neither the keyboard nor the mous

-

Satellite P200 - Realtek driver install - I can do this backward?

I was about to install the Realtek 6.0.1.5605 audio driver but the installation screen says (I think, the English are poor) that he * remove the existing driver * and advise I need to re - install this if the upgrade has failed. I do not have the ori

-

In Outlook Express, can not see the file tab, such as page moves right

I can't move the Outlook Express mail page to the right. It just won't go further to the right. I get the arrow on the right side, but he doesn't hover over. So I don't see the file, only a part of the Mail tab tab (-Arnaud).

-

My cursor of volume under windows 7, keep going down and I tried to change the communication for the 'status quo', but still not working please help me

-

Guard Windows Explorer crashing and restarting

Hi all I use Windows 7 Home Premium 32 bit on a Toshiba laptop. Yesterday afternoon, this "Explorer stopped responds" / "reboot...". "begun loop that I couldn't solve. I was not doing something special when he started to occur, no new installs, no ne