default delay for timed loop

When the time is not specified (i.e. the value - 1), what is the default time that will fix the finish late? [i-1] indicator true?

Fix.

Tags: NI Software

Similar Questions

-

Operating system: Windows XP

Hardware: PCI 6259

Terminals used: PFI0 and PFI2

Counters used: Ctr0 and Ctr1

IM developing an application for the acquisition of data where timed loop synchronization source comes from my PFI2 (using the string A of an encoder). IM basically trying to acquire data based on the number of ticks from my encoder. For the synchronization source, I use counter 1 to capture the rising edge and have the loop time-acquisition of data. At the same time, Im using the counter 0 to count the number of rising edges so I know exactly in what tick data was acquired. PFI0 and PFI2 are connect to channel A of the encoder.

Questions:

Timed loop acquires data at each tick, because when I discover the data (text) file is missing count of my encoder value. Is it because there is a limitation on the Windows operating system? I used a noculars to measure the frequency at the maximum rotation of the channel encoder and 6,757 kHz. All solutions?

Also, is there anyway I can route the source channel internally an encoder to generate synchronization source instead of using another counter? I have attached my VI.

Hello

All the samples that you acquire will be read by LabVIEW in a sequential manner. Figure 4-21 on the M-series on page 80 (4-34) shows that you will acquire all the samples you request all channels that you enjoy in sequentially.

-

Why loops run after that assignment of processors for timed loops?

I have 256 call loops of two frames in my code. When I execute the code without affecting processors only 128 call loop runs at the same time, however when I attribute a different processor to each of them (0-255) then only 4 runs at the same time. Why is this? How can I make all run simultaneously?

Attached: two snapshots of the code. 1 shows a small portion of the call loops, and the other is the part of code that communicates with an FPGA VI which controls the status of the outputs (using a CRio-9066.) For call loops, the small Sun icon is a Subvi, which generates values for the time delay dt call loops.

doug333 wrote:

They run on the computer VI and I don't know how many processors available I!

Windows? If this is the case, don't bother with call loops. They add overhead and you're very unlikely to get something from him. Even basic affinity rarely helps. Normal just use While loop with a ms funtion in here waiting.

-

OR 9403: Digital Input/Output slows timed loop?

Hi all

I use a loop timed sample of 7 current channels (NI 9023), 3-channel (NI 9025) voltage at 1000 Hz in scan mode and it works fine. However, when I add for 8 output channels of the input/output module digital module NI 9403 for timed loop, CAPAS sampling cannot exceed 1000 Hz. According with time stamp data I wroten in file, it seems that I have in all ten milliseconds, I missed a miliseconds.

I would like to ask is there a reason for this? The digital I/o module affect the timed loop?

Thank you much in advance.

I'm not familiar with the FPGA code, so I can't comment there. However, I noticed that you call writing to text file twice in the timed loop. Can you only collect data and then write the files after the time loop? This would save a lot of time. For each entry, the program needs to access the hard disk, find the end of the file, add him and return to write on the hard drive. A lot of your time, especially since the files are getting bigger.

-

While why broken arrow will not appear for a timed loop

Hi all

I need a little clarification relative to normal while loop and timed looping in labview.

In labview, if I keep a while loop on a block diagram, broken arrow will appear in the upper left corner of the window indicating the error. It displays error because I have not wired conditional terminal of the while loop.

But same is not the case for a timed loop. Can someone tell me what is the reason behind this...

If I release the conditional terminal of the timed while loop, it runs in infinfite time like a normal while loop. Then y labview behaves differently for these two types of loops in the scenario above.

FYI... I'm using labview 2009.

Waiting for response.

Thank you

Herald

Ruben,

the reason is quite simple: call loops are mostly real-time and FPGA targets. Since most of the applications on these targets work continuously (at least this is more often the task), it is possible to create a loop that does not end. So the timed loop by default assumes that there is no need of a stop button.

The 'normal' while loop needs code for termination (conditional terminal) because normal applications on Windows/Linux/Mac are used to be fair...

hope this helps,

Norbert

-

Impossible to click on the buttons for the timed loop.

Hello!

I have a loop that is timed with a pace set by the user. And when the loop is running, I can't push any button of my GUI to stop it...

I have to wait until a mistake or I stop the race.

I can't put the diagram is too big and I think I don't have the right, but you have ideas?

Ask me for more details.

Thank you

bejard wrote: timed loop is just in a structure of the event and I put 10 ms or 100ms.

The program runs correctly (with this loop delay of 10ms/100 ms) like in the beginning, but I can't push any button or even change the tabs during the loop.

You shouldn't have long extensions inside the event. Which is supposed to stop your timed loop?

I think that you have the option "Lock the front until the end of the occurrence" lit. It will not press anything, until the end of everything for this case (including the timed loop).

According to my experience, using a loop timed in a Windows system is a complete waste and often adds more overhead and questions. Instead, I really think you need to use a State Machine. When the button is pressed, you tell your state machine to move to the State the code inside your timed loop tracks. You can use the State with the structure of the event to time your loop. If you can go behind your state of event to your processing loop structure. Just set the timeout on the structure of the event at any rate of loop you really want to.

-

Strange DAQmx Timing delay home error loop

I have a digital dashboard introduced in a timed loop counter. Everything works fine until I have stop the loop and stop the task of data acquisition. Once I restart the loop that it fails with 'resource is reserved. My code is attached.

Thank you

I think the problem is that when you set up a timed loop to use DAQmx task as its source of the time, the timed loop is automatically set to start the task at the start of the loop. Here, you never seem to stop the task of counter before restarting the timed loop. For the second time that you run the loop timed, it tries to restart the task of Counter and sees that a task is already running with this resource (from the first timed loop run).

If you use the function of the task to stop the task of counter after the timed loop, you should be able to restart things.

-

In the attached VI, I put the loop timed to end once the delay 1 reaches zero. However the timed loop continues to run and stop only if I have OR both 1 and 2 delay delay. (Tried with different schedules for late 2 which are less lag 1, equal to 1 delay and more delay 1 - no chance unless it is also linked to stop)

What is the reason for this? (The VI is in LV2012)

And it is protected by word that prevents us from looking into it.

Is this your VI or did you also?

Subvi properties seem to show that it is not reentrant. Otherwise it can only run one instance at a time. And if happens to store data to leave once it is called to another in the uninitialized shift, running an instance registers is probably interfering with the execution of the other instance.

-

Why the STOP button stops not timed loop.

Hello world

I had a rather complicated code launched against me. I had to change program action unique (and many other things) when ACQUIRING a button has been clicked making timed measurements. I was able to add the time... but I want the loop to stop once you click on the STOP button.

I have attached a very simplified version of my code.

So if you start and press the ACQUIRE the program generates random numbers (to simulate the measure) and records them with a device ID. The program stops once the total is for instance in the default settings after 20 sec.

But it does not stop when you press the STOP button. MY QUESTION: why not?

FOR INFO:

In my actual code, there are 10 events instead of only 1.

It doesn't have to stop immediately, inbetween iterations (because I already tried to include the timed stop Structure VI and it did not work either).

I also used the execution to highlight, but it did not help me.

Thank you for any help or suggestion!

Lisa

Lisa,

First of all, thank you for explaining clearly what your problem and to present a simplified program.

The problem with your program is very simple. The loop inside the structure of the event begins when the acquisition: Mouse Down event occurs, which seems to be what you wanted. The default condition for the case of the event is "front Lock (defer the treatment of the actions of the user) until the end of the occurrence of the event." This is controlled by a checkbox at the bottom of the evetn installation dialog box. What this means is that the stop button is not recognized until AFTER the event is complete. BUT the case of the event cannot complete until the while loop stops.

The Solution: Move the loop outside the case of the event. Generally speaking, event must not contain any code that could take more than a few milliseconds to run and certainly should not depend on the user's other actions to complete.

Look at the design of producer/consumer models (events) for advice. Also learn how to use queues to pass data between loops rather than local variables.

Lynn

-

Sequence structure flat inside the timed loop and execution order

I have some problems trying to implement a flat sequence structure when you use a loop timed on a target of cRio VI

I tried with or without the while loop around the structure of sequence flat, and I also tried to replace the 'Non-deterministic loop' with a timed loop

The problem is that the program seems to run only once, then get stuck somewhere

I am writing a program that performs the following operations as soon as possible:

1. read the Pos_MC of entry on the FPGA

2 send the value of Pos_MC to the VI target (on cRio CPU)

3. calculate a value of output based on Pos_MC with a PID block ("exit PID')

4. send 'PID output' to the FPGA

5 write "PID output" analog output "MOOG".In addition, I want the program to return the measured value "Pos_MC" to a host VI for the recording of data

So that the output of PID is calculated and sent to the FPGA as quickly as possible, I placed a flat sequence structure to ensure that it happens before you send the output to the nondeterministic loop for recording data

Also, I want the digital input 'Stop' to be able to stop the loop deterministic (the timed loop)

I read much more entries than that and the help of several PID and exit, but I rewrote the code for a single entry and exit to make it easier to illustrate

Screenshot of the code is shown in 'target code.png' and 'fpga code.png.

The VI themselves are attached in the next post (cannot attach files of more than 3)

Question 1:

Any advice on how to get this race? Thank you!Question 2:

Is also my correct understanding in that, using this structure, each 0.9ms (fpga loop time) comes the following:

1. the input ("Pos_MOOG") is read on the fpga

2. the production of PID is calculated on the cRio with some delay to computation (for example 0.1ms)

3. the output of PID is then written for analog output "MOOG" in all about 0, 1 - 0.2ms

4. the FPGA program then waits until 0.9ms spent and repeat the processAs opposed to the next pass whenever performing a loop is started on the FPGA:

1. the FPGA reads the input and written on the output (the output of the execution of the previous loop PID)

2. then the entry is sent the cRio, PID output is calculated and sent to the FPGA

3. the new release of PID is maintained until the next time through the loop

Thank you!

PHG wrote:

Thanks for the input guys, any advice as to how I could get the feature in scenario 1?

I still say that the best route is just putting all the logic of the control in the FPGA.

Other alternatives include 1) the use of DMA FIFO sedn data back or 2) use interruptions so that the FPGA code can not read the output level until the RT.

DMA FIFOs are usually very limited, and I would not use them in this situation since I belive said it this code to do for the many outputs.

-

Module speed FPGA, speed controller and timed loop speed

Hello.

I'm developing an application to acquire an analog signal at 800kS/s. Budget does not seem to be enough buy material excess spec. So I have to be very very accurate on all components. I had a look on the site and selected the following materials.

9221 8 module capable analog channel on 800kS/s sampling. I don't know if this sampling rate indicated in the specification of the module means that it can acquire up to 800kS/s or is the device samples ADC sampling rate to which the machine don't maybe not to the criteria of Nyquist and the module can perform sampling to 1.6MS / s is necessary which I think is not available?

9012-400 MHZ controller controller. If I put a while loop inside a VI under the RT target, it runs at 400 MHZ by default provided there is no code inside? Is so I could definitely use loop time express vi for sampling at the required level.

What of the timed loop? I just developed a project of RT and added vi under the RT target. The timed loop default clock frequency is 1 kHz and I can't select more than 1 MHz?

9112 chassis. Default clock 40 MHz. same rate issue which concerns the 9012 above controller.

Kind regards

Hi AustinCann

If you need to acquire 800 kech. / s, then the module module-9221 will be able to do this, if you are using only 1 channel, that is. The module using a global sample, therefore the maximum rate will be distributed on channels that you use.

If, however, you have to detect the frequency of > 400 then you would need a higher sampling rate to detect these, as you mentioned.

The controller processor runs at 400 MHz, even though the loops in your code will not run at this pace. On the target in real time, you can use a timed sources of clock - usually 1 kHz to 1 MHz - and set the period in terms of the chosen clock. If you need faster line rates, you can still code directly on the FPGA. The CompactRIO Developers Guide is a comprensive document and deals with most of the concepts of RT and FPGA.

The best course of action would be to contact your local office, because they have all the resources necessary for the specification of your system.

-

While loop inside a timed loop

Hello world!

I use:

-LV 7.1 + real-time;

-compactFieldpoint;When I put some time, I noticed a strange behavior, loop inside a timed loop. Let's fix loop timed with these settings:

-Clock 1 kHz

-1 ms period (Yes, I know it's short...)

-offset 0 ms

-Stage 0

-Take the period of absence (ON) and maintain initial Phase (ON);

-Timeout:-1.So, inside the loo, I put a traditional while loop, waiting (for example) an event will occur, and if this event doesn't happen, my cFP-2020 crashes! I mean, it becomes inaccessible for the debugger, and also, if I run a ping at his address, after a few cycles it becomes inaccessible as ping!

Obviously, that statement of code lock the fieldPoint, because if I remove the inside while loop all work.

I know that with 1ms duration, timed loop always the finishing of the delay, but I put the scrapping period missed and timeout-1.

It seems to me that sometimes timed loop add overload heavi programs, I all so that the loop according to the tasks, even if my application has be in real-time!Tips welcome! Good day!

Graziano

Thank you very much for your answer!

I'll test the entire application and then look for the best practice... but I still think I'll replace it timed with while loops loops...Good day!

Graziano

-

Loading the default limits for each execution

Hello

My situation is like this:

I spend my sequence using the sequential model. Usually, the sequence is executed, 'in the loop', which means that when once the sequential model is launched, we can test unit after unit until we want to put an end for some reason any. The sequence is load dynamically by the sequential model and download after executing the step to discharge option.

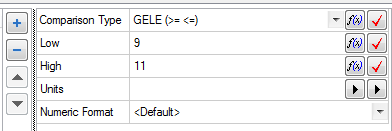

In the sequence, we use limits. Default TS limits similar to below.

All our limitations change during execution depending on what unit we test and on what stage is the unit.

Problem:

I thought that if the sequence is loaded dynamically, it is unloaded when executing the next time that the next unit will be tested the default values of the container limits will be charged (in response to being dynamically loaded and unloaded at the step which called the main sequence is executed). Unfortunately, it seems that when we realize continous test the test limits have not returned to the default value, as expected, but they are a superposition of the limits assigned by previous executions. Of course

Issues related to the:

1 are my expectations about the behavior of TS are correct?

2. how to impose default deadline to be 'reset', the default value for each run of the sequence, not only the first execution of sequential model?

MimiKLM wrote: I am worry the speed of loading, you talked about associated to your solution, but potential problems with memory. Let say, I called the main sequence of 1000 times without breaking execution. So instead of having one copy of the sequence called with wiped/reset all variables and properties I have 1000 copies in the memory. I would call it a waste to have 1000 copies only because I need to have the properties and variables deleted.

The copy exists only during the execution of the sequence. Once the execution of the sequence is complete, the copy will be destroyed/released. At least as long your code modules do not hold their own reference to it somewhere (which generally do not do).

If you call from the main sequence 1000 times in a loop, you must still do not have a runtime copy into memory at once. The difference is a new copy is created (and destroyed once that the sequence is made running) each time, rather than create a copy only once and reuse. There is a performance hit in this call of your sequence which is somewhat proportional to the size of your sequence, but unless your sequence is really huge, or test you execution is extremely fast, you probably won't see the difference.

Hope this helps to clear things up,

-Doug

-

Hello

I would like to create a FPGA loop that runs at a fixed rate. Whatever if I use a timed loop structure or a timer loop express VI into a regular while loop? Under what circumstances should I choose one over the other?

I understand that the timer loop approach can cause the code in the loop run twice before calendar is established (but this isn't a problem for me here). Are there other differences in the two approaches?

Thanks in advance.

JKSH wrote:

But my question was about the differences between the use of "multi-cycle" Timed loops and VI express loop timer.

In a targeted FPGA VI, all call loops are single cycle timed loops (SCTL). This means that all the code in a SCTL must run in a clock cycle, so there are a few types of nodes cannot be used in such a loop. In a used while loop with a timer, you can use a wider range of features, but the loop will generally run much more slowly.

These documents may be useful to learn how to use loops clocked on FPGA:

Using loops of Cycle time unique to optimize the FPGA VIs

Optimization of your screws of LabVIEW FPGA: running in parallel and Pipelining

-

Structure of the event in timed loop

Quick question on the structures of timed loops\event

What is a good or a bad idea to use structures of event call loops - as opposed to while loops. ? I guess I like the idea of call loops - because you can prioritize them - so if there are some important things you need priority of 100% in the background - but for the user interface, you can configure it to run slower\or run to a different priority level.

I just wanted to check it is not a reason why I shouldn't do that - since all the examples don't do that.

JP

I don't think it's a good idea. Your timed loop can stop waiting for an event. There is no advantage of placing the structure of the event in a timed loop. It is possible to assign priorities to other objects outside of the call loops. For example, you can the priorities given to subVIs. I'm reasonably sure that the structure of the event can work at other priorities if you do not the activities of the user interface. Maybe someone of NOR can confirm this.

But the goal of a timed loop is to have a deterministic periodic job. The structure of the event must be used for asynchronous events. The two disagree with them if they are in the same spot.

Maybe you are looking for

-

How to force you Firefox to download something when he resists?

When I download a file, for some files, I can check the 'Do automatically for files like this in the future' But NOT for everyone - sometimes this option is disabled. How I allowed it?

-

Envy 17 Notbeook PC: SimplePass always asking to confirm the password on Windows 10

Since the upgrade to Windows Pro 10, about a week ago, this happens whenever I try to drag to connect with SimplePass: I get a dialog box asking me to confirm my Windows password. I have to enter twice, and this works for me to open a session, it's b

-

Hi there everyone in that I currently have 8 GB (2 x 4) Ram my iMac late 2014 5 k and I want to upgrade. I read on the forums that if I buy 2x8gb ram, I'll be able to add them to my current 8 GB giving me a total of 24 GB of RAM. Is this correct? Sho

-

Hello I'm working on a labview test program. I tried to implement a loop that will basically take a measure ten times then stop. Then, I intend to read all these data in a data table a trend. My problem is that my curls do not work as expected, basic

-

Microsoft WIRELESS 3000 keyboard and mouse do not work.

I bought a set with wireless keyboard and mouse and even pretend to be plug-and-play, I couldn't make me work. What should I do Reference is Microsoft WIRELESS 3000 Thank you Original title: keyboard and wireless mouse