Parallel FPGA while loops

Hello

I m using a module NI 9870 in my Crio system and the program worked fine.

The problem I have is that I also need to use a Profinet PN module, and when I try to use both programs included in my FPGA, my 9870 module does not work like it s supposed to (it s points--instead of the characters).

Can someone help me with this? is it assumed that the different loops are independent and without any problem, are - it true?

or do I have to implement a program in a different way?

I would appreciate any idea or entry,

Thanks a lot for your help!

Thanks to all for the replies.

I ve already solved the problem, and it was the size of the FIFO for reading.

I use only a FIFO for reading, and to do this, I included a number after the data, according to which I m from port to aid. When the size of the data in the FIFO is not exactly the same that in the FPGA program, this function does not work correctly and returns false data.

After this change, the program worked correctly.

Thanks in any case again for your time!

Tags: NI Software

Similar Questions

-

LabVIEW FPGA while loop (first call? (VI) question

Hi gentlemen!

I am creating a LabVIEW FPGA VI appearing in a WHILE loop. He has a first call? VI in which, in the first occurrence of the loop, a variable must be initialized to some value. However, when I incorporate the VI in the FPGA, it would seem that the first call? VI has not been called. I also tried this implementation through registers at offset where the registry is initialized outside of the WHILE loop. However, the result is always the same. May I ask how the LabVIEW FPGA functions when it comes to everything IN a loop? Thank you very much!

For some reason that I don't me remember not I avoided the use of FPGA FirstCall and instead, I use a change sign boolean, son of genuine in the terminal, on the left and a fake in the while loop to the right Terminal. As a result, you get a true for the first iteration only, in exactly in the same way that the function of FirstCall. It could even use fewer resources on the FPGA?

-

Start stop while loop with tab control

I want to be able to start and stop a while loop by entering and leaving a tab. I use a structure of the event to do so, but it seems not elegant or the right way to do it. The only way I could get to the kind of work is by unchecking the lock front panel in case of structure. I have attached a sample vi of what I have so far.

The problem is that you can't even stop the program by pressing the stop button until you exit the tab, which is not a user friendly interface.

The event should just manage basic user events. Any given event does not take a lot of time to run. While you are in the diagnostics tab, your code is stuck in this while loop. Although the setting of the front panel of the lock allows you to do other things, the LabVIEW is just put on hold all these other events of the UI (like Stop button value change) and cannot handle them inside while the loop stops and allows outside while loop to go through again.

You should have a parallel while loop to manage waveform graph. You can use notifiers or queues or a motor of action FGV (see Ben Action Engine Nugget) to switch the starting or stopping of the update of the chart of waveform until the parallel of while loop.

-

Stop the multiple while loops in the acquisition of Vision

Hi, I want to close multiple while loops with a STOP. I use the software for the Acquisition of the Vision for the recording of multiple cameras and I would like to finish this record from all cameras simultaneously. I don't know how to do this since I am knew to LABView. I would add my VI here and maybe someone can help me. Thank you!

A local variable should be sufficient for your application. Read the following article:

-

Error with parallel while loops

Hello

I need to connect 6 different instruments gpib. I am using parallel loops, but the problem is when I try to open 2 or 3 Subvi simultaneously (the intstrument drivers), I just open one because of everything in a loop to run the Subvi. The program should be able to open all the Sub - VI independently.

Can give you some ideas?

Thank you

A. Castillo

Look at the detailed help for functions to notify. Then follow the links to the examples included with LV

Another problem that you have, whether you use your curls greedy or reporting or another technique, is to know how to stop your hand while loop. All the subVIs must be called before the loop stops. This is the fundamental paradigm of LV

You will probably need to rethink your primary architecture to something that will actually do what you want. Plan and design before your departure from the coding. Note requirements for the program and determine which parts are dependent on othrer parts, then select a program architecture that can meet the requirements.

Lynn

-

While loop with stop unwired FPGA button?

I've seen examples FPGA with a while loop where nothing is plugged to the stop button. On a target PC, it would throw an error. What it means?

I think you are talking about "Timed loops" that are "single-Cycle timed loops" on FPGA.

FPGA is intended to be run until it is powered, a 'Stop' software does not much sense.

Norbert

-

How to end parallel while loops

Hi, I'm using LV8.5. I have 2 while loops, running in parallel. Loop1 is faster (waiting time of 100 ms) and Loop2 is slower (several minutes waiting time). I use a local variable (STOP button) Boolean to commonality between the loops. The button is in the loop faster (Loop1) and the local variable is in Loop2. When I try to end the While loop, Loop1 stops immediately, while I have to wait for Loop2 finish. Is there a simple way to make two loops to stop immediately? I have been using a Control\Stop Application, but may not be the right solution.

Thank you.

Hi shanx2,

reduce waiting time in your second loop and count the iterations instead. The loop will do the same, but the stop will react much faster. Another possibility would be to use a queue instead. Connect to a timeout that corresponds to the current time-out period, you use and send a message to stop the loop. You can choose between the queue has been exceeded or not. Connect this result to the conditional loop. You can send the message from the queue after the first loop was arrested.

Mike

-

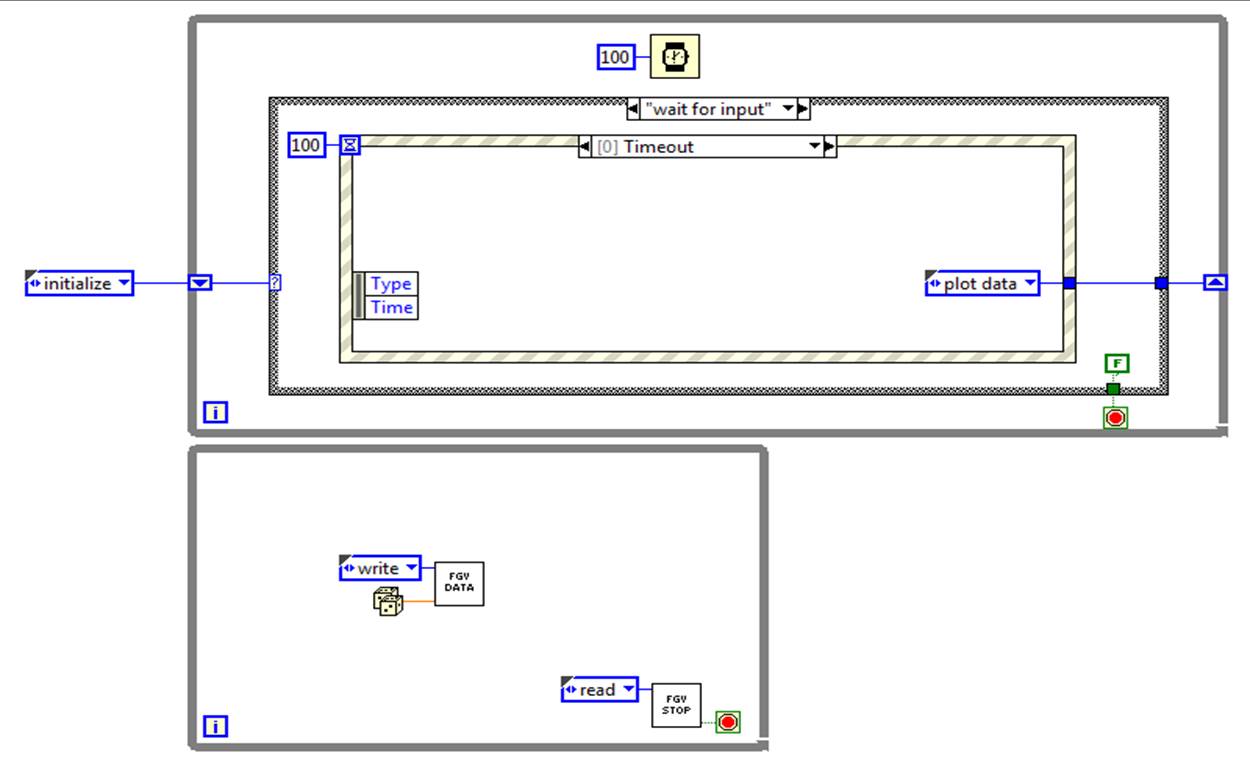

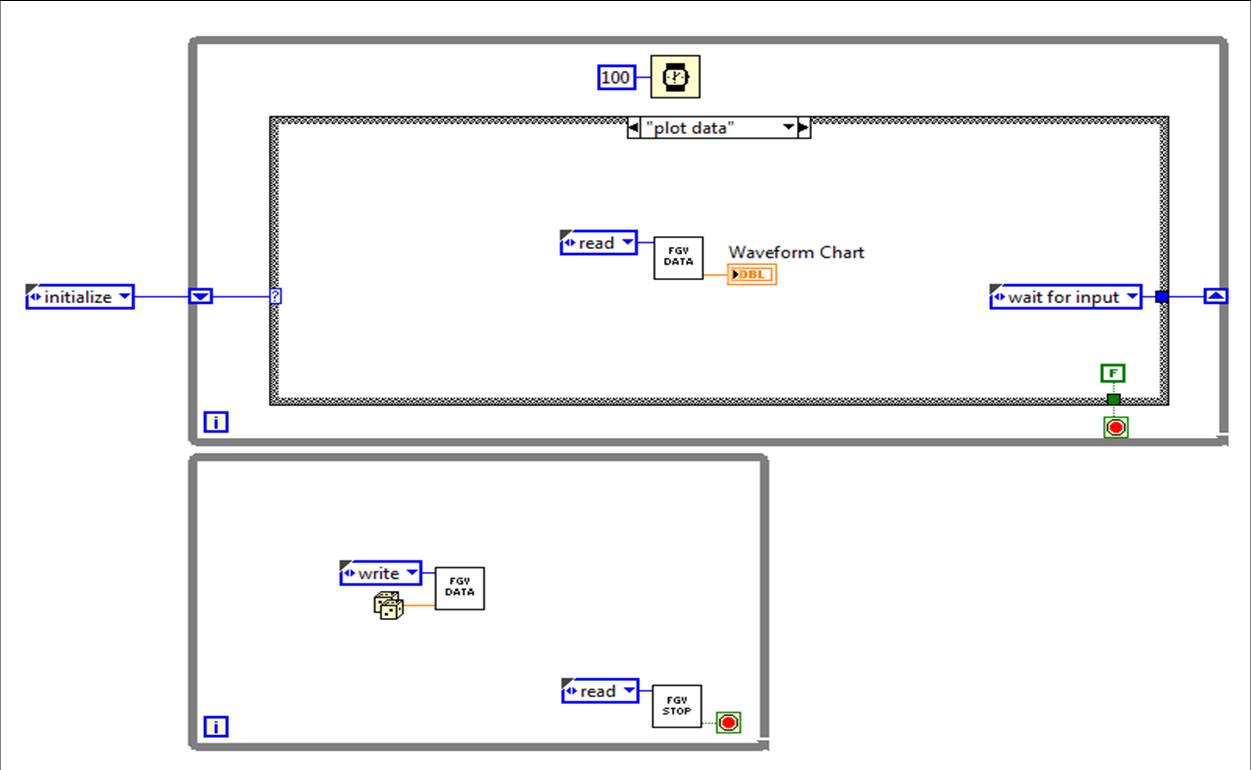

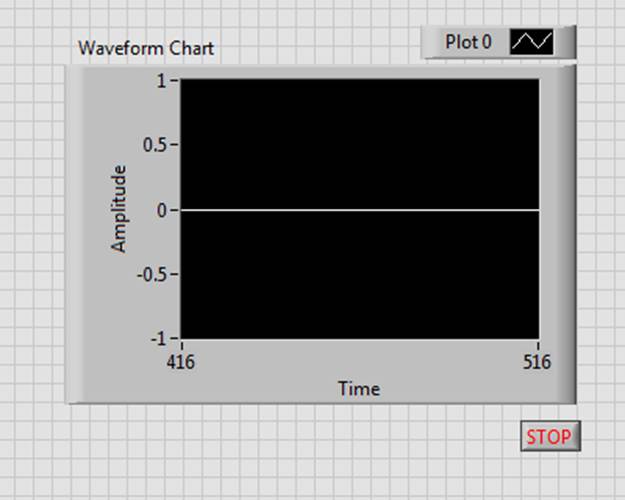

2 parallel while loops with functional overall to share data

Hello

I'm having a problem with the sharing of functional with globals data between two parallel while loops:

- One of the loop (bottom) generates a random number periodically and write the total functional sample.

- Another loop (above) has a structure of event and when it expires, he would read the functional global and intrigue, a chart data point.

The problem is sometimes the functional overall seems to be 'locked' and the output becomes zero constant. It also seems that whenever I first open the VI, it works fine. But for the second time running, he begins to have the problem.

You must initialize your VI stop FGV FRONT of your lower loop begins. Even if you use a global variable that is functional, you have a race condition. FGV is read in the lower loop until it had a chance to be initialized with a value of false in the upper loop. Functional global variables do not forget their data between executions of the VI. So it is always set on stop the last time that you ran the VI. This works your VI the first time it's because VI does not have in memory, so when it loads, it loads with the default value False in the shift register.

-

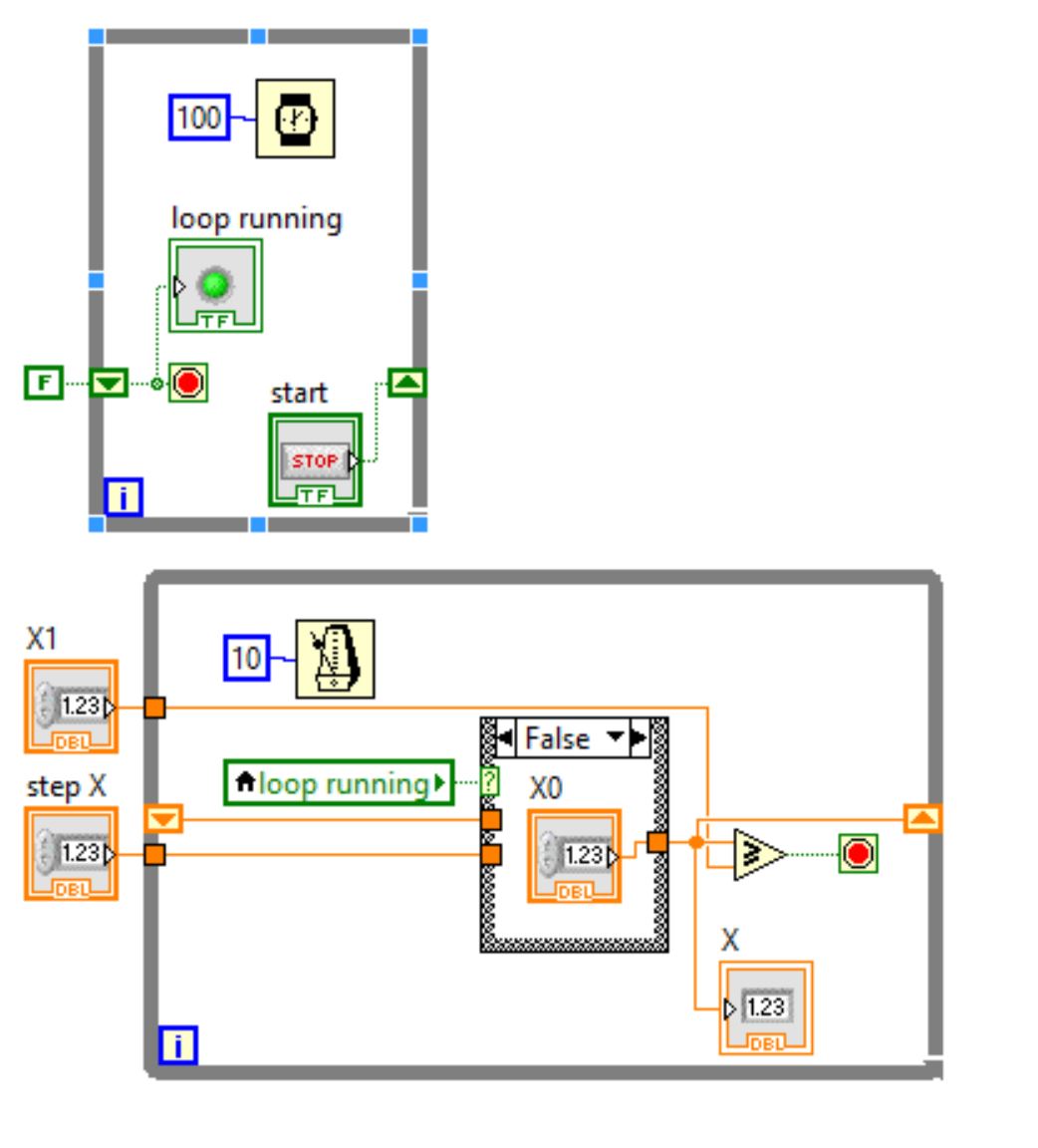

Two while loops in parallel - 2 does not run

Hello

In this simple configuration, there are 2 while loops:

- 1st - for installation

- 2nd - operation, where variable X increments

The problem is: after 1st run variable X is not reset to X 0, if VI stops immediately after it starts.

The reason - 2nd loop is not executed, X 0 if value is not propagated to X.

Thanks in advance

Pavel

You want to first one case installation and after perform the different number of steps, based on the parameters for installation.

A perfect place for one State (a single necessary loop usually) machine. You need an idle state when waiting for user input. After that the user starts the initialization state, which calculates the number of steps for other States required. At the end the system automatically moves back to the idle state, and waiting for the user to install and launch another race.

No need to sequence meal structure at all. With a state machine, you can just do much more (like abandonment of sequence to Midway, is not possible with the structures of the sequence)

-

A result of sending the data to a while loop through another loop of TCP communication

Hi all

I have 2 screws

1 matching model (using the method of Grab) which is put inside a while loop. This VI works correctly and returns a string in a specific format (position and the angle of the object).

2 TCP server who always listens to a specific port, if it receives a correct command string, it sends the string above VI - 1 (position and angle).

The two 2 screws works if they are in separate VI. But I want to combine them into 1 single VI and I get the problem: Pattern matching doesn't work anymore (the video has only first frame then stops).

I tried to put the two while loop in parallel or put the TCP while loop inside while loop Pattern Matching. Nothing has worked.

Pls see my attached VI and the TCP module.

What is the solution for requirement?

Thank you all!

What I would do, is be your two screws at the same time. Given that you do not send the last result, store the result in a global variable. Your comparison models written VI the global variable of the results of each iteration of the loop and the TCP bed module global variable results when it receives the right to order and then send it.

-

Control and Simulation in a loop / while loop with TCP/IP reading / writing of synchronization

Hello, I have a problem with reading TCP/IP and written in two loops. The problem is NOT to get the two loops to read and write to and from the other. This has been accomplished. My problem is when I run control and the loop simulation on my laptop and the while on a RTOS remote on the controller on-Board of LabVIEW in a remote PXI chassis, the while loop the remote system running on four 4 times faster than the loop control and simulation on my laptop. In other words, for each iteration of the loop control and simulation on my laptop, there are 4 four iterations of the while loop on the remote system. I need to know how to get a degree of kinship (1:1) with these iterations of the loop. When I run a longer simulation in real time, say 10 seconds, the control and Simulation loop begins to slow, i.e. the simulation time slows down until it is no longer in real time and the "Late Finish"? Parameter is set to true and the LED lights and continues to stay lit. At this point, the system destabilizes due to what I believe is being well sampling rate too discreet and I have to end the simulation. How can I get a ratio of one to one between the loops and also to avoid slowing the loops causing destabilization?

To give an overview of my application, I implement a control system in a network, seen in "image2.png". This is achieved using my laptop as a subsystem 1. Reference signals are generated from the laptop and the error signal is produced. Control measures taken and the control signals are sent via TCP/IP to the remote system. Position feedback is returned, and the process repeats. My system has Core I7 Procs w / 3 GB of RAM, up to 1 GB/s speed via ethernet and LabVIEW 2011 installed with all necessary modules and networking tools. The attached VI Custom_Wireless_Controller works on my laptop. The remote system I'm working on that has the 7830 NI R Series with FPGA card. OTN runs on the PXI chassis with an enbedded controller that has networking capabilities of up to 100 MB/s via ethernet. I use the FPGA for the acquisition of data and apply control signals to my plant. The plant is the PCE twist connected to the FPGA through the cable of the ECP - RIO of NOR. Subsystem 2 is this side of the CNE. The FPGA collects position, he sends to the controller via the network, receives signals from the network drive and writes signals to the plant power amplifier that operates the plant. This process is repeated and the VI and is titled Custom_Wireless_Plant.

I appreciate the help really and look forward for her and for any question!

Well, the first step is to understand what you have set up right now. Your control and Simulation loop on the side of the controller is configured as 'Runga Kutta 4' and you have a loop timed on the other side. In addition, you have the primitives of TCP/IP on the control and the Simulation diagram and means he will perform (a message) on the size of each minor step, which in your case is 4.

So, you have two options:

1. replace the Solver side controller Runga Kutta 1 (this must synchronize loops)

2. hold RK 4, but create a Subvi around two primitives of TCP/IP and configure from the VI to run than the major (continuous) step-size. If you do it right, you should see a 'C' on the upper right part of the VI you have created.

Please let me know if what I said is not clear...

-

Static analog output without a while loop?

Hi all

Would like to know if it is possible to set up a card outputs analog instrument (with DAQmx I presume) to have a static/continuous output, without needing to use a while loop. I what would want to return a single value rather than a table or a waveform. It would be similar to option for digital IO cards to have static strings instead of strings of waveform. In the examples I've seen, he always seems to be a time loop is necessary, even if the channel is configured for a single sample, but I think it would be cleaner and easier to control dynamically without the loop (particularly if I run several screws in parallel). My particular application is to configure inputs and outputs analog, then runs different tests with other maps of the instrument. Please notify. Thank you.

GSinMN

No, you don't need a loop. A writing DAQmx for 1Sample game, it's all you need. Please include am image of the pattern block one of these examples. My guess is that the example is simply a way to accept changes in production without having to re-run the whole VI.

-

Parallel FPGA in LabVIEW/Multisim co-simulation

Hi guys, it is possible to put 3 or 4 FPGA modules in a model of LabVIEW and then simulate jointly with Multisim runs 1 model plant? I want to simulate a converter of solar by using multiple parallel FPGA (this part on LabVIEW) cores conducted multiple interacting with the grid inverter bridges (this part is the Multisim factory model).

Hey hacmachdien,

This should be possible. If you have the Control Design and Simulation toolkit, you can use the control and the Simulation loop to simulate jointly with Multisim after you have installed the co-simulation plugin that comes with Multisim. See here for more information.

If you encapsulate your LabVIEW FPGA logic inside a Subvi, you should be able to use these subVIs in control and the loop simulation. There are a few caveats with this. First of all, the rate for the LabVIEW FPGA SubVIs must be configured depending on how they will run in the actual hardware. For example if the Subvi is inside a timed Cycle simple loop that is configured for a 40 MHz clock, you will need to configure the delay for the Subvi 25 ns. You can set up the period right-click on a Subvi in control and Simulation loop, then go to the Subvi node installation. In this menu, you can set the type of operation to be discreet and then configure the discreet calendar. Another restriction is certain things will not be supported as I/O. You can usually work around this by leaving your IO on the next level of your app and just by passing the values in the Subvi through controls and indicators. Let us know if you have any other questions!

-

How to set up the execution in a way independent while loops?

Hello

I hope someone here can help point me in the right direction for that. My system at this stage is still quite simple, I just data collection of 2 resistance probe and a pressure sensor, their output in the Panel before and sometimes to write. I have put architecture in place to call parallel loops running at the frequency I would ideally like to do. that is, I want the RTD to update every seconds and the pressure transducer for updating chaque.5s, I want to write to the file at a rate defined by the user and I want the Panel before updating a half second (correspondence with the pressure transducer).

Now, in the structure, I wrote, it should run all the while loop once before it can restart the sequence. Technically, the code works, but it takes ~1.5s to the RTD to collect and update and so the whole VI takes ~1.5s to complete.

I don't care if the RTD is slow to update, but as I use the sensor as a gauge of the cell pressure I need to know at a high frequency that the pressure is in the cell, and I don't want to wait 2 seconds for the information.

I know I'm starting to get into a much more advanced architecture for this and ive spent the last googler 6 hours trying to find a procedure for how it works but I can't figure out a way to have the whiles stop waiting for RTD loop finish. I guess that this is to divide the VI in several screws and construction of a library, but the resources I could find about it were not very useful for a beginner like me. If someone could point me in the right direction on where I should look then that would be great!

Thank you

Zach

Zach,

Because you created the tasks of data acquisition elsewhere, we do not understand how you have set up. Continuously, starting and stopping tasks may be slower than setting up of a permanent task and let it run.

You have not indicated that you use the DAQ hardware. It is often better to leave in the DAQ hardware clock set ignition rather than rely on software distribution. The pressure loop reads 1000 samples at a time and calculates their. If you're not sampling at 2000 s/s or faster, the loop ends late due to waiting for data. In two loops DAQ, you do not use the calendar information. Acquire the data in tables rather than waveforms.

The Dequeue functions in the loop at the bottom have no wait times for this loop will not iterate until all three queues have data. As the pressure loop runs faster than the loop of RTD, the queue of pressure slowly fills.

The upper and lower loops are vying for the data. The preview queue item does not delete data from the queue, but the functions of the Dequeue elements in the loop of the low fact. If data is deleted form the queue before the upper loop resembles it, it will never be saved. With your installation there is no way to ensure that you get all the data or that you do not read and record the same data more than once.

You don't have anything set up to stop one of the loops. You use the Cancel button to stop your VI? If Yes, STOP! Other aprticpant on the Forums said: "using the button abandon to stop a VI is similar to the use of a tree to stop a car.» It works, but can have unintended consequences. "Things like closing of files, freeing up the queues, by closing the task of acquiring data, and other things can occur when the program is interrupted. You do not shut down your computer by pulling the plug. Stop your program also neatly.

Ok. I have highlighted some of the things that can keep your program to run as desired. What can you do about them?

1. you probably don't need call loops. Normal so the loop should be good enough.

2 put a stop button on the front panel. Put the terminal in loops (bottom) and connect it to a function to send a Notification and the status of the Terminal loop (stop sign). Put wait Notification functions in each of the other loops. Put a period shorter than the time loop minimum on all of them if the lops can work.

3. see the comments above regarding the DAQ bed material.

4 use the Dequeue timeouts to adjust the pitch of the loop the loop where the data is used. Also make sure that all data is removed. You need to think about your time together and what are the bottlenecks. Except if you expect this system to grow to much larger dat sets, I probably acquire ALL data (pressure and RTD) at the same rate and reduce the displayed amount by the average like you do for pressure data now. If you want different final data rates, just average different amounts of data.

5. it might be useful to learn how to work the State machines. Display, averaged and recorded files could be managed in a loop by a simple state machine while allowing for more flexibility in the calendar.

6. Another good reason to consider a state machine is that initialization and shutdown processes can easily be handled in the corresponding States. At this point you do nothing with errors. A state machine would enable you to handle errors (for example, the cancellation of the selection of the user files) without stopping the program.

Lynn

-

VI is paused and while loop has highlighted

I'm in parallel while loops and for some reason when it should start to run loops, it pauses for the VI and highlights one loops. It was not last week when I ran it so I don't know what is the issue. I've included a screenshot of the beginning of the code, the loop that is highlighted is the down right. Also, what is the red dot on the wire in error right after the structure of sequence?

Thank you

lvuser333 wrote:

I'm in parallel while loops and for some reason when it should start to run loops, it pauses for the VI and highlights one loops. It was not last week when I ran it so I don't know what is the issue. I've included a screenshot of the beginning of the code, the loop that is highlighted is the down right. Also, what is the red dot on the wire in error right after the structure of sequence?

Thank you

Someone snuck into a breakpoint on you.

The red dot is the stopping point, and that's why your VI made a break.

The red dot is the stopping point, and that's why your VI made a break.

Maybe you are looking for

-

C55-B802 - Windows 10 drivers need satellite

And drivers windows 7 pls tanks

-

problems viewing videos

-

Video download dark and darker. What is the cause?

The problem occurs for DVDs and videos I find on the internet. I tried to increase the brightness by pressing 'fn and f8 '. Nothing helps so far. My operating system is Windows Vista. ASEFA

-

How does Apex support for work "bootstrap"?

HelloThis can be a very basic question, but I have here a bootstrap and application apex 4.2.4 using the sensitive issue 25. I noticed that whenever I Specifies a value for the duration column other than automatic, the following tag is generated: < d

-

jana13410867Prioriterede slutar plotsligt att fungera och ominstallation November. Fungerar inte ominstallation efter fortsätt. Felkod 5 visas. VAD gora?