PCIe-6537 County in ANSI C sample clock

I want to get the precise times of the edges on 32 digital lines using a card PCIe-6537. The card should have a sample of 50 MHz clock (minimum and 200 MHz/N N is 4). So if I can get a count of the sample clock when the any lines going from low to high, I know the time at a resolution of 20ns. Each line should have a transition from bass up per second. They should all be synchronized, it is possible that more than one line will have an advantage in the same sample clock signal.

I'm programming in Visual C++ with the DAQmx ANSI C API.

What I've tried so far, I think I need to put in place two DAQmx tasks: one to count the sample clock and one to detect transitions on the i/o 32 lines. The next problem after that is the task of transition to trigger a capture of a county on the first task.

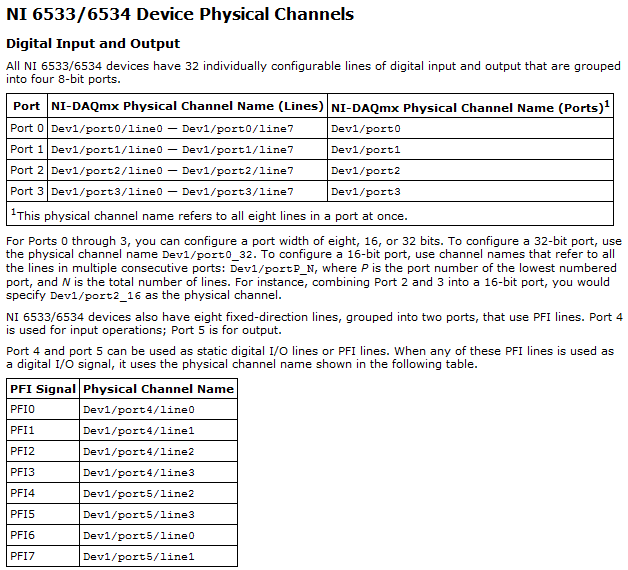

But I can't even set up a counter stain. I think I need to call DAQmxCreateCICountEdgesChan() to create a channel for the sample clock. The example code I found (Mult_Counters_Count_Dig_Start_Trig_TIO.c) sets the name of the channel to counter with a constant:

#define COUNTER_SOURCE1 "Dev2/ctr0.

My camera is 'Dev1 '. If I try to use ' Dev1/ctr0', I get:

Measurements: Physical channel specified does not exist on this machine.

Refer to the documentation for the channels available on this device.

Device: Dev1

Name of the physical channel: ctr0

Task name: Dev1CtrTask

Status code :-200170

I tried to call DAQmxGetDevCIPhysicalChans() to get the name of the channel, and I return an empty string. So I tried ' Dev1 / ' and got a similar error, unless of course

The physical channel name: empty string

Is it possible to count the sample with the 6537 clock? Or is there a better way to get the values of accurate time for transitions on the i/o lines?

Frank

As for performance, I can personally attest that I have listened 12 SMU-6537 at the maximum rate (50 MHz) with 32 lines on the disc. It seems there a configuration delivers in this case

OK, well, I don't have not sorted. She is still ongoing at only 40 MHz. But we decided to resolution 25ns is close enough for now (ran out of time for development  ). It's another problem of implementation of the task, so I asked a question separate from the maximum of PCIe 6537 ANSI C sample clock

). It's another problem of implementation of the task, so I asked a question separate from the maximum of PCIe 6537 ANSI C sample clock

Since then, with the help of the forum I got my running program, I would like to summarize the thread and the solution to my problem, in case anyone else is the rising later.

- The problem is exactly the timestamp rising edges on a set of 32 digital inputs. I expect only a couple of edges per second per channel, but I need to know when they occur (in fact the interval between the edges on different lines) as accurately as possible.

- I thought that the card could detect changes on inputs and pass a count of the sample clock pulses during an edge has occurred.

- The 6537 has no channel counter, so it will not be a feasible way

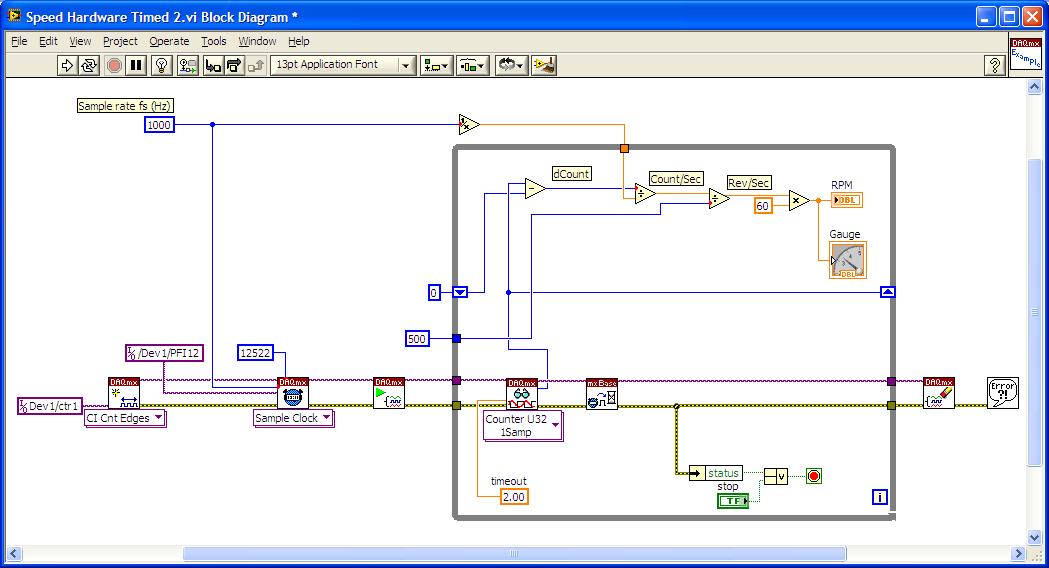

- Definition of the card to read all 32 lines on the forehead amount of sample clock allows me to write a reminder that allows you to see the status of each line on each sample clock. Because I know that the period of the sample clock, I know that the time of each sample. The reminder I have used a few loops on the pad looking for changes.

- Surprisingly, this set only 30% a single processor and 40% on the other CPU on a 2-core 2.2 GHz PC. Well, that surprised me. I don't think that the PC could handle shoveling bits that fast autour. SCP got fast enough since the last time I built a. Sample clock was 40 MHz.

- The callback uses DAQmxReadRaw (taskHandle, DAQmx_Val_Auto, 0, SampleArray, SampleArraySize, unread, & numBytesPerSamp, NULL). The documentation for it says unread will be set to the number of bytes read; It should indicate the number of samples. And I should have used DAQmxReadDigitalU32() instead in any case.

Thanks to all those who helped with my lights

Frank

Tags: NI Hardware

Similar Questions

-

Maximum sample clock of PCIe 6537 ANSI C

I'm programming a card PCIe-6537 with ANSI C. The application uses sampling continuously, with a reminder to analyze the samples.

The maximum sampling frequency should be 50 000 000 samples/s. The internal sample clock is assumed to be 200 MHz/N where N > = 4.

I can run to 40.000.000 samples/s (N = 5), but if I put the sample clock to 50,000,000 samples/s (N = 4), the callback is never called.

I created the task with the following calls.

DAQmxCreateTask (TaskName.c_str (), & m_TaskHandle);

I calculate $thisline = ' Dev1/portX/BEHLULI for X = Y = 0.7 and 0.3 and I call for each

DAQmxCreateDIChan (m_TaskHandle, ThisLine.c_str (), "", DAQmx_Val_ChanPerLine);

Then I put in place of the sample clock. It works:

DAQmxCfgSampClkTiming (m_TaskHandle, NULL,

40000000, DAQmx_Val_Rising, DAQmx_Val_ContSamps, 16000000

);It's not:

DAQmxCfgSampClkTiming (m_TaskHandle, NULL,

50000000, DAQmx_Val_Rising, DAQmx_Val_ContSamps, 16000000

);I save the callback so:

() DAQmxRegisterEveryNSamplesEvent

m_TaskHandle,

DAQmx_Val_Acquired_Into_Buffer,

4000000,

0,

NI6537_EveryNSamplesCallback,

This

) ;The callback increments an integer that came out when I end the program by pressing ESC.

Y at - there a trick to getting the sample clock to work at the rate increase? Or it is limited by the PC somehow, so that the callback just won't happen to 50Ms/s?

Frank

Frank,

You can check and make sure that the BIOS of your PC has been updated to the latest revision. This can have an effect on the maximum transfer speed on PCI Express.

There are some cases (depending on the maximum packet size allowed by the chipset of your computer) where a PCIe-6537 cannot acquire 32 channels of data at 50 MHz. It's strictly a limitation of the PC. If your BIOS is up to date and it still does not work, you can try your code with the PCIe-6537 on a newer computer?

Keith Shapiro

National Instruments R & D

-

Measurement error of the County of edge by using the external sample clock

Hello

I'm trying to measure the number of edges (rising) on a square wave at 5 kHz with a generator function on a device of the NI PCIe-6363. I configured a channel of County of front edge of counter at the entrance of the PFI8 device. I use an external sample clock that is provided by the output of the meter of a NI USB-6211 housing channel. If I acquire for 10secs then ideally I would expect to see a total of 50000 edges measured on the meter inlet channel. However, my reading is anywhere between 49900 and 50000.

When I use the internal clock of time base to measure the edges, the measure is accurate and almost always exactly 50000. I understand that when you use the external sample clock, the precision of the measurements is subject to noise level of the clock signal. However, I checked the clock signal is stable and not very noisy. Any reason why there is an error of measurement and how tolerance should I expect when using an external sample clock compared to when you use the internal time base clock?

Also, what is best clock Frequency (with respect to the frequency of the input signal) when using an external clock?

Thank you

Noblet

Hi all

Thanks for all your sugggestions. I was using an input signal with a function generator which had a range of 8V. It turns out that the reduction of the amplitude to 5V solves the problem. I was able to get accurate numbers with the 6211 external clock.

Thank you

Noblet

-

Hello

I have a small question on an example of clock by RTSI source.

In my configuration, two PCI cards (PCI-6602 (dev2) and PCI-6110 (dev1)) are connected by a RTSI cable.

I would like to build a clock on 6110 source sample and use it on 6602 counting external impulses of entry.

In the MAX test Panel, I checked that a meter was reading of external signals.

However, the vi attached do not work, and the whole County, and then give an error of 200284.

Could you tell me what is the problem?

I guess that something is not right on the clock signal routing. I have to use DAXmx connect terminals vi instead of external signal?

How can I check that both devices are connected through a RTSI cable?

I recorded the cable and connected devices on MAX with no problems. Is this enough?

Thank you for your comments and kind suggesion.

Several things briefly:

- Must match the orientation of the RTSI cable. Connectors are generally indexed to ensure this, but if you use a cable in water House, just keep it flat between the boards.

- The code you posted attempts to use the time base internal 20 MHz as a sample clock. That will not work for several reasons, and the fact that you try suggests you may have a poor understanding of the functioning of the meter. You do * not * need to "sample" at a pace high in order to catch the digital transitions. The meter circuit manages everything in the material. What you "sample" in a task of counter is a County registry value. Digital TTL edges which are worth little matter how many times you "sample" it increases.

- I suspect you want to * account * cycles of the clock of the signal of your 6110, be it a train of pulses counter or a sample clock based on the tasks.

- I am writing an example that does without buffer sampling clocked by the software, to approximately 10 Hz. Dev2 uses to generate a pulse of 1000 Hz and uses Dev1 train to interrogate the County registry value in a loop. It is simple from the code you posted to help unravel the special problems of routing RTSI config problems. Start using something simple like this to see if DAQmx succeeds routing signals through RTSI.

-Kevin P

-

An external sample clock between sharing arrangements

I need to acquire samples of 2 separated Renault M series (PCI-6254). My master device receives a sample of 8 on PFI0 KHz clock. Is it possible at the root of this clock of the master to the slave via a RTSI cable device?

I looked through the forum and the sample programs, but have only seen examples in which the master clock on board the aircraft happened to the slave.

It is possibe to synchornize device slave the master clock to external sampling of the device?

Thank you

ANT1

ANT1,

Fortunately, most of the time something that can be done in DAQmx in LabVIEW can be done in ANSI C using the appropriate function calls. I have listed the following steps of the program example LabVIEW and retouched to remove anything that it is not suitable for the DAQmx configuration. I'm sure it should work for you.

Steps to follow:

1 create a channel of analog input voltage for the master and the slave.

2 set the synchronization parameters. For the master, select the source of the external sample clock. Set the source AI/SampleClock of the master for the slave device. (Note: sample of the master clock is automatically routed through the cable RTSI.)

3. for the slave, set the Source of the trigger to the AI/StartTrigger of the master device. This will ensure that both devices start sampling at the same time. (Note: the trigger is automatically redirected via the RTSI cable.)

4. call the start task to start the acquisition. (Note: start slave task before the master task.)

6. read all waveform data.

7. call the clear task to stop the acquisition and clear the task.So, essentially, the value of the task of the slave to the top in the same way as you would for the synchronization of clocks on board, but configure the task to master as you would for an external clock. This will automatically share the external clock and trigger on the line of the RTSI.

-

Synchronization of analog and digital output with the external sample clock

Hello

First of all sorry for my English, I will try to explain what I want to do.

I want my PCIe-6321 to send two custom signals (modification sawtooths) on a mirror controller. I would also like to generate output with my card at the beginning of each tooth of saw. Everything must be synchronized with an external k-clock signal of 100 kHz. The idea is that whenever the PCI receives a trigger to external clock, it sends two analog output voltages and when he received 1024 clock ticks it will also send a pic of triggering TTL. What I do is first prepare the map and after that in a loop sending and modifing the output values of the two signals and at the same time send a digital signal Boolean in each arch, so when's done it 1024 iterations of the loop I send an event to the digital port. Attached you can see.

The problem is that I don't know how to synchronize both. Can I use the sample clock just to the analog output? I can use sample for the two outputs clock, or do I need to use the output of the meter? If don't know how to use it here.

If I do nothing else bad/wrong, I would be grateful for feedback.

Thanks in advance,

PabloI don't know how but I find the solution. I'm generating more than a positive value (as I was triggered maybe very fast the oscilloscope has been absent there). If I put the sample clock of digital output to use the sampling/ao/Dev1 clock that it doesn't, but if I put to use the same source as the OD (terminal where my external clock is connected), but the trigger to start the DO to be Dev1/ao/StartTrigger this works. I don't really know why, but it does.

Thank you for your patience and your help. I put here the final code.

-

AI sample clock using to Trigger counter samples

My basic question is: the ai\SampleClock signal is active only during the execution of a task of analog input?

The details are:

I have a multifunction data acquisition card series X PCIe-6321. It is controlling an SCXI chassis and has a module SCXI-1180 and SCXI-1302, so I can control the analog inputs of the chassis but also access to the meter 4 on the map. My application requires that I use all 4 meters to measure a frequency input signal and synchronize the samples for the analog input signals. I created 5 tasks, 1 for AI and 1 for each counter.

I'm using LabVIEW 8.6.1 with the latest NOR-DAQ drivers on and the operating system 64-bit Vista

1 are there drivers or hardware restrictions that cause this solution does not work?

2. can I use the ai\SampleClock as sample clock of entry for each task frequency? If I do this the beginning of sampling will be synchronized? I.e. If I each task frequency first starts, they will wait until that task to HAVE it is started before you start sampling?

3. If this does not work, do I need to send the sample clock of the task of the AI to a line PFI (PFI1) and then use it as the special frequency sample clock input?

I used to do option 3 when the synchronization of two cards in PXI chassis and use only the beginning of the task of the software instead of synchronization on a digital departure, given that the sample clock will control samples anyway. I need to know if the same behavior works with the above scenario.

Thank you

Bob

Prolucid Technolgies Inc.

Hi Bob,

I can confirm that the AI/SampleClock is available only during the execution of the task to HAVE it. As far as other issues go:

1. you must provide more information on what you seek to do exactly, but there is no problem with the clock of the task of analog input sampling to be used with routing counters. I had read through the section of the X series operating manual which deals with the measures of frequency clocked at sample (see page 7-16) for more information about what really happens during this configuration to make sure that it suits your needs.

The frequency of the signal to be measured must be at least two times faster than the sample of your task clock to HAVE.

2. you can indeed pass the signal on all four tasks at the same time (you can check the page peripheral routes in MAX to ensure the routing restrictions). Sampling will be synchronized four counters are started before the task to HAVE it, but counters will be armed at different times unless you configure a trigger to begin arms (see page 7-45 series X operating instructions). I would consider using the AI/StartTrigger if you want to do.

The effect of not to arm the counters at the same time would be a different number of periods on average on each counter for the first sample (assuming an average is enabled). Maybe it's not a major concern, but I just wanted to point out.

3. the itineraries are available inside the Board of directors so external routing is not necessary, you can simply specify to use the sample clock of the AI for each meter clock and roads will be done for you. If you want to export the signal on a PFI line and new route on another line PFI, this option is also available for you, but shouldn't be necessary.

I hope this helps you get started. I'll make sure to take a look at Chapter 7 of the X series user manual, if you have a chance as he described how all configurations of meter of working more in detail. If you have related questions do not hesitate to post in return.

Best regards

John

-

How the PFI to go top-to-bottom with sample clock?

Hello world!

I am very new to LabView and I try to do something very simple in the NI PCI-6534 and still not get anywhere (or do not know if it is the limitation of the hardware)

My request is to acquire digital data of 2 channels (16-bit each) of our Board custom designed analog-to-digital.

So far, I am in a position to acquire a finite amount of sampling digital (say 100000) and using a trigger to start (PFI6) to start the acquisition of our custom card board. Just to let you know that I'm feeding the PCI-6534 an external clock of 20 MHz by PFI2.

However, I want to send a signal to trigger recognition (high/low-rising edge) to our personal advice, saying: he did the acquisition of 100000-sample.

My problem is that whenever I try to use the lines of PFI signal with an internal sample clock, I get an error saying that I can't use the PFI lines with any sample clock. But my goal is to use a rising edge (low-high) to trigger back.

So far, I can pull the PFI4 high and used a timer to make it low. But the resolution of the timer is milliseconds (software) range. I would like to have at least a few microseconds.

I also tried using implicit since manual said that it does not require any clock but still get no result. Also, I couldn't find an example of implied clock and don't know if PCI-6534 supports.

Note that I'm able to use the clock synchronization of sampling with other DIO (Port 0 to Port 3) lines and get the result I want. However, I would need to use all our custom Board 32 - DIO for analog-to-digital data lines. So, using the line of PFI laccuse is the only choice.

If you have ideas/pointers, please throw it at me, I'll try them. Thanks a lot for your help!

See you soon,.

Yaseen KhanHi ykhan,

After validation, I noticed that it will not really work for what you are trying to do. The PFI lines on your 6534 are I/O static only as shown in the DAQmx help.

You will be able to control these lines, but only with software timing. You should be able to call and argue by their physical channel name. I hope this helps!

Kind regards

-

External sample clock change takes a lot of time on the SMU-5186

Hello

I use the external Lv - niScope EX Clocking.vi example to define SMU-5186 using an external sample clock. However, it takes a long time, 5-6 minutes, before I can get the first block of data acquisition.

Then I run the example 'niScope EX Acquisition.vi Configured' to switch to dashboard clock. There are also 5 to 6 minutes on the first acquisition.

I think maybe the SMU-5186 made some calibration when I change the source of the clock.

Anyway is to ignore the calibration? Or make it faster?

Thank you very much

Yiming

Yiming,

Delays in acquisition are caused by calibration routines that must be performed on the engine to sample (ADC) every time that changes sampling rate. This ensures our justified precision specifications.

I don't know if you've noticed also calibration of Power-Up, which will take 5-10 minutes to complete when the unit is turned on. This is mentioned in our specifications at page 18:

http://www.NI.com/PDF/manuals/373257b.PDF#page=18

I hope this helps.

Nathan

-

Problem with DAQmx Schedule VI (sample clock)

Hello to you all,.

I'm new to this forum, please bare with me. I have some experience with LV, but I am relatively new to data acquisition projects. I use LV2009.

I want to make sure that I use the hardware timing (instead of software distribution) in my project so I followed some of the threads here as sugested to use DAQmx Schedule VI. The problem is that no matter how I set the system I get the same error-200300 invalid calendar

type.The project is simple. I encode with 1000 pulses per

Rev and it is mounted on a shaft of a turbine water goes thru. I'm watching the frequency

and so the rotation of the shaft which tells me that the amount of water flows through the turbine. In the end, there will be 2 channels

by every encoder and ~ 3 encoders (turbines) total and calibrated the main meter that will give me constant impulses and all encoders will be compared to this master frequency.I'll use PCI6602 DAQ, but

now, for the development, I use USB6221. Let's say that the

frequency is between 500 Hz and 10 kHz. What I am doing wrong? Or maybe better to ask - what would be the right approach for this project?Thank you

Marty

Hi Marty,

It seems that your question is already answered here, but Jason is correct that the 6221 neither the 6602 support a clock sampling for frequency measurements.

As Jason mentioned, your best bet is also likely set the mode of synchronization for "implied". This means that the frequency value is sampled at the end of each period of your input signal. In addition, a solution that is clocked by the software (On-Demand) might be acceptable.

X Series DAQ devices allow an external sample clock to use for frequency measures (described in the Manual of X series). Frequency of sample-clocked measures are useful in very specific

circumstances, but it does not seem that you need this feature based on what you've described so far.(621 x) bus-powered M series can also be configured to use an external sample as the X series clock but do you not have the same features described in the manual of the X series.

I hope this helps!

-John

-

Requested sample clock source is invalid wls-9163

My goal is to use two accelerometers that using the NI 9234 entry of the modules and wireless wls-9163 chassis.

My program is attached. Here is a photo in case you do not want to download the attachment: http://www.imagebam.com/image/577a4a195651371.

The slave device is not able to use the sample clock that came out of the master on PFI1.

I looked through the wireless DAQ resource kit and watched the following video:http://www.YouTube.com/watch?v=g_8jiKuKeDI

and ive read this: http://zone.ni.com/devzone/cda/epd/p/id/6124

I am aware that

I also tried to synchronize two cDAQ-9178 using the same methods. I always get the error "required sample clock source is not valid.

The manual says it should be able to do this

http://www.NI.com/PDF/manuals/372488c.PDF

Any help would be greatly appreciated.

Vexis,

Unfortunately, at the moment, you cannot synchronize the modules that use adelta-sigma converter (such as the NI 9234) in several cDAQ chassis. This is because these modules use a clock of sampling, which is very high; the PFI lines are unable to return to the required sample clock. You can share the start triggers, but the clocks of individual modules will drift over time.

The reason that the error message says that "requested the sample clock source is not valid" is because these modules require the use of a sample of clock that comes inside a time base clock oversampling.

Sorry for the bad news!

Katie

-

Buffer the output AO, refresh rate is different from the sample clock frequency

Hello

I am an AO output in the buffer using a single channel. I have a stamp with a ripple of 200000 points with a triangular waves of a 1000pts each repeated 200 times. If I want a frequency of 1 Hz, I simply update this waveform 1000pts and if I wanted to 5 Hz, then 5000pts and so on. But there is some frequency that I won't be able to use like the refresh rate (the number of samples that I ask to update) is different from the sample clock frequency, which makes synchronization with the other difficult to trigger (incomplete cycle). Frequency 3 Hz (update 3000pts), as (update 7000pts) 7, 6 Hz (update 6000pts), 9 (update 9000pts)... 11Hz at 15 Hz and is not valid in the sense that the refresh rate is different from the sample clock frequency. That makes a whole lot of inaccessible CONFIGURED! Can someone tell me what determines the banned frequency? Is this something to do with the material?

concerning

One thing you can try is to change the number of samples per cycle. This cannot give the precise frequency accurately, but can reduce the average error.

120 Hz, the error is currently about 400 parts per million (ppm). The accuracy of the time base is 50 ppm, then this error is less than 10 times the inherent error due to the time base.

Consider this configuration: the closest nominal sampling you rate, you can get is 120048 Hz (1000 samples per cycle at 120 Hz). If your buffer contains 1200 samples per cycle, 100 copies of it would produce 1 second of data to 120,048 Hz. But if the buffer contained an average of 1200,48 useful Samper by cycle, you get the exact frequency. Of course getting 0.48 of a sample is delicate. But the kind of feasible. If you use 48 cycles in the 1201 samples per cycle and the cycles of 52 to 1,200 samples per cycle, the total number of samples per second = 120048. Average frequency will be exactly what you want. Instantly, the frequency is slightly higher or lower than the exact value. By an alternation of 1200, 1201, 1200, 1201... 1201, 1200 100 cycles that the Jig is fast. If you group all 1200s whole and all 1201 s frequency hopping may be more sensitive. If this kind of jitter is acceptable depends strongly on what you do with the release.

This technique is used in some systems of frequency synthesizer.

Lynn

-

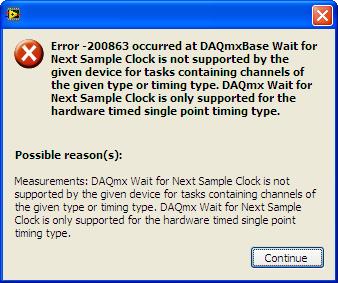

Error on wait the next sample clock

Hello

I need measure the speed using an encoder for a control application. I installed a sample external clock on CNTR0 (in another vi) and I wired CTR0_OUT to CTR1_GATE. I start the vi, then the measure of the clock vi speed sample and Labview displays the following error. I don't know what is happening, my measure is established for the sample clock and timing type single-point sample clocked by material and the error says that I do not have this? What's funny, is that the same app works if I am using the DAQ Assistant.

Thank you

David

Hey David,

I believe that the document I linked can be a problem, and I'll go ahead and make the necessary changes to be made to this document on my side.

The next issue I can see uses HWTSP on a windows machine. HWTSP is usually reserved for computers running real-time operating systems. These operating systems can ensure deterministic operations. On windows XP, windows may decide to treat another thread / process that can cause you to miss a sample (if you miss a sample that the default behavior is to throw an error).

With HWTSP, you will be difficult to get one without a real-time system faster sampling rate. Stamped acquisition will also have a large amount of latency for a control application.

Looking at your code, I recommend trying a task of sampling frequency CI On Demand. Currently, your code is the edges and conversion of frequency/RPM. In addition, because of the lag phase with your sample clock, your current configuration has an error of ±1 count. This translates to error ±1KHz (on behalf of 9 to 1 ms it would be 9 kHz, 10 would be 10 kHz, etc.). Based on mathematics in your example, you introduce ±120 rpm of error. By a frequency on the task on demand, you can ensure that whenever you call the DAQmx Read, you get the last frequency within a tick of time base error ±1. Not only it gives a better accuracy, but as long as you keep the rate of fast loop, you will ensure you get the last frequency to the fastest rate possible.

Ensure that your loop rate remains fast is to remove the loop of your acquisition processing and placing him in a parallel while loop. This is possible through the use of reporters. Local loop in Windows rates are usually in milliseconds. To get faster line rates, you might want to consider a real time operating system.

Please let me know what you think of this, and if you have any other questions, I can go into this more in detail.

-

Looking for USB DAQ for AO using the external sample clock

Hi all

I'm looking for a cheap solution for the acquisition of data to select the AO using an external digital signal as sample clock, and I just realized that the USB-6001 is not a good candidate. Please someone remind the cheapest USB version for this task? There no need for high sampling rate. Thank you.

Define cheap and low sampling rate. You've already been told on the 6211.

-

I'm trying to use a NOR-USB-6221 to implement SPI in a C++ application. When I try to configure a digital output task that uses ctr0 as the clock, I get an error stating that 'Sample clock' is not supported and use instead "on demand". I would be able to use the NOR-6221 and if so how to do this? Thank you.

Hi IntAndTest,

Maybe silly question: are you sure that you have a USB-6221 and not a USB-6212? The USB-6221 supports clocked DIO, but the USB-6212 is not working.

A problem with your code: when you specify a terminal DAQmx name, it must be is compared to the device (such as 'Ctr0InternalOutput', "AI/SampleClock" or "PFI0") or contains a slash before the device name (like "/ Dev1/Ctr0InternalOutput", "/ Dev1/AI/SampleClock ', or ' Dev1 / / PFI0"). This does not apply to the names of physical channel (like ' Dev1/port0' or "Dev1/ctr0").

The error is returned from code that you have not displayed? Your says error message DAQmxCreateDIChan failed, but the code you posted does not call this function. In addition, I don't see a call to DAQmxStartTask or DAQmxWriteDigitalU8, U16, U32, whatever.

Also, what NOR-DAQmx version are you using?

Brad

Maybe you are looking for

-

En Herramientas not me appears options

Necesito UN tutorial para seguir UN what

-

How can I make links DO NOT open outlook? And why is it so difficult to actually ask this question.

-

printer deskjet HP 2545: forgotten password wireless printer

Please help me remember my password wifi printer

-

Not clear picture... HEELLLLLPPPP!

Hi, my toshiba satellite comes to change to an unclear image, not too much but enough to hurt my eyes. He was running REALLY slowly before then I uninstalled a few programs that I thought that I didn't and I think I uninstalled something I wasn't sup

-

My DVD/CD-RW (drive E :) is not displayed in my computer more)

I tried to burn a CD, but then realized my computer has not been grateful that I put the CD, then I noticed that my drive is no longer displayed in my computer. I tried to put other CDs and DVDs in, but it still does nothing. I tried browsing around