timed loop

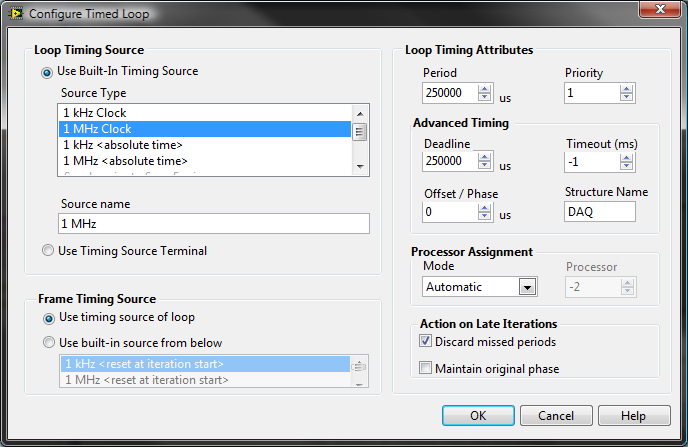

In the timed loop, the entry node was a... of entry... that called "Source name" and says that I can specify the name of the source of synchronization. What this means and how can I do? How is it when I put a constant with the same name as the name of the default Source (create > constant > "1 kHz") the loop runs only x times then stops on its own. Yet when I leave the value by default as is the loop runs until I hit the stop button?

Hi Clint,.

Yes, the moment Source.vi create will serve in the same vi. There is actually no difference between the vi and the options on the node of the loop. However the calendar source.vi creation will be used if you want to programmatically select the synchronization source.

You will find information on the configuration of the source of synchronization in the detailed help, a link to which lie at the bottom of the window context help:

"Double-click the node entry or with the right button of the structure and select Configure the timed loop to display the Configure the timed loop dialog box, where you can configure the timed loop. The values you enter in the dialog box Configure the timed loop appear next to the input on the entry node terminals. »

Thank you

Tags: NI Software

Similar Questions

-

Timed loop continues to turn after stop

Only, I have seen this time, but thought I should ask about it. After pressing the stop button, I was surprised that the diagnostic LED on the front panel of the main vi kept flashing. With the performance highlighting ONE values showed that the timed loop was still running. I checked the other 8 loops clocked subvis and they also ran. None of the methods Stop worked. Only stop LV and abandonment of the cRIO eliminated the problem.

Run LV2014 SP1 on cRIO-9067 with dual-core ARM processor. Windows 7 x 32.

BTW: The function of the check LED VI scale does not work on this device.

You must allow an order any to be able to stop your curls. A simple global variable would work well here.

-

Hello

I would like to create a FPGA loop that runs at a fixed rate. Whatever if I use a timed loop structure or a timer loop express VI into a regular while loop? Under what circumstances should I choose one over the other?

I understand that the timer loop approach can cause the code in the loop run twice before calendar is established (but this isn't a problem for me here). Are there other differences in the two approaches?

Thanks in advance.

JKSH wrote:

But my question was about the differences between the use of "multi-cycle" Timed loops and VI express loop timer.

In a targeted FPGA VI, all call loops are single cycle timed loops (SCTL). This means that all the code in a SCTL must run in a clock cycle, so there are a few types of nodes cannot be used in such a loop. In a used while loop with a timer, you can use a wider range of features, but the loop will generally run much more slowly.

These documents may be useful to learn how to use loops clocked on FPGA:

Using loops of Cycle time unique to optimize the FPGA VIs

Optimization of your screws of LabVIEW FPGA: running in parallel and Pipelining

-

In the attached VI, I put the loop timed to end once the delay 1 reaches zero. However the timed loop continues to run and stop only if I have OR both 1 and 2 delay delay. (Tried with different schedules for late 2 which are less lag 1, equal to 1 delay and more delay 1 - no chance unless it is also linked to stop)

What is the reason for this? (The VI is in LV2012)

And it is protected by word that prevents us from looking into it.

Is this your VI or did you also?

Subvi properties seem to show that it is not reentrant. Otherwise it can only run one instance at a time. And if happens to store data to leave once it is called to another in the uninitialized shift, running an instance registers is probably interfering with the execution of the other instance.

-

Structure of the event in timed loop

Quick question on the structures of timed loops\event

What is a good or a bad idea to use structures of event call loops - as opposed to while loops. ? I guess I like the idea of call loops - because you can prioritize them - so if there are some important things you need priority of 100% in the background - but for the user interface, you can configure it to run slower\or run to a different priority level.

I just wanted to check it is not a reason why I shouldn't do that - since all the examples don't do that.

JP

I don't think it's a good idea. Your timed loop can stop waiting for an event. There is no advantage of placing the structure of the event in a timed loop. It is possible to assign priorities to other objects outside of the call loops. For example, you can the priorities given to subVIs. I'm reasonably sure that the structure of the event can work at other priorities if you do not the activities of the user interface. Maybe someone of NOR can confirm this.

But the goal of a timed loop is to have a deterministic periodic job. The structure of the event must be used for asynchronous events. The two disagree with them if they are in the same spot.

-

Operating system: Windows XP

Hardware: PCI 6259

Terminals used: PFI0 and PFI2

Counters used: Ctr0 and Ctr1

IM developing an application for the acquisition of data where timed loop synchronization source comes from my PFI2 (using the string A of an encoder). IM basically trying to acquire data based on the number of ticks from my encoder. For the synchronization source, I use counter 1 to capture the rising edge and have the loop time-acquisition of data. At the same time, Im using the counter 0 to count the number of rising edges so I know exactly in what tick data was acquired. PFI0 and PFI2 are connect to channel A of the encoder.

Questions:

Timed loop acquires data at each tick, because when I discover the data (text) file is missing count of my encoder value. Is it because there is a limitation on the Windows operating system? I used a noculars to measure the frequency at the maximum rotation of the channel encoder and 6,757 kHz. All solutions?

Also, is there anyway I can route the source channel internally an encoder to generate synchronization source instead of using another counter? I have attached my VI.

Hello

All the samples that you acquire will be read by LabVIEW in a sequential manner. Figure 4-21 on the M-series on page 80 (4-34) shows that you will acquire all the samples you request all channels that you enjoy in sequentially.

-

What is error-1418 on a timed loop?

Someone at - he never had error - 1418 on the timed loop terminal error? It runs only once and I'm trying to run it on a cRIO-9004.

There is nothing in this range listed under the timed loop error codes.

http://zone.NI.com/reference/en-XX/help/371361F-01/lverror/timed_loop_error_codes/

As always, thank you

Jim

Hi Jim,.

I think that's what you're looking for:

Synchronization sources available for LabVIEW timed loop by platform

Kristen H.

-

limits of priority on a timed loop

Hello

Concerning the value of priority in a timed loop, aid said that this value must be between 1 and 65535.

Does anyone know what are these targeted limits?Thanks for your time...

Maximum for a U16: http://zone.ni.com/reference/en-XX/help/371361J-01/lvhowto/numeric_data_types_table/

-

Execution time of the timed loop

When I run a timed loop, even a dummy, I have 100% CPU usage with "RT get CPU loads. The Profiler 'Performance and memory' and "execution trace toolkit" also indicate a maximum time of VI. Is this normal?

What target RT do you use? If it's a FP, you will always have 100% of the CPU load due to the optimizatio performance.

Best regards

Fabio

-

Timed loop in loop of producer/consumer

Hello!

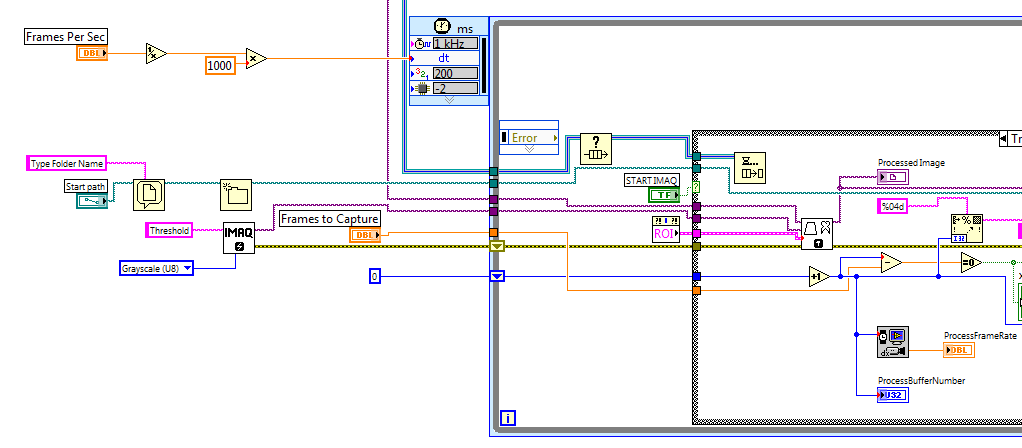

I have a loop of producer/consumer LabVIEW program configuration to allow me to properly capture the images that are large enough (8MP) at about 14 frames per second (FPS). The program works very well when the consumer loop is a while 'loop' (recorded at 14fps without problem), but I wanted to do a loop timed, so that I can vary the FPS as requires it. A curiosity arises when I do that. Anywhere under 12 fps, the loop works very well and the data is saved correctly. However, when I bump it up to 13fps, the calculated consumer FPS goes haywire and starts to jump between 9 ~ and ~ 13fps (processing of data gets bogged down?). When I set the FPS at 14, the loop runs at a constant maximum 7 fps. Is there something I can do to remedy this situation?

I have attached my .VI

Thanks in advance!

Palanski,

Are you using LabVIEW Real-time? Loops clocked to a windows OS do really increase determinism more than a while loop with a wait until the next timer multiple. Before you change the loop of producer-consumer in order to include a while loop was programming works correctly? You can also vUtiliser the VI analyizer to see how long things take to run. I let the loop of consumer to the producer in the traditional game upward and change the FPS by controlling the timer to wait, after benchmarking your code, it should be done in the same way as you did for the timed loop

-

Machine condition with timed loop?

Hello world

Is it possible to have a state machine with timed loop? i.e. on the last State, wait us here until the end of the period to return to the initial state again.

Thank you

crazycompgeek wrote:

Hello world

Is it possible to have a state machine with timed loop? i.e. on the last State, wait us here until the end of the period to return to the initial state again.

Thank you

Yes. However, when the loop is running, there is no way to stop the program or do any other action. But if this is what you want, yes it is possible.

-

OR 9403: Digital Input/Output slows timed loop?

Hi all

I use a loop timed sample of 7 current channels (NI 9023), 3-channel (NI 9025) voltage at 1000 Hz in scan mode and it works fine. However, when I add for 8 output channels of the input/output module digital module NI 9403 for timed loop, CAPAS sampling cannot exceed 1000 Hz. According with time stamp data I wroten in file, it seems that I have in all ten milliseconds, I missed a miliseconds.

I would like to ask is there a reason for this? The digital I/o module affect the timed loop?

Thank you much in advance.

I'm not familiar with the FPGA code, so I can't comment there. However, I noticed that you call writing to text file twice in the timed loop. Can you only collect data and then write the files after the time loop? This would save a lot of time. For each entry, the program needs to access the hard disk, find the end of the file, add him and return to write on the hard drive. A lot of your time, especially since the files are getting bigger.

-

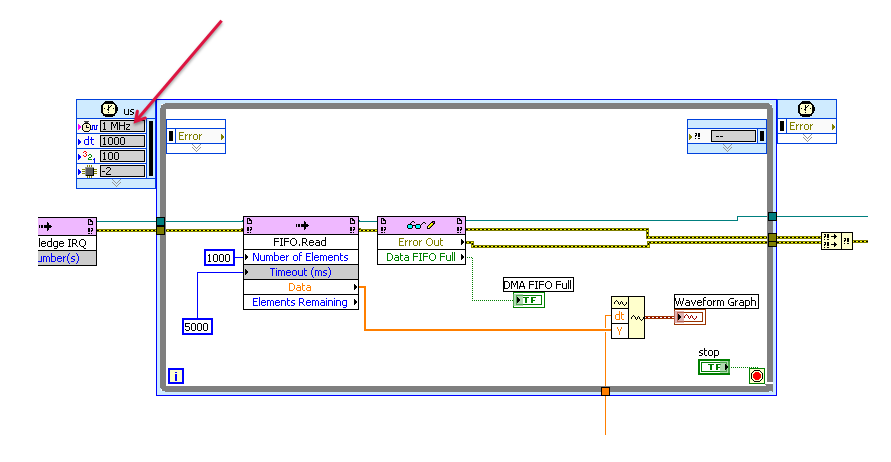

I have two codes for my NI9024 cRIO; an FPGA and a side side of RT.

In my RT code, I use a frequency of 1 MHz for my timed loop.

Just wanted to check if I should consider certain things important when using this frequency or not.

I mean, is there a particular point or referring to the fact that I had noticed.

Is there any limitation, future problem or question?

Just to be careful.

I think that the point that you are missing, it is that it is never necessary to update a graph 1000 times per second! operators just can't see that fast! So, unless you save the data on a disk, you can use a much slower pace of update. You can indeed, be limitation in this loop timed by your actual acquisition rate (timeout is 5 seconds - what is the sampling frequency of the FIFO?)

If the buffer is full or reduce the sampling frequency of the FPGA (a million points per second is really much more that a human eye can process) or increase the number of samples by reading.

-

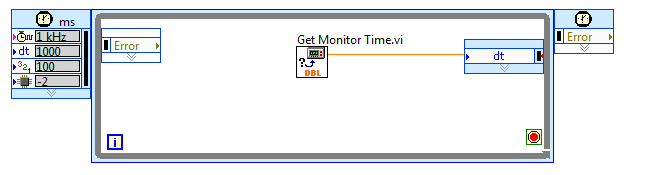

How to force a new period of a timed loop?

Hello.

Here my question:

I need to modify programmatically the period of a timed loop. This isn't a problem but:

I have to wait until the next loop to present new period value. For example if my previous period was 20 minutes, now I have to wait 20 minutes in order to submit a new period.

This beacause the code to change the period should be inside the timed loop itself. You can see what I mean in the picture as an attachment.

The Subvi Gets the new period of a console operator. It will run until the end of the period previously configured.

My question is: is it possible to force the timed loop to get the new value without waiting for the execution of the previous period?

Thank you

FPIA

Hi fpia.

Sometimes, it would be more useful to 1200 seconds instead of 20 minutes

It was suggested many times before: rather than wait for a long time with just a single call to a wait function you should divide this amount of time into smaller pieces!

-Why do not use you a period of time for example 5 and only count the iterations to know when 20 minutes are more?

-Why don't you use the function "Time" to know when to exceed the 20 minutes?

-

Sequence structure flat inside the timed loop and execution order

I have some problems trying to implement a flat sequence structure when you use a loop timed on a target of cRio VI

I tried with or without the while loop around the structure of sequence flat, and I also tried to replace the 'Non-deterministic loop' with a timed loop

The problem is that the program seems to run only once, then get stuck somewhere

I am writing a program that performs the following operations as soon as possible:

1. read the Pos_MC of entry on the FPGA

2 send the value of Pos_MC to the VI target (on cRio CPU)

3. calculate a value of output based on Pos_MC with a PID block ("exit PID')

4. send 'PID output' to the FPGA

5 write "PID output" analog output "MOOG".In addition, I want the program to return the measured value "Pos_MC" to a host VI for the recording of data

So that the output of PID is calculated and sent to the FPGA as quickly as possible, I placed a flat sequence structure to ensure that it happens before you send the output to the nondeterministic loop for recording data

Also, I want the digital input 'Stop' to be able to stop the loop deterministic (the timed loop)

I read much more entries than that and the help of several PID and exit, but I rewrote the code for a single entry and exit to make it easier to illustrate

Screenshot of the code is shown in 'target code.png' and 'fpga code.png.

The VI themselves are attached in the next post (cannot attach files of more than 3)

Question 1:

Any advice on how to get this race? Thank you!Question 2:

Is also my correct understanding in that, using this structure, each 0.9ms (fpga loop time) comes the following:

1. the input ("Pos_MOOG") is read on the fpga

2. the production of PID is calculated on the cRio with some delay to computation (for example 0.1ms)

3. the output of PID is then written for analog output "MOOG" in all about 0, 1 - 0.2ms

4. the FPGA program then waits until 0.9ms spent and repeat the processAs opposed to the next pass whenever performing a loop is started on the FPGA:

1. the FPGA reads the input and written on the output (the output of the execution of the previous loop PID)

2. then the entry is sent the cRio, PID output is calculated and sent to the FPGA

3. the new release of PID is maintained until the next time through the loop

Thank you!

PHG wrote:

Thanks for the input guys, any advice as to how I could get the feature in scenario 1?

I still say that the best route is just putting all the logic of the control in the FPGA.

Other alternatives include 1) the use of DMA FIFO sedn data back or 2) use interruptions so that the FPGA code can not read the output level until the RT.

DMA FIFOs are usually very limited, and I would not use them in this situation since I belive said it this code to do for the many outputs.

Maybe you are looking for

-

I think that discussions in the past that the general opinion on antivirus software, is that they are useless. Some time back I had a few emails Intego with severe warnings of risk and now that my subscription is coming up for renewal I wonder if the

-

No additional data in the address book

Even if my AddressBook is connected to my ICloud, where all my contacts When I opened AB, it is empty. All my contacts have disappeared

-

Can I access my money from another computer program when I'm on vacation

As above, can I access my program myMoney from another computer when I'm on vacation?

-

Vertical bars, thin, white full screen of WMP11

With the help of Dell Dimension 4700, 3 GB RAM, EVGA GeForce 8400 GS with 512 MB, Windows XP SP3, SoundSpectrum G-Force 3.9.4. When I open WMP11, then select show improvements, then close show improvements, then go to the mode full screen... There's

-

Hi, first sorry for my bad English and my possibly silly question, but I do not know how to find a similar position (due to the help of keywords). I have a router Small Business RV042 VID PID: RV042 V03 and firmware version: v4.0.4.02 - tm (July 4, 2