Timed-loop frequency of 1 MHz

I have two codes for my NI9024 cRIO; an FPGA and a side side of RT.

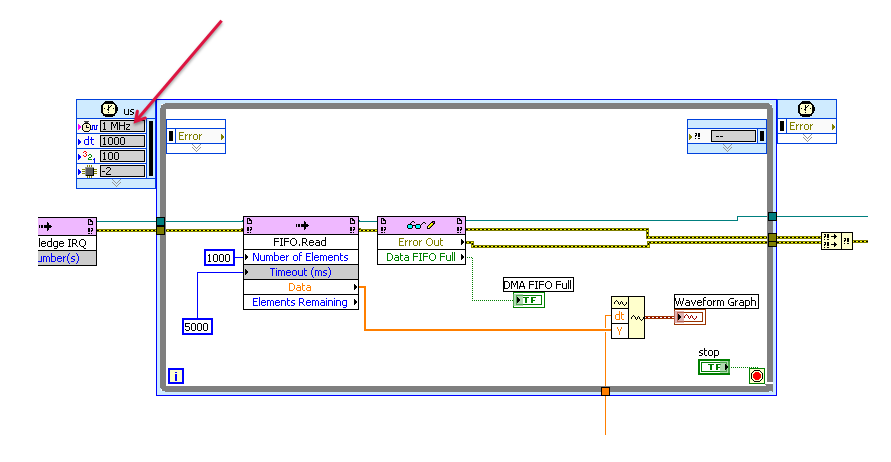

In my RT code, I use a frequency of 1 MHz for my timed loop.

Just wanted to check if I should consider certain things important when using this frequency or not.

I mean, is there a particular point or referring to the fact that I had noticed.

Is there any limitation, future problem or question?

Just to be careful.

I think that the point that you are missing, it is that it is never necessary to update a graph 1000 times per second! operators just can't see that fast! So, unless you save the data on a disk, you can use a much slower pace of update. You can indeed, be limitation in this loop timed by your actual acquisition rate (timeout is 5 seconds - what is the sampling frequency of the FIFO?)

If the buffer is full or reduce the sampling frequency of the FPGA (a million points per second is really much more that a human eye can process) or increase the number of samples by reading.

Tags: NI Software

Similar Questions

-

Module speed FPGA, speed controller and timed loop speed

Hello.

I'm developing an application to acquire an analog signal at 800kS/s. Budget does not seem to be enough buy material excess spec. So I have to be very very accurate on all components. I had a look on the site and selected the following materials.

9221 8 module capable analog channel on 800kS/s sampling. I don't know if this sampling rate indicated in the specification of the module means that it can acquire up to 800kS/s or is the device samples ADC sampling rate to which the machine don't maybe not to the criteria of Nyquist and the module can perform sampling to 1.6MS / s is necessary which I think is not available?

9012-400 MHZ controller controller. If I put a while loop inside a VI under the RT target, it runs at 400 MHZ by default provided there is no code inside? Is so I could definitely use loop time express vi for sampling at the required level.

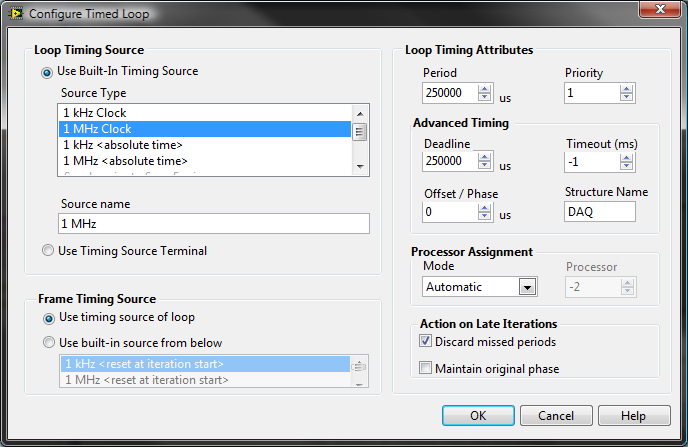

What of the timed loop? I just developed a project of RT and added vi under the RT target. The timed loop default clock frequency is 1 kHz and I can't select more than 1 MHz?

9112 chassis. Default clock 40 MHz. same rate issue which concerns the 9012 above controller.

Kind regards

Hi AustinCann

If you need to acquire 800 kech. / s, then the module module-9221 will be able to do this, if you are using only 1 channel, that is. The module using a global sample, therefore the maximum rate will be distributed on channels that you use.

If, however, you have to detect the frequency of > 400 then you would need a higher sampling rate to detect these, as you mentioned.

The controller processor runs at 400 MHz, even though the loops in your code will not run at this pace. On the target in real time, you can use a timed sources of clock - usually 1 kHz to 1 MHz - and set the period in terms of the chosen clock. If you need faster line rates, you can still code directly on the FPGA. The CompactRIO Developers Guide is a comprensive document and deals with most of the concepts of RT and FPGA.

The best course of action would be to contact your local office, because they have all the resources necessary for the specification of your system.

-

Operating system: Windows XP

Hardware: PCI 6259

Terminals used: PFI0 and PFI2

Counters used: Ctr0 and Ctr1

IM developing an application for the acquisition of data where timed loop synchronization source comes from my PFI2 (using the string A of an encoder). IM basically trying to acquire data based on the number of ticks from my encoder. For the synchronization source, I use counter 1 to capture the rising edge and have the loop time-acquisition of data. At the same time, Im using the counter 0 to count the number of rising edges so I know exactly in what tick data was acquired. PFI0 and PFI2 are connect to channel A of the encoder.

Questions:

Timed loop acquires data at each tick, because when I discover the data (text) file is missing count of my encoder value. Is it because there is a limitation on the Windows operating system? I used a noculars to measure the frequency at the maximum rotation of the channel encoder and 6,757 kHz. All solutions?

Also, is there anyway I can route the source channel internally an encoder to generate synchronization source instead of using another counter? I have attached my VI.

Hello

All the samples that you acquire will be read by LabVIEW in a sequential manner. Figure 4-21 on the M-series on page 80 (4-34) shows that you will acquire all the samples you request all channels that you enjoy in sequentially.

-

Satellite L30-134: is it possible to determine the frequency of 533 MHz RAM?

Hello!

I have Satellite L30-134 and used a module of 1 GB / 667 MHz (sic!) for a while. Same Toshiba says maximum speed 533 MHz memory he recognizes module PC-5300 and sets exactly to 667 MHz.

I decided to increase the RAM and bought another PC-5300 1 GB stick.

... RAM is only 1 GB with two modules together. The two sticks are OK - L30 sees 1 GB and works well with each of them separately.I know that the reason is that Toshiba couldn't work with greater speed on the two banks (or something like that).

So. It seems to be a good idea to set the frequency of 533 MHz and it should work.

The only question is to know how to do it? BIOS Setup is almost empty and does not have these settings.One advise, please (except to buy sticks more :)

Hello

Laptop Satellite L30-134 is a processor 1.5 GHz of Intel-Celeron-M (Yonah).

Is this good?This processor supports a 533 Mhz bus and if you use modules of 533 Mhz RAM then will automatically solve this value!

Simply put, you do not need to change anything manually! Everything is controlled automatically.Concerning

-

Timed loop continues to turn after stop

Only, I have seen this time, but thought I should ask about it. After pressing the stop button, I was surprised that the diagnostic LED on the front panel of the main vi kept flashing. With the performance highlighting ONE values showed that the timed loop was still running. I checked the other 8 loops clocked subvis and they also ran. None of the methods Stop worked. Only stop LV and abandonment of the cRIO eliminated the problem.

Run LV2014 SP1 on cRIO-9067 with dual-core ARM processor. Windows 7 x 32.

BTW: The function of the check LED VI scale does not work on this device.

You must allow an order any to be able to stop your curls. A simple global variable would work well here.

-

Hello

I would like to create a FPGA loop that runs at a fixed rate. Whatever if I use a timed loop structure or a timer loop express VI into a regular while loop? Under what circumstances should I choose one over the other?

I understand that the timer loop approach can cause the code in the loop run twice before calendar is established (but this isn't a problem for me here). Are there other differences in the two approaches?

Thanks in advance.

JKSH wrote:

But my question was about the differences between the use of "multi-cycle" Timed loops and VI express loop timer.

In a targeted FPGA VI, all call loops are single cycle timed loops (SCTL). This means that all the code in a SCTL must run in a clock cycle, so there are a few types of nodes cannot be used in such a loop. In a used while loop with a timer, you can use a wider range of features, but the loop will generally run much more slowly.

These documents may be useful to learn how to use loops clocked on FPGA:

Using loops of Cycle time unique to optimize the FPGA VIs

Optimization of your screws of LabVIEW FPGA: running in parallel and Pipelining

-

In the attached VI, I put the loop timed to end once the delay 1 reaches zero. However the timed loop continues to run and stop only if I have OR both 1 and 2 delay delay. (Tried with different schedules for late 2 which are less lag 1, equal to 1 delay and more delay 1 - no chance unless it is also linked to stop)

What is the reason for this? (The VI is in LV2012)

And it is protected by word that prevents us from looking into it.

Is this your VI or did you also?

Subvi properties seem to show that it is not reentrant. Otherwise it can only run one instance at a time. And if happens to store data to leave once it is called to another in the uninitialized shift, running an instance registers is probably interfering with the execution of the other instance.

-

Structure of the event in timed loop

Quick question on the structures of timed loops\event

What is a good or a bad idea to use structures of event call loops - as opposed to while loops. ? I guess I like the idea of call loops - because you can prioritize them - so if there are some important things you need priority of 100% in the background - but for the user interface, you can configure it to run slower\or run to a different priority level.

I just wanted to check it is not a reason why I shouldn't do that - since all the examples don't do that.

JP

I don't think it's a good idea. Your timed loop can stop waiting for an event. There is no advantage of placing the structure of the event in a timed loop. It is possible to assign priorities to other objects outside of the call loops. For example, you can the priorities given to subVIs. I'm reasonably sure that the structure of the event can work at other priorities if you do not the activities of the user interface. Maybe someone of NOR can confirm this.

But the goal of a timed loop is to have a deterministic periodic job. The structure of the event must be used for asynchronous events. The two disagree with them if they are in the same spot.

-

In the timed loop, the entry node was a... of entry... that called "Source name" and says that I can specify the name of the source of synchronization. What this means and how can I do? How is it when I put a constant with the same name as the name of the default Source (create > constant > "1 kHz") the loop runs only x times then stops on its own. Yet when I leave the value by default as is the loop runs until I hit the stop button?

Hi Clint,.

Yes, the moment Source.vi create will serve in the same vi. There is actually no difference between the vi and the options on the node of the loop. However the calendar source.vi creation will be used if you want to programmatically select the synchronization source.

You will find information on the configuration of the source of synchronization in the detailed help, a link to which lie at the bottom of the window context help:

"Double-click the node entry or with the right button of the structure and select Configure the timed loop to display the Configure the timed loop dialog box, where you can configure the timed loop. The values you enter in the dialog box Configure the timed loop appear next to the input on the entry node terminals. »

Thank you

-

What is error-1418 on a timed loop?

Someone at - he never had error - 1418 on the timed loop terminal error? It runs only once and I'm trying to run it on a cRIO-9004.

There is nothing in this range listed under the timed loop error codes.

http://zone.NI.com/reference/en-XX/help/371361F-01/lverror/timed_loop_error_codes/

As always, thank you

Jim

Hi Jim,.

I think that's what you're looking for:

Synchronization sources available for LabVIEW timed loop by platform

Kristen H.

-

limits of priority on a timed loop

Hello

Concerning the value of priority in a timed loop, aid said that this value must be between 1 and 65535.

Does anyone know what are these targeted limits?Thanks for your time...

Maximum for a U16: http://zone.ni.com/reference/en-XX/help/371361J-01/lvhowto/numeric_data_types_table/

-

Execution time of the timed loop

When I run a timed loop, even a dummy, I have 100% CPU usage with "RT get CPU loads. The Profiler 'Performance and memory' and "execution trace toolkit" also indicate a maximum time of VI. Is this normal?

What target RT do you use? If it's a FP, you will always have 100% of the CPU load due to the optimizatio performance.

Best regards

Fabio

-

Timed loop in loop of producer/consumer

Hello!

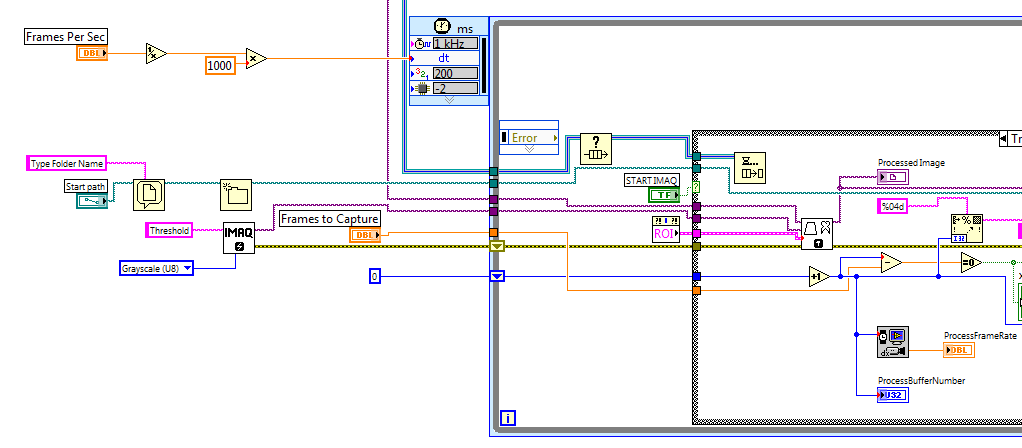

I have a loop of producer/consumer LabVIEW program configuration to allow me to properly capture the images that are large enough (8MP) at about 14 frames per second (FPS). The program works very well when the consumer loop is a while 'loop' (recorded at 14fps without problem), but I wanted to do a loop timed, so that I can vary the FPS as requires it. A curiosity arises when I do that. Anywhere under 12 fps, the loop works very well and the data is saved correctly. However, when I bump it up to 13fps, the calculated consumer FPS goes haywire and starts to jump between 9 ~ and ~ 13fps (processing of data gets bogged down?). When I set the FPS at 14, the loop runs at a constant maximum 7 fps. Is there something I can do to remedy this situation?

I have attached my .VI

Thanks in advance!

Palanski,

Are you using LabVIEW Real-time? Loops clocked to a windows OS do really increase determinism more than a while loop with a wait until the next timer multiple. Before you change the loop of producer-consumer in order to include a while loop was programming works correctly? You can also vUtiliser the VI analyizer to see how long things take to run. I let the loop of consumer to the producer in the traditional game upward and change the FPS by controlling the timer to wait, after benchmarking your code, it should be done in the same way as you did for the timed loop

-

Machine condition with timed loop?

Hello world

Is it possible to have a state machine with timed loop? i.e. on the last State, wait us here until the end of the period to return to the initial state again.

Thank you

crazycompgeek wrote:

Hello world

Is it possible to have a state machine with timed loop? i.e. on the last State, wait us here until the end of the period to return to the initial state again.

Thank you

Yes. However, when the loop is running, there is no way to stop the program or do any other action. But if this is what you want, yes it is possible.

-

OR 9403: Digital Input/Output slows timed loop?

Hi all

I use a loop timed sample of 7 current channels (NI 9023), 3-channel (NI 9025) voltage at 1000 Hz in scan mode and it works fine. However, when I add for 8 output channels of the input/output module digital module NI 9403 for timed loop, CAPAS sampling cannot exceed 1000 Hz. According with time stamp data I wroten in file, it seems that I have in all ten milliseconds, I missed a miliseconds.

I would like to ask is there a reason for this? The digital I/o module affect the timed loop?

Thank you much in advance.

I'm not familiar with the FPGA code, so I can't comment there. However, I noticed that you call writing to text file twice in the timed loop. Can you only collect data and then write the files after the time loop? This would save a lot of time. For each entry, the program needs to access the hard disk, find the end of the file, add him and return to write on the hard drive. A lot of your time, especially since the files are getting bigger.

Maybe you are looking for

-

MSN does not meet the methods to transfer from Internet Explorer.

-

Keyboard on my satellite error - 'L' key seems to be stuck, forces logut

Hello I'm fixing a satellite phone with a keyboard error, the 'L' key seems to be stuck permanently down, except that it's not! Also by clicking on the button start requires the user to be disconnected and returned the the login screen. The keyboard

-

550-153no Pavilion: four screens on a HP Pavilion 550-153no

I just bought a HP Pavilion 153no 550, and I want to connect four screens. (Not necessary for the use of heavy graphics, just for business applications). Can I remove the supplied AMD Radeon R5 330 and install a cheap graphics card which can drive tw

-

Sims3: someone can give me a few steps for the sims3 on a windows vista installation?

Can someone give me a few steps for the sims3 on a windows vista installation?

-

I had a problem with my AcerPower F2 Windows XP Professional. You will work and it stops just and restart on it. What could be causing it to do this? A virus? I use this computer a lot for school I hope its something fixable. He has had this problem