Timed loops with visa

Hi, I'm new in labview and I need help.

I have a microscope shutter which is controlled by VISA.

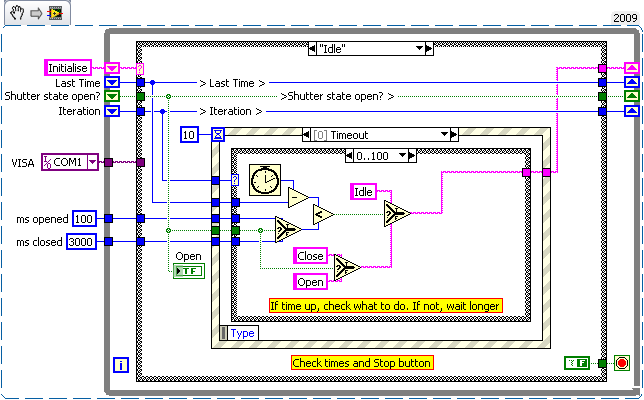

I want this component to open for X milliseconds (eg. 100 milliseconds) and then close, wait W dry (eg. 3 seconds) until it opens again expect the same milliseconds X so that it closes and wait W dry again and so on. And I want to repeat this cycle Z time (eg. 100 times). I use the shift operators in a time loop, but I can't stop the loop in the middle of the operation.

Thank you

Carlos

Hi Carlos,

Under the name of Raven suggested would be the way to go. I have attached a first draft of this thing with the necessary documentation. If something is not clear, feel free to ask.

Tags: NI Software

Similar Questions

-

Most of the machine control software I design have the following structure:

1. There's a HAND that takes place inside a TIMED LOOP with synchronization of 50ms and priority of 100. His only job is to read / write data from / to DAQMx IO cards.

2. the MAJOR can call several SUBs based on the choice of the user, and once a submarine is called FP MAIN is closed and the FP SUB opens. All submarines have a States Queued Machine running within a TIMED LOOP with 50ms timing but with priority to 50.

3. data transfer between HAND / SUB is through function globals - there are many of them based on past data.

4. all woks fine so far. No need to any RTOS. and platform of WIN7 is alomost standard. I even ran with a timing of 20ms without anything crashing...

Problem: When there are a lot of file i/o operations in a SUB partciluar, then I have the chance to see several missed iterations. Perhaps the TIMED LOOP is hogging resources.

What I want to do: convert both TIMED in asnd SUB HAND loops simple while loops. But I am concerned by the priority - since the MAIN interacts with HW there priority. But with LOOP WHILE how can I ensure this?

Or is there any replacement / effective way of doing what I do now?

Rama wrote:

.... FGV should be thrown out the window...

Well used for a while, based on many articles in the KB. One of them is locked... and it does not represent the engine of the Action or of the FGV as a villain to avoid.

The driving force is one of the largest buildings in LabVIEW. The FGV who does nothing but Get and Set (or writing and reading) is useless and a waste of resources. Why? It does nothing to fix possible race conditions (does not protect critical sections) and it is much slower than just using a global variable. See this example I put in place to see what I mean: an overview of the race Conditions.

Rama wrote:

So in the sample that I had attached, what do you think would happen if I just replaced the two loops with the SAME timed in MAIN and SUB wait value ms. is there a work order then?

When things are at the same time, there is no such thing as the order of execution. But as I said, it seems that your loop is quite slow, so it's something I would not worry. Just make sure that you do not have a loop that uses all the CPU.

-

Timed loop first iteration to fast

A timed loop is used to create a calendar suitable for data acquisition. The structure has been tested with a period of 1 000 ms and each loop takes 1 000 ms except the first flowing through the ms. a little my expectation was of course ms 1 000 the same for the first loop. I need the measures to be equally separated in time from the very first point. How to solve this? Is there information on the behavior of NEITHER?

Windows XP.

LabVIEW 2010.

Hasun,

try to use the shift / timing settings phase timed loop.with 1000ms.

-

Leak memory in real time caused by VISA Read and timed loop of data nodes? Is not supposed.

In collaboration with LV 8.2.1 in real time to develop applications that monitor or emulate computers on bus RS-422. The following screenshots have been taken an application that monitors a transmission of 200 Hz. After a few hours, the PXI station would break a range impressive messages angry... most involving something about memory loss. After much hair pulling and passing money, my partner has discovered while looking at the available memory on the controller of loss of memory occurred at each loop containing a VISA read and propagation of error using the data nodes (see Leak.jpg of memory). He concluded that if he went to the propagation of the error to the regular old shift registers, then the available memory was rock-solid. (has the Leak.jpg of No memory)

Any ideas of what could be the cause? Do you see not any problem with the way that we code these kinds of loops? We always strive to optimize the way in which we use the memory on our urgent requests and VISA readings and DAQmx bed give us the heartache more than ever, we are able to allocate memory for these screws some tips?

Dan Marlow

GDLS

Hi thisisnotadream,

This problem has been reported, and you seem to be exactly reproduce the conditions required to see this problem. This was reported to R & D (# 134314) for further investigations. There are several possible solutions, of which one is the one you have already found the wiring error directly in the loop. Other situations which give rise to no memory leak are:

1 if the bytes of the property node port is not there and has read lies in each iteration and time-outs resulting are ignored.

2. If the structure of the deal is gone and just blindly check the bytes to the port and read each iteration.

3. If the timed loop is transformed into a while loop.

Thanks for the comments!

Kind regards

Stephen S.

-

Machine condition with timed loop?

Hello world

Is it possible to have a state machine with timed loop? i.e. on the last State, wait us here until the end of the period to return to the initial state again.

Thank you

crazycompgeek wrote:

Hello world

Is it possible to have a state machine with timed loop? i.e. on the last State, wait us here until the end of the period to return to the initial state again.

Thank you

Yes. However, when the loop is running, there is no way to stop the program or do any other action. But if this is what you want, yes it is possible.

-

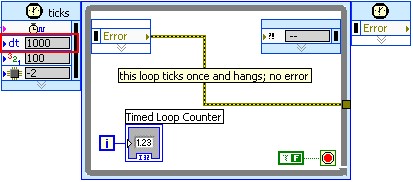

Timed loop runs only once with pulse train?

It is a VI that attempts to drive a loop timed with a train of pulses 6608 OR map attached. My timed loop never appears to run more than one cycle. No error is reported. I suspect it's because I'm not set up correctly with NOR-DAQ. Any help would be most appreciated.

WB

Hi Wb,

Take a look near the timed loop, I can see that the value of dt period is set to 1000. This period is used to scale based on synchronization source units. In this case, the clock contains 0.5 second pulses. Change the dt to a value of 2 has allowed me to see the timed structure to go as planned. See the image below for more details:

I hope this helps. Let me know if this behaves that way even on your system.

See you soon!

-

Hello

I would like to create a FPGA loop that runs at a fixed rate. Whatever if I use a timed loop structure or a timer loop express VI into a regular while loop? Under what circumstances should I choose one over the other?

I understand that the timer loop approach can cause the code in the loop run twice before calendar is established (but this isn't a problem for me here). Are there other differences in the two approaches?

Thanks in advance.

JKSH wrote:

But my question was about the differences between the use of "multi-cycle" Timed loops and VI express loop timer.

In a targeted FPGA VI, all call loops are single cycle timed loops (SCTL). This means that all the code in a SCTL must run in a clock cycle, so there are a few types of nodes cannot be used in such a loop. In a used while loop with a timer, you can use a wider range of features, but the loop will generally run much more slowly.

These documents may be useful to learn how to use loops clocked on FPGA:

Using loops of Cycle time unique to optimize the FPGA VIs

Optimization of your screws of LabVIEW FPGA: running in parallel and Pipelining

-

Timed loop continues to turn after stop

Only, I have seen this time, but thought I should ask about it. After pressing the stop button, I was surprised that the diagnostic LED on the front panel of the main vi kept flashing. With the performance highlighting ONE values showed that the timed loop was still running. I checked the other 8 loops clocked subvis and they also ran. None of the methods Stop worked. Only stop LV and abandonment of the cRIO eliminated the problem.

Run LV2014 SP1 on cRIO-9067 with dual-core ARM processor. Windows 7 x 32.

BTW: The function of the check LED VI scale does not work on this device.

You must allow an order any to be able to stop your curls. A simple global variable would work well here.

-

In the attached VI, I put the loop timed to end once the delay 1 reaches zero. However the timed loop continues to run and stop only if I have OR both 1 and 2 delay delay. (Tried with different schedules for late 2 which are less lag 1, equal to 1 delay and more delay 1 - no chance unless it is also linked to stop)

What is the reason for this? (The VI is in LV2012)

And it is protected by word that prevents us from looking into it.

Is this your VI or did you also?

Subvi properties seem to show that it is not reentrant. Otherwise it can only run one instance at a time. And if happens to store data to leave once it is called to another in the uninitialized shift, running an instance registers is probably interfering with the execution of the other instance.

-

Structure of the event in timed loop

Quick question on the structures of timed loops\event

What is a good or a bad idea to use structures of event call loops - as opposed to while loops. ? I guess I like the idea of call loops - because you can prioritize them - so if there are some important things you need priority of 100% in the background - but for the user interface, you can configure it to run slower\or run to a different priority level.

I just wanted to check it is not a reason why I shouldn't do that - since all the examples don't do that.

JP

I don't think it's a good idea. Your timed loop can stop waiting for an event. There is no advantage of placing the structure of the event in a timed loop. It is possible to assign priorities to other objects outside of the call loops. For example, you can the priorities given to subVIs. I'm reasonably sure that the structure of the event can work at other priorities if you do not the activities of the user interface. Maybe someone of NOR can confirm this.

But the goal of a timed loop is to have a deterministic periodic job. The structure of the event must be used for asynchronous events. The two disagree with them if they are in the same spot.

-

In the timed loop, the entry node was a... of entry... that called "Source name" and says that I can specify the name of the source of synchronization. What this means and how can I do? How is it when I put a constant with the same name as the name of the default Source (create > constant > "1 kHz") the loop runs only x times then stops on its own. Yet when I leave the value by default as is the loop runs until I hit the stop button?

Hi Clint,.

Yes, the moment Source.vi create will serve in the same vi. There is actually no difference between the vi and the options on the node of the loop. However the calendar source.vi creation will be used if you want to programmatically select the synchronization source.

You will find information on the configuration of the source of synchronization in the detailed help, a link to which lie at the bottom of the window context help:

"Double-click the node entry or with the right button of the structure and select Configure the timed loop to display the Configure the timed loop dialog box, where you can configure the timed loop. The values you enter in the dialog box Configure the timed loop appear next to the input on the entry node terminals. »

Thank you

-

Execution time of the timed loop

When I run a timed loop, even a dummy, I have 100% CPU usage with "RT get CPU loads. The Profiler 'Performance and memory' and "execution trace toolkit" also indicate a maximum time of VI. Is this normal?

What target RT do you use? If it's a FP, you will always have 100% of the CPU load due to the optimizatio performance.

Best regards

Fabio

-

Can't see the terminal emulator port after all control with VISA

Hello

I created a LabVIEW VI to control cycle to PWM channels on a microcontroller FRDM KE02Z reports. The microcontroller, programmed in CodeWarrior, is set up to receive an an input of the terminal string and break it in two parts (the channel name and ratio), which are then applied to the PWM. The code works and I tested with the 2.9 Termite and a Logic Analyzer before ordering through LabVIEW. The problem I had, though, is that I have to completely close LabVIEW to see the port on the new Termite and vice versa.

Previously, I had problems with VI after I something else in it, even a VI almost identical, more open as he was using the same port. I get errors and be unable to get my VI to work again unless I restarted LabVIEW. I was able to fix by adding a VISA flush the IO buffer according to a discussion earlier (http://forums.ni.com/t5/LabVIEW/Timing-issues-with-Serial-Read-Write-can-t-achieve-terminal/m-p/2636... once the configuration of the Port series and at least now I can jump between the screws I am still unable to see the port jumps between LabVIEW and termite, unless I close one;) Close VISA and the closure of the VI are not enough, I must close LabVIEW himself. Is it possible to achieve only within the VI? For example using a VISA or VISA clear Flush at the end (after closing VISA)? If Yes, what is the difference/preference between them?

As I mentioned previously, the VI is functional, but I would like to know what is happening for future considerations. Would appreciate any advice.

Hope to hear from you,

Yusif NurizadeYou have not wired resource VISA through the stop event name so it doesn't close anything.

-

How to exit while loop with delay schedule?

I have a pretty heavy program that iteratively takes a series of measures from a number of channels using a variety OR-Switch and OR-DMM screws that I assembled as a result of various examples and several help pages. Each channel is sampled once during each iteration with data to be saved in a text file for later analysis, after it is imported into Excel. I added to the screen 'real time' indicators and charts to see what looks like running data.

Each iteration is performed using a While loop with a delay timer, even if a previous version, I used a timed loop. Measures for the series of channels are collected with a loop For inside the While loop. The loop For includes screws which:

1 cut the channel and wait as debounce.

2 Initializes the DMM and passes the configuration information.

3. wait for a while to make sure that the DMM is set.

4. measure.

5. close the DMM.

6 disconnect all the switches.

The terms of the election of the channels is ends in 15-20 seconds and I am currently collecting data every two minutes, so he spends "wait" time "collection". Each iteration of the loop For initializes and closes the DMM to avoid the hot switch.

Other components of the program are configuration setting controls, etc. (in front of the While loop), a "current measurement" indicator and a writing-text inside the loop file operation For, several indicators of the iteration (inside the While loop, but outside the loop For) and a bunch of operations related to the grouping and table that provide graphics of groups of time vs measures.

I don't know there are more elegant ways to perform many functions that I do and I'm not posting the VI here because I want to concentrate on what I know, it's a big problem with my program (for now!) - I can't figure out how to get out of the While loop. I tried the combinations of Boolean control, its conditions of latch and Stop / continuous if true to nothing does not.

I want a 'Stop' button that ends the While loop, at the next opportunity, but it is not working properly, I think, because the stop button does not play with good timing, because the program runs either the loop For or the time delay at the beginning of the While loop. 'Next opportunity' can mean 'Immediately', 'at the end of the next iteration of the loop,"or"at the end of the next delay schedule." I think that if I get one of these scenarios to work, I can get an any of them to work!

Help, please!

-

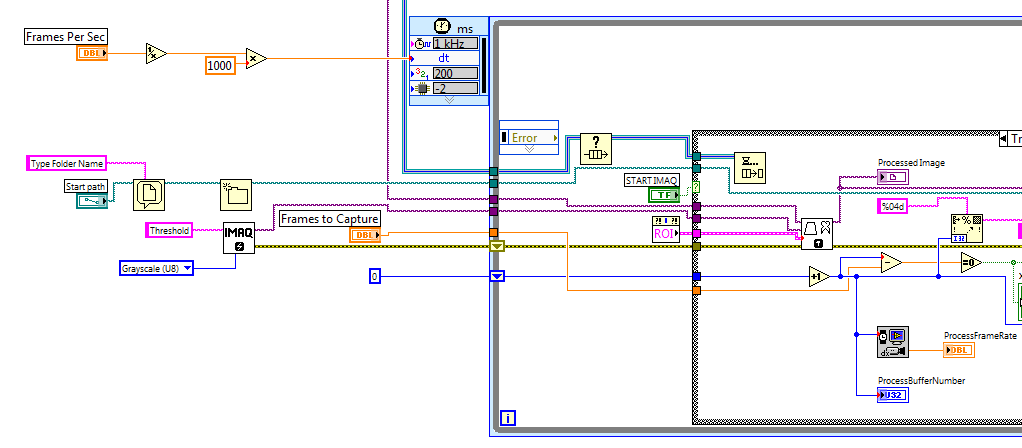

Timed loop in loop of producer/consumer

Hello!

I have a loop of producer/consumer LabVIEW program configuration to allow me to properly capture the images that are large enough (8MP) at about 14 frames per second (FPS). The program works very well when the consumer loop is a while 'loop' (recorded at 14fps without problem), but I wanted to do a loop timed, so that I can vary the FPS as requires it. A curiosity arises when I do that. Anywhere under 12 fps, the loop works very well and the data is saved correctly. However, when I bump it up to 13fps, the calculated consumer FPS goes haywire and starts to jump between 9 ~ and ~ 13fps (processing of data gets bogged down?). When I set the FPS at 14, the loop runs at a constant maximum 7 fps. Is there something I can do to remedy this situation?

I have attached my .VI

Thanks in advance!

Palanski,

Are you using LabVIEW Real-time? Loops clocked to a windows OS do really increase determinism more than a while loop with a wait until the next timer multiple. Before you change the loop of producer-consumer in order to include a while loop was programming works correctly? You can also vUtiliser the VI analyizer to see how long things take to run. I let the loop of consumer to the producer in the traditional game upward and change the FPS by controlling the timer to wait, after benchmarking your code, it should be done in the same way as you did for the timed loop

Maybe you are looking for

-

Qosmio F60-111 - HARD drive replacement

I have a F60-111 and he had a problem bad hard drive several months ago, he was not even a year and was already late and crashing all the time. I have 3 years international warranty for it, so I sent the laptop in Saudi Arabia and the hard drive was

-

The system time has changed after the restart of Bootcamp

Hello After a restart of the boot camp partition Windows 10. I have the wrong time, in fact its always an hour later that it is. Although in the Control Panel, I checked the "time of to of Appleserver" it does not update the time of its actual value.

-

Want to 6 1010sv: Intel rapid storage 10 Windows software/driver

Hello everyone! I noticed that Intel Rapid Storage process (32 bit) crazy sometimes, consuming a lot of CPU and RAM. In addition the control application storage quick, accessible via the Control Panel does not start. I would like to reinstall the dri

-

U8 array used in digital form with 0.1 Hz for each array index

Hello I am trying to write a code that allows me to output an array of 36'000 U8 values to an NI USB-6009 digital output. The problem starts as soon as I try to set the clock should be 0.1 Hz send me 3600 seconds on my 36 k samples. Looks like it's n

-

How windows ask me password when I open a session?

original title: password Hello.. IM currently running windows vista Home premium sp2 with acer bio protection... everything was ok, but the system now don't ask me the password to windows connect when I open windows... but when I disconnect or change