USRP RIO as BS and EU

Is it possible to use USRP RIO for BS and EU side? Several USRP Siu can connect to NBS?

Hi varugantigopal,

It is certainly possible to use USRP RIOs for the EU and the BS and for several Siu to connect with NBS. Our MIMO Massive reference design, for example, uses up to 64 USRP RIOs the BS and 6 USRP RIOs to the equivalent of 12 Siu.

Tags: NI Products

Similar Questions

-

Muliple USRP RIO 2943R, synchronization and phase-locking problem

I use 8 USRP RIO 2943Rs transmission of signal and receving (4 for Tx) and 4 for Rx I'm using the "signal-based" method for synchronization of all devices. And I did it. I tested the system the result is very interesting:

1. when I put the sampling rate of less than 40MS/s IQ, I can obversve very good phase locked Tx and Rx signals (I use a sine wave CW for tests), please refer to video joint (locked 40MSs)

2. BUT, when I put the IQ more than 60 MS/s sampling rate, I'll lose phase lock. Please refer to unlocked 60MSs. My goal is to run the system at 120MS/s

I have doubt as to if the problem comes from two sides:

a. the sync methed isn't fair

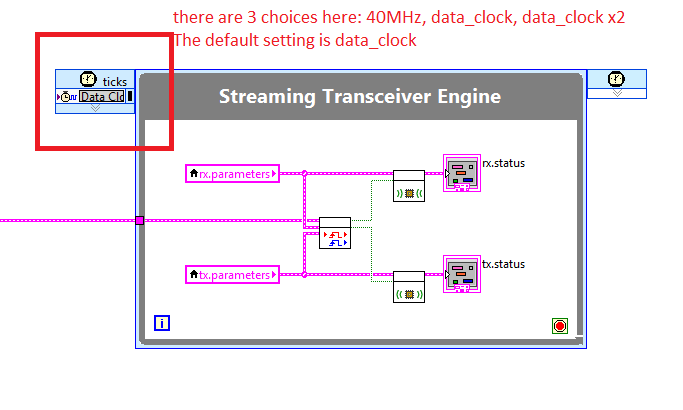

b. OR, should I increase the clock that operates the loop 'In Streaming radio engine' in the FPGA VI. as shown in the following image.I would like to ask experts in the forum to discuss the solution of this problem.

More information about my system setting:

-

Problem of generation of Sync trigger in several synchronization USRP RIO 2943R problem

Generation problem shutter Sync in several synchronization USRP RIO 2943R problem.

Previous SR you may already know I'm stacked in USRP RIO multiple synchronization problem, especially in the mode based on the signal. Now I can cut down, the problem is mainly due to the outbreak of sync signals generation.

First of all, I read the article and the discussion in the following two links:

http://forums.NI.com/T5/USRP-software-radio/how-to-synchronize-multiple-USRP-Rio-294x-devices/TD-p/3...

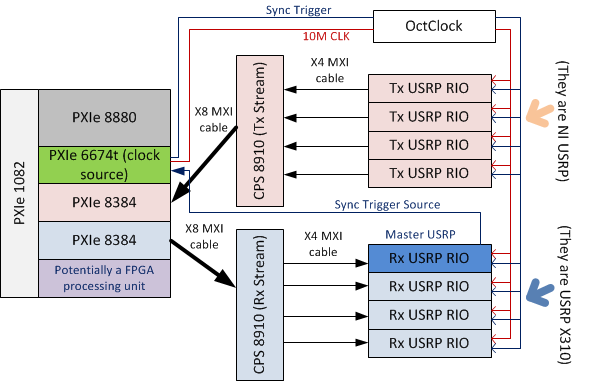

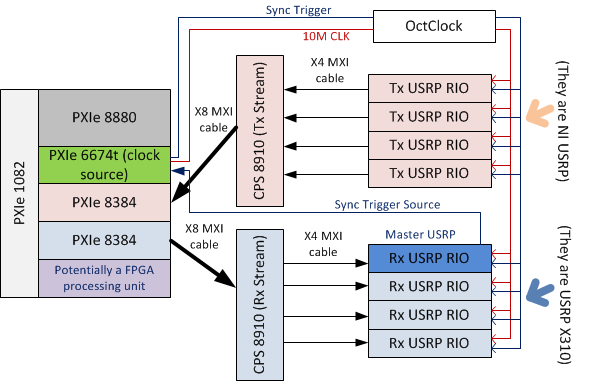

http://zone.NI.com/reference/en-XX/help/373380D-01/usrphelp/synchronization/and I did my connection of the material according to the suggestions in the second link. My system schematic is shown in the following image:

I checked OctColck and SMU 6674 T connections. They are all connected correctly and the cable are fine. I use the niUsrpRio200_XcvrSyncPps.lvbitx.

According to the description of documents and discussion forum, the USRP RIO 1st in the list of devices are considered to be the USRP Master. Then, the FPGA to master USRP RIO released "trigger of sync" signal through the 'PPS Trigger Out' SMA port in RIO USRP box.

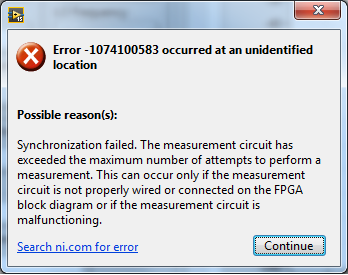

Based on the my analysis of the system, the first impression I have is the USRP Master does not export the 'sync trigger' correctly. The host VI reports the error like this:I was trying to measure the "synchronization trigger" using oscilloscope, but I found that it is impossible, because the host VI can not yet run, so there is that no signal can be seen from port 'PPS Trigger OUT.

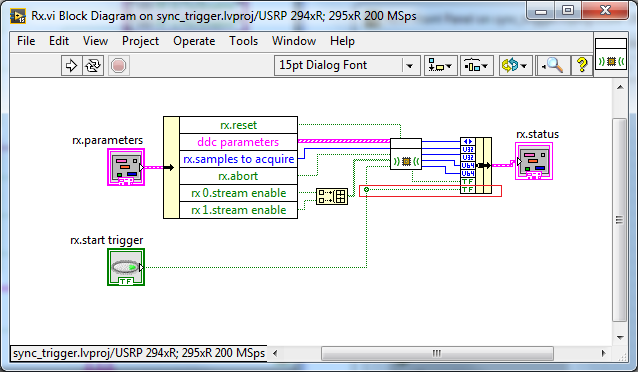

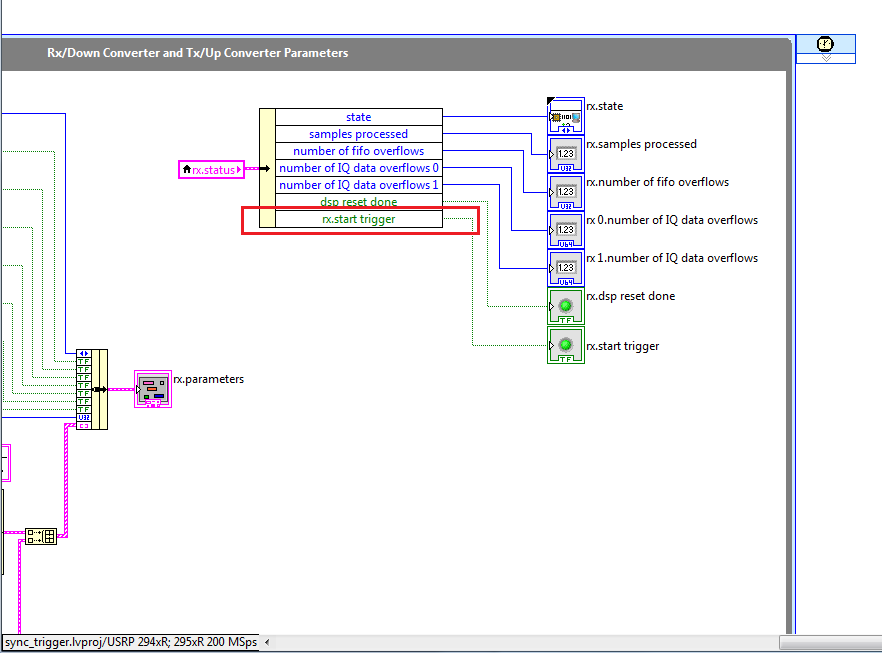

So I think that if I can watch this signal "sync trigger" in home VI by importing this signal from FPGA to host VI. I did some changes on the FPGA VI as shown in the following image to watch this signal of façade of the host VI. but not so successful. the rx.start tragger relaxation and tx.start do not appear on the host vi read/write control function.

-

USRP RIO 2953R firmware update

Hello world

We use NI USRP RIO 2953R with LabView 32bits. We are trying to run the example, the VI "niUSRP EX Rx Async.vi continues", but it returns an error in the GUI.

Open Session.vi Rx niUSRP

a runtime or configuration error.

Code: 1440

Details: RuntimeError: should FPGA number 0 x 6 compatibility, but got 0x9.0:

The build FPGA is not compatible with the host code generation.

As an administrator, run:"C:\Program Files (x86)\UHD\lib\uhd\utils\uhd_images_downloader.py.

I guess I have to perform a firmware update to run the example VI, because he said that it indicates if the utility of Configuration NI USRP. Please also the attached photo. However we do not know what image file to download or burn. In contrast, we find also that the manual suggests not the firmware update for NI USRP 294 x or x 295 if you want to change the behavior of the FPGA?

Do you know how I will deal with him?

Rui

Hello

1. make sure that "Update Needed" message persists even after reboot of the device and and re-enumeration of the device by using the utility of Configuration of NOR-USRP.

2. If the message persists, go to the tab 'Image Updater'.

3 and select the device that you want to update the image on. Once you select the device that the path of the image will be automatically updated. If it does not go through this path of the image: "C:\Program Files (x 86) \National»

4. write the image in the camera.

5 restart the device and re - list and check that the "Update Needed" message no longer exists.

Thank you.

-

Can a single USRP 2920 tansmit (Tx) and receive (Rx) at the same time?

I know a USRP can be a transmitter and a receiver, but a single unit can send and receive at the same time? The application in question involves the sending of an RF signal to a label of RFID and followed by the response of the tag with a single reading USRP. I heard that the link between the channels can cause significant on because bleeding that is not insulation between the tracks, but could not find an example showing simultaneous Tx and Rx. Is there an example or documentation that I'm missing?

Thank you!

Kristen Heck

Academic ESF - middle of Southeast

Hello Kristen,

The USRP can send and receive at the same time. You have because there are bleed more because of the lack of isolation, but documentation of the USRP is always formed and includes no information about this. Here are the 2 screws that allows you to make simultaneous TX/RX. Just to set the IP address in the two screws to the IP address of your USRP and run them. You may need to change the rate of IQ and the frequencies of your application, but this very basic example should be a good starting point.

Let me know if you have any other questions, I'd be happy to help you.

-

I read that we can control the RF switches to the antenna of the road between transmitter and receiver.

I am interested in implementing TDD sytem. Can someone tell how to exploit the functionality of RIO USRP 2952?

Thank you

See SISO TDD OFDM or example frame 802.11.

-

Synchronization of 2 USRP in reception (master and slave)

Hello

When I run "niUSRP EX Rx finished Sync.vi " for the device USRP slave that is connected to the master via the cable MIMO. I put:

-> MIMO frequency reference source

The basic source of time clock-> MIMO

I have the following error ""niUSRP Initiate.vion the PLL reference clock does not lock in the allotted " "Can you help me solve this problem?

Can you help me to synchronize two USRP in reception: a slave and the other is the master connected with cable MIMO?Thank you

Hello

When I run the master and the slave simultaneousely--> I have no error

I use this configuration:

IPAdressMaster = 192.168.10.2

Frequency-> RefIn reference source

Time base clock Source-> PpsInIPAdress = 192.168.10.3

-> MIMO frequency reference source

The basic source of time clock-> MIMOThank you for the help

-

Compact Daq or Rio measurement signal and datalog

Hello

I'm in a project to create a diagnostic for an offshore wind turbine generator system.

So I have to choose a material acquisition and make the basic operations with the measured signals.

The equipment has to work without being connected to a PC, write the data in the internal memory, and then send it via ethernet.

The CDaq and the controller chassis is cheaper than CRio, but she would work without a PC (with the exception of couse the stand-alone version that is overpriced)? Is it possible to add memory via USB to a CDaq (for datalog)?

Hello

If cDAQ standalone chassis is more than your budget, then cRIO is the right/only way to go. The good thing is that they share the modules C-series real connectivity and conditioning of signals is the same. Youneedtohavesomeformoflocalintelligence/processingpowertoevenperform the taskofwritingdatatoaflashdrive "simple."

This is a technical presentation online that might interest you: measures and monitoring in Offshore Applications

Let me know if you want me to make a connection with your local technician to NEITHER.

-

How to synchronize multiple devices (294 x) Rio usrp

Hello

I'm trying to receive 4 channels using two devices USRP-294xR (USRP RIO) to synchronously and run the example for the reception of several device program. Often, I receive the error message "failed synchronization. If I run the example several times in a row, this error message occurs more often than otherwise, but for all the times that he does not, I am able to collect data that seems like synchronous through the channels of reception. So, in a way that works for me, but with the annoying feature that I need to run the program several times now until I am able to avoid the "Synchronization failed" error

My installation includes an Octoclock connected to the Ref connections in and PPS in the two USRPs. In the example, VI, I selected Ref in, but it is clear to me what choice should I use for relaxation. Possible options are: 'Software', 'Immédiate', "Digital Edge", "Rx Start Trigger" and "Tx Start Trigger. I had assumed my previous experience using these devices with the FPGA Ettus I would choose an option indicating that I tried to synchronize the external signal of PPS. "External PPS" is not among the options of trigger, I'm confused as to how the synchronization.

I saw the article below, but it's not not clear for me if I should be able to achieve my goal without making changes FPGA. It is possible to synchronize multiple devices using the program by default FPGA and example (i.e., for example RIO, not the host screw using the Ettus FPGA image)? If so, any suggestions to help me avoid this error "synchronization failed"?

http://zone.NI.com/reference/en-XX/help/373380D-01/usrphelp/synchronization/

Thank you.

Rob

rkossler1 wrote:

Since we did not have a 6674 t, I thought I might as well try to connect PPS from a RIO USRP to PPS on the two RIOs USRP. I just used a BNC - T to "distribute" the relaxation. It did not work - maybe for the same reason you mentioned on the PPS USRP out is not strong enough for the Octoclock by car.

Yep, that's exactly it. The USRP RIO is not output enough power on the PPS TRIG OUT line to drive the lines of PPS TRIG IN two USRP RIOs, unfortunately

rkossler1 wrote:

How can I know which USRP RIO is the 'master '? Do I need to designate in the software? I chose arbitrarily use the device for which I have connected the PPS on the BNC - t 'RIO0', but I don't know how the SW knows what USRP I chose to connect the power cord to.

The USRP captain's exit a PPS TRIG OUT in PPS TRIG IN sound. then all the USRPs you set this unit as the * first * device in the table of features of RIO for the façade of synchronization with a cross screw.

-

Hello!

I'm in the quest to replace some aging PCI-5640R. I am currently using as a portable-Journal data solution, mounted in a Magma Expresscard to PCI box with a laptop. As a reference of the time, I use a Symmetricom XLi.

The equipment is dependent on the sampling finished a set of samples once a trigger signal goes high and also receive antenna azimuth information using two lines PFI more. The signal is sampled at IF, 30 MHz, and the signal is less than 5 MHz bandwidth.

Now, I started watching the Ettus X 301 with a GPS OCXO and MXI-express interface which should be the same as the USRP-295xR NI. It is available as device NI RIO with three different front ends, unfortunately, none of them work at 30 MHz.

Q-1: Ettus has the front-end 'BasicRX', but it is only considered compatible with LabVIEW driver and not necessarily with the RIO. Is the front-end BasicRX usable with the USRP - 295XR RIO and MXI-interface with LabVIEW FPGA? Should I just avoid trying tune the nonexistent LO? As long as he gives me data, I can live with some error messages during the Setup...

It's the best solution for me, but if it is absolutely impossible, I have a few questions:

Q-2: information on the front end are really rare in the pages Web OR both Ettus, but the WBX is listed up to 50 MHz frequency, to have a filter of low pass of bandwidth of 40 MHz to I and Q. This should mean a total of 80 MHz of bandwidth with I and combined Q,-40 to 40 MHz. Why did the bandwidth to Web pages as OR listed being "40 MHz bandwidth in real time", if the low pass filter of the WBX is 40 MHz in I and Q? Not the band total bandwidth or 80 MHz?

Q-3: assuming a bandwidth-40 to 40 MHz: could I put the WBX LO at 50 MHz, be tuned to the frequencies from 30 MHz to 20 MHz signal,-20 MHz and use a bandpass filter to the FPGA to extract the new signals and remove all other signals?

Q 4: I tried to start a FPGA project in LabVIEW and add the x 301/294xR/295xR as a target. Data clock is locked to 120 MHz, which I guess means he will receive no data to 120MS/s IQ? The x 301 Ettus is listed as provide data of the ADC to the FPGA at a rate of 200 ms/s, could someone explain to me why, OR USRP RIO expects only database 120MS/s?

Hi Idar,

Yes, you should be able to put the basics on your X 310/USRP RIO and use LabVIEW FPGA to receive 120 MECH. / s of the DACs. The example I posted is in fact not for the precompiled file bit. The example I posted is for LabVIEW FPGA, which allows you to add the IP address for the FPGA. There is a sample project that comes with LabVIEW FPGA which is the recommended starting point to build your FPGA application. The sample project has all the configuration set up as well as broadcast continuously and pads/FIFOs in the FPGA and examples for synchronization. There are comments in the code example that show where he must add your own blocks of property intellectual as a filter and decimater you mentioned. The PDF I posted shows what changes you must make to this sample project using the Remora Basic/LF.

I would like to know if I'm not explaining this clearly, or if you have any questions, I'd be happy to help you!

-

SISO TDD OFDM Streaming Video on NEITHER RIO or FlexRIO USRP

Hello!

How has the Full Duplex was assured in USRP RIO?

In accordance with the document of this example, the simultaneous transmission of receiver chain is possible at the same frequency. If I take this right has component the interference of the transmitter Tx1 and RX1 was completely canceled for transposition Full Duplex.

Or the FD is possible for an arrangement of the antenna?

Thank you

Understood that here Full Duplex doesn't mean full-duplex, we speak in reception and simultaneous transmission of documents i.e. contemporaries. Here, it's a TDD system, where two data sources can be listened in conjunction, rising and falling, for example as in the No. loopback condition. Simultaneous, albeit two multiplexes in time, flow: downlink uplink (base station user) (base station for the user).

-

USRP RuntimeError: Please update the firmware and FPGA images for your device.

Hello

I have an Ettus USRP N210 with a surfboard RF WBX running FPGA firmware version 4.

2009 LabVIEW and NOR-USRP 1.1

When I try to run one of the USRP VI OR as devices to find it displays the following error code:-1074118627

"niUSRP Devices.vi find

a length or configuration error has occurred."

Code: 1440

Details: RuntimeError:

Please update the firmware and FPGA images for your device.

See application for USRP2/N-Series notes for instructions.

Compatibility of the Protocol expected number [7-11], but received 12:

The version of the firmware is not compatible with the host code generation. »I can communicate with unity on Linux using UHD machine and the utility Configuration NI USRP can see the device, but firmware update is not possible, probably because of my IP ending in 221. Latest firmware Ettus was recharged via Linux UHD.

Looks like my firmware again? I am not allowed to download the old versions of the FPGA firmware.

Can someone help me with this problem please?

With respect,

-Sigurd has.

Hello Sigurd,

The NOR-USRP driver requires a specific firmware and FPGA image to be downloaded to the USRP to exploit.

You can use the utility of Configuration USRP download appropriate firmware and FPGA image to the usrp.

This knowledge base article will help you: how update the Firmware and FPGAS Images for N2xx and NI 292 x USRP

-

LV 1.1, 14.5.1, 2950R USRP, DSP overflow using the example of Streaming Single-Device

Hello.

I use the SDR LabVIEW 1.1 and the USRP 14.5.1 with USRP-2950 device driver. Recently, I tried to use the interface of RX-host of the 'USRP RIO 40 MHz BW Single - Device Streaming PC' - example. Although the USRP device is connected to the PC via the MXIe card I get an error of overflow DSP (continuous mode). In my view must avoid an overflow of DSP for the chosen bandwidth and sample rate (examples in screenshot).

If someone else gets this error or do I have to contact support OR? I already crushed the FPGA Image with the "NOR-SURP Configuration Utility.

Thanks and greetings

-

There is no help for the usrp blocks screens

For power, where are the docs for help for the USRP & USRP related blocks (host side & lvfpga blocks)? Help is dimmed in the menus. If they came with the driver, they should be grouped in with something not obvious & has not installed. Where are they?

BTW, I use NU-USRP 15.00.

Thank you.

apchar,

Try to use context-sensitive help on the pilot of the USRP RIO screw Either click on the "?" in the upper right corner of the block diagram, or press Ctrl-H and hover over the screws of RIO USRP. You should see the additional help documentation.

-

Use the same node of IO in sbRIO (VxWorks) 9606 and 9607 (Linux)

Hello!

I have one tries to use the same FPGA VI on both a sbRIO 9612, 9605, 9606 and 9607. For the three first it is perfectly feasible as soon as I call the IOs even name to different boards. For the 9607 I can't make it work.

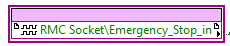

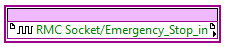

A knot of IO on 9607 looks like:

And I can't the closest to a 9606 is:

Because I'm not allowed to name it with backslash.

And it does not work on both targets.

Is there any other way to the insertion of a structure conditional disable for each node of e/s I use?

Thank you

Anders

Hi Anders,

I noticed in your example, you created a CLIP in the interface with your e/s under the 9607. Did you plan using VIDEO-specific features? If not, you can simply add an EGGA as in the 9606 (target FPGA 9607 right-click > New > RIO Mezzanine Card) and the e/s should look like. This can give you more parity between the targets. Otherwise, I think that the two interfaces will have different properties. I modified your sample project and attached. Take a look at "IO2.vi" and let us know if that's what you're looking for.

Maybe you are looking for

-

As part of my struggle to get rid of all the spam, I've implemented a rule before apple-mail some contacts known to my G-mail. For the mail itself it works well, but attachments are not included. What can I do?

-

need technical help how do I get it?

the program continues by cutting University anad is baffled

-

I can't get my psc1210 to work on my new laptop running windows 7.

I can't get my psc1210 to work on my new laptop running windows 7. I followed all the advice on the HP support pages, but nothing helped. some of the things I've tried: (a) followed by editing according to the http://support.hp.com/us-en/document/c0

-

Used to be when you bought the new computer you got the CD. And as boring he could reload the entire computer from 95 upwards, at least you can operate. Then when I bought this XP rights came with it, sticker on the back, but no CD for safety. They

-

Backup of Assistant - Placement of files on external hard drive (WD Passport)

I've recently backed up all my photos, videos and music files on an external hard drive (WD Passport) using the Microsoft Backup Wizard. In the past I had used WD Sync or Dmailer Sync, but I wasn't able to find my files anywhere, don't know why. If