Digital output on two fronts and internal clock edge

Hola,

I use a PCIe-6537 and LabView 8.6 unit. This unit has an internal clock up to 50 MHz. I am trying to output a digital square wave at the maximum rate of 50 MHz I put my 50 MHz clock frequency, build my table of 1 and 0, convert it and the digital waveforms (on port0/$line0 if it makes a difference) output. During playback of the wave on a scope it shows a [very] good, but only 25 MHz square wave. The reason for which I believe is being only a sample of output (1 or 0) DAQ card for each rising edge of the clock and not fall. This is why the output wave will always be twice as slow as the clock frequency. Is there a way to power on the edge both amounts and descendants of the sample clock so that I can get a square of 50 MHz, wave or should I try a different technique?

I'm all ears...

~ JS

ISO

The ability to generate/acquire both the rising and falling clock edge is called double rate (DDR). We have an application on the use of DDR note with our instruments.

Of the advanced features of digital devices: Double data rate

The Board you use, however, is not capable of a double speed. The only devices capable of DDR at the moment are the NI 6561 and NI 6562, which were maps LVDS. You can get out on the forehead or the edge down, not both. You can use an external circuit to generate a signal of 50 Mbps. Basically, would need you an XOR gate and combine two different ways to create a signal 50 Mbit/s on a 50 MHz clock frequency.

Here is an example of how you can achieve. The white paper I mentioned above will guide you in this process.

On the other hand, we have boards of 100 MHz that will give you a square of 50 MHz, similar to the desired wave. The NI 6542, 6552, 6544 and 6545 are all 100 MHz or higher. The SMU-6545 is a 200 MHz Board. You can use one of these tips to generate higher frequency signals.

Hope that helps. I would like to know your opinion on this.

Tags: NI Hardware

Similar Questions

-

digital output: relationship between input and output values

Hi, could someone tell me if you are using digital lines material OR daqmx (SMU 6358, if it is dependent on the device), what is the value of weight of the inputs that will change the output of 0s to 1s?

Suppose, I write a table of 10 numbers from 0 to 9, which will output look the same?

Thank you.

This is of specific devices, but you will see a pattern the same values across many devices. Of the datasheet for your SMU:

- Continuous positive threshold: 2.2V

- Line negative: 0.8V

Yes 0 - 9V, depends on which direction you're going. It is a grey between 0.8V and 2.2V area because the value will not switch until it reaches the threshold value.

From False to True, you need read a value of 2, 2V. Changes from true to False, you will need to read a value less than 0.8V

This image does a good job of this representative. See the red line (positive course) and green-(négatif cours).

Your title says "Exit" and with the intervention. The above information concerning the digital inputs. The 0V or 5V output feature.

-

Hallo,

I use the following system:

- OR PXI-1044 with controller NI PXI-8109

- OR PXI-2564 switch module to turn on the monitor of my test device

- Data acquisition multifunction NI PXI-6259 to measure the signal that responded to the questionnaire jump

The two cards are the same - PXI trigger bus. For both, PXI-2564 and PXI-6259 I use DAQmx to set the reading and writing of the channels.

Now, I want to measure the time between the digital output, my unit turns and the analog input, which measures the response of my system.

I can't do work by myself, please help me!

I thank Ludwig.

Hi Ludwig,.

If you can't give us any VI we have difficulties with to help you.

Because I Donat knowledge how your program is mounted it is not easy to know where you should enter signals.

Here's a question similar to yours:

http://forums.NI.com/T5/LabVIEW/best-way-to-measure-time/TD-p/178704

and 2 external links:

http://www.ehow.com/how_8698983_measure-time-LabVIEW.html

http://objectmix.com/LabVIEW/385152-how-can-i-use-LabVIEW-measure-time-between-analog-pulses.html

-

How can I more easily generate a pulse of digital output of finite length?

Hello

I need to open and close the two pneumatic valves using a TTL output (without load current or the output power) using a PCI-6280 or PCI-6601. The valves must open almost simultaneously and closing after different amounts of time elapsed (millisecond level timing, maybe 100 microseconds-level timing at worst). My current plan is as follows:

-Create a task with two digital outputs (type of waveform) and another task with a counter that generates a frequency set by the user (I know I can use the generator frequencies on one of these cards, but I would have preferred a counter - the best selection of frequencies).

-Wire the output of the counter at the entrance to clock two digital outputs.

-Output of the meter is digitally triggered by another digital channel which I use to control if the pulse goes out. Through its counter node, it is programmed to be redeclenchables.

-Two digital waveforms are drafted who have both consist of unique active high pulse (i.e. signals go ' down (for the amount of time user-defined) - low ".")

-These signals is written to their respective ports and their tasks have started, as is the task of the meter.

-Whenever the user wants to open taps, digital triggering is sent up and then back to low (this can be done with synchronization software, because it is not exactly when the fire valves). Whenever the user wants the valves open for a different period, different digital waveforms are generated and written in the buffers of the digital output channels.

My problem is that it looks like a lot of effort for me to go and I wonder if there is a much simpler solution, that I don't know everything. You can program a computer to produce a pulse of finite length? Is there a faster way to program a digital output for that channel?

Thanks to anyone who responds to their help.

It is certainly instructive. Thank you.

The thing is, I have only six total counters to work with and I have a lot of time to do things. To use these solutions, I would need to use 4 or 6 account counters required to my needs.also that I would need to synchronize their departures.

Overall, I stick to my method for now - less system resources and synchronization can be don by using the same meter of finished output clock and not to use a trigger to all.

Once again, thank you for your help so far.

-

take the digital output USB-6001 always high or low in c

Hi all

I am new to the NI DAQ interface. I have a USB-6001 and I am trying to use this device to control some flowchart in C. What I want to do is:

* set digital output lines with high and low intensity and change their status as needed (in C).

I tested the device NEITHER Max--> Test panels and found that the device is capable to do that. Then I try to do in C. I have checked hace examples and function I use is one called "DAQmxWriteDigitalU32". I have problem in the understanding of its input parameters. I tried something with my own knowledge, but it does not work as I expected. Here is a test I did:

data uInt32 = 1;

Int32 wrote;

TaskHandle taskHandle = 0;

DAQmxErrChk (DAQmxCreateTask("",&taskHandle));

DAQmxErrChk (DAQmxCreateDOChan (taskHandle, "Dev1/port0/line7", "", DAQmx_Val_ChanForAllLines));

DAQmxErrChk (DAQmxStartTask (taskHandle));

DAQmxErrChk (DAQmxWriteDigitalU32(taskHandle,1,1,10.0,DAQmx_Val_GroupByChannel,&data,&written,));taskHandle = 0;

DAQmxErrChk (DAQmxCreateTask("",&taskHandle));

DAQmxErrChk (DAQmxCreateDOChan (taskHandle, "Dev1/port0/$line0", "", DAQmx_Val_ChanForAllLines));

DAQmxErrChk (DAQmxStartTask (taskHandle));

DAQmxErrChk (DAQmxWriteDigitalU32(taskHandle,1,1,10.0,DAQmx_Val_GroupByChannel,&data,&written,));I just want to set ' Dev1/port0/line7' and ' Dev1/port0/$line0"at a high level, but only ' Dev1/port0/$line0' answer me. The second parameter of the DAQmxWriteDigitalU32 function is numSampsPerChan. If I replace (currently 1) with a higher value, such as 100, I see that "Dev1/port0/line7" sends a number of 1 output, then back to 0. So I guess that the problem is just that I understand not all parameters for the DAQmxWriteDigitalU32 function. Is someone can you please tell me how I can set up a line of digital output 1 or 0?

Thank you!

Hongkun

Hello

I finally find a way to do it! The feature works very well, and my problem was not set the data value to write correctly. It seems that if I want to write a 1 to the port0/line1, I put "data = 2 ^ 1" rather than "data = 1", because by default it is the second bit of the port.» Similarly, "data = 2 ^ 7 ' high level to port0/line7. I find that this setting is surprising when you want to control an individual line. It seems more reasonable when you control the whole port. In any case, is to solve the problem!

Thanks anyway!

Hongkun

-

Synchronization of analog and digital output with the external sample clock

Hello

First of all sorry for my English, I will try to explain what I want to do.

I want my PCIe-6321 to send two custom signals (modification sawtooths) on a mirror controller. I would also like to generate output with my card at the beginning of each tooth of saw. Everything must be synchronized with an external k-clock signal of 100 kHz. The idea is that whenever the PCI receives a trigger to external clock, it sends two analog output voltages and when he received 1024 clock ticks it will also send a pic of triggering TTL. What I do is first prepare the map and after that in a loop sending and modifing the output values of the two signals and at the same time send a digital signal Boolean in each arch, so when's done it 1024 iterations of the loop I send an event to the digital port. Attached you can see.

The problem is that I don't know how to synchronize both. Can I use the sample clock just to the analog output? I can use sample for the two outputs clock, or do I need to use the output of the meter? If don't know how to use it here.

If I do nothing else bad/wrong, I would be grateful for feedback.

Thanks in advance,

PabloI don't know how but I find the solution. I'm generating more than a positive value (as I was triggered maybe very fast the oscilloscope has been absent there). If I put the sample clock of digital output to use the sampling/ao/Dev1 clock that it doesn't, but if I put to use the same source as the OD (terminal where my external clock is connected), but the trigger to start the DO to be Dev1/ao/StartTrigger this works. I don't really know why, but it does.

Thank you for your patience and your help. I put here the final code.

-

Fortunately the cRIO merger two time real screws: analog and digital output

Howdy,

I need help with a cRIO code. The purpose of the code is to acquire an analog input from the NI 9234 c series module and be able to send a "signal of pulse" digital camera (first low for some time, t1, then high for some time, t2) from a NI9401. Separately, I wrote the code to perform both tasks. However, when I add the code of RT digital output pulse pulses to analog input RT code, the DMA FIFO overflows because of the way that my digital pulse output code works. Currently, there are two reasons which overflows of the FIFO:

- The digital output code is pending for a while loop (pending "Send Pulse" become a true), the loop I can't empty the buffer FIFO

- The FIFO is not enough, quickly emptied depending on how long the pulse (t1 and t2) times are. The way I keep the pin high or low for a defined period of time is by issuing a sleep command, which blocks the loop I empty the FIFO. (Is there a "best" way to sleep?)

I have attached photos of my codes FPGA and RT. Please give me a suggestion on how to marry my two loops of RT for the use of happy resources! Thank you.

I found a quick way to solve this problem. I moved the timing of the Digital pulse on the FPGA. So whenever I have a Boolean value, the FPGA generates a waveform with the settings I put (a pulse in my case). This works because the FPGA loops run in parallel, I think. That's why, when I run a pending order in the loop of FPGA digital output, it does not prevent the FPGA of analog input loop to run. I have attached a picture of the code.

-

How to generate the digital output of the variable duty cycle and clock source being contrary?

I want to generate a digital pulse every front amount of my pulse counters. He must have a variable duty cycle. until now, I've been able to generate a digital output, but I can't change its duty cycle.

pls tell how I should proceed?

Thank you in advance...

-

separation of two edges using a digital output

I am using a DAQ, PXI-6229 map and programming in c# .net.

I'm claiming a falling edge on PFI12 used as a digital output, and I need to measure the time between this edge and a second front on PFI8 used as a digital input. I have implemented the code using some examples I found. I don't know when to to argue the signal on PFI12 in order to be read at the right time. Playback must be put in place before the signal is asserted, but I do not know how to set it up it up properly.

Here is the code I have so far:

Public Sub MeasureAcquisitionTime()

{

DigitalSingleInputTask = new Task();

CIChannel counterSetup;

firstEdge = CITwoEdgeSeparationFirstEdge.Falling;

secondEdge = CITwoEdgeSeparationSecondEdge.Rising;

Double minTime = 10-3;

Double maxTime = 60F-3;

String auxCounterInput = "/" + CardName + ' / PFI12 ';

String gateCounterInput = "/" + CardName + ' / PFI8 ';

counterSetup = DigitalSingleInputTask.CIChannels.CreateTwoEdgeSeparationChannel)

CardName + ' / ctr1 ', 'counter',

minTime,

maxTime,

firstEdge, secondEdge, CITwoEdgeSeparationUnits.Seconds);

counterSetup.TwoEdgeSeparationFirstTerminal = auxCounterInput;

counterSetup.TwoEdgeSeparationSecondTerminal = gateCounterInput;

DigitalSingleInputTask.Control (TaskAction.Verify);

runningDigitalTask = DigitalSingleInputTask;

counterInReader = new CounterReader (DigitalSingleInputTask.Stream);

Double data = counterInReader.ReadSingleSampleDouble ();

}I'm glad to hear it.

paofthree wrote:

Is there a way to make a measure of separation of two edges on the analog inputs of the PXI-6229?

The only way would be to constantly acquire the analog input voltage and calculate the separation of the two edges in the software.

Best regards

-

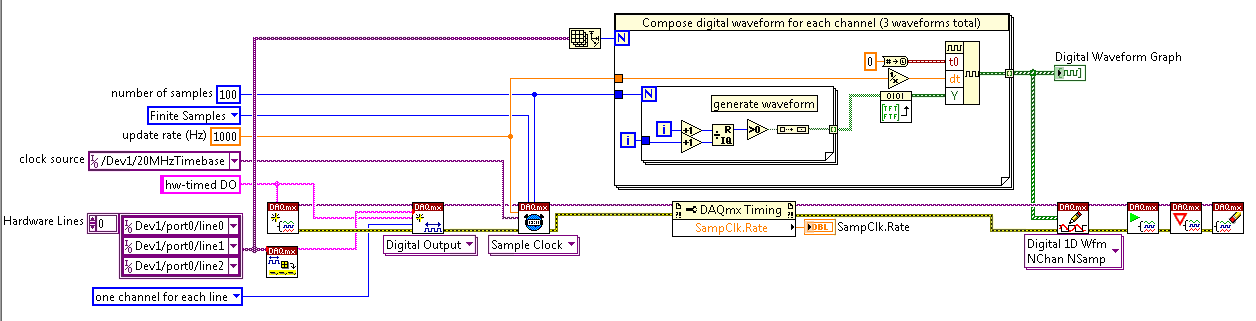

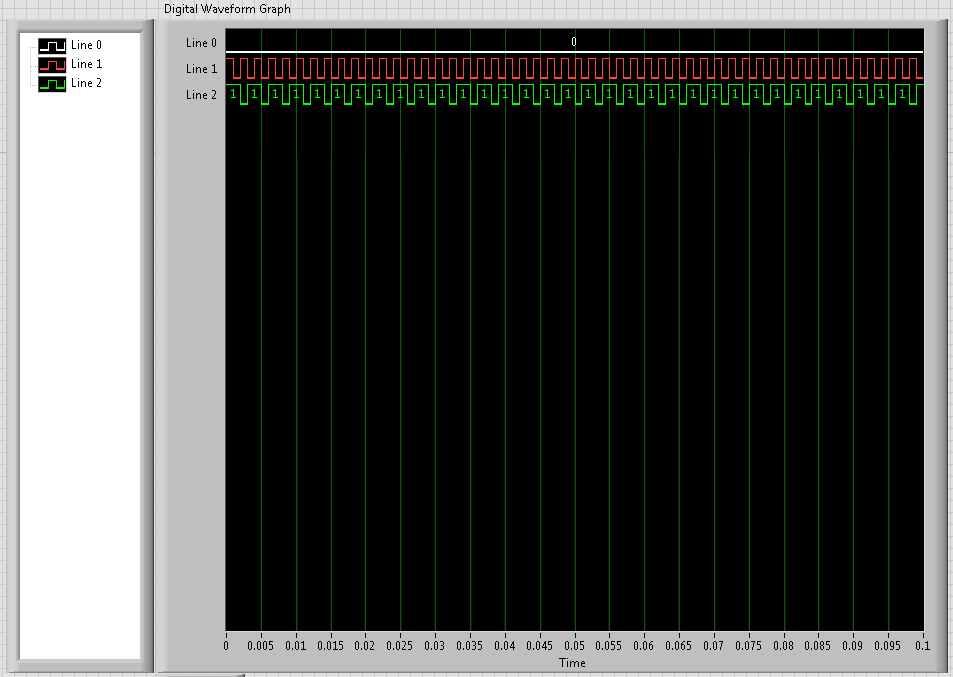

clock calendar - digital output

Hi all!

I need timing equipment impliment on a few digital output lines. That's what I have so far:

I didn't get an oscilloscope for her yet, but I'm fairly certain that it works. Please note that in this example, I use a PCI-6115. I have 2 questions:

(1) make what I do look reasonable at a quick glance?

(2) I'm kinda mistified by the entry of clock source to the example of the clock function. The analysis that I read just still confuses me. I understand that the clock is what dictates the sequence of material. I do not understand how to choose the appropriate clock source correctly. More specifically, in the above example, I've only had the program work when I chose "20MHzTimebase". What is c? Why this work?

When I try to select ' Dev1 / / SampleClock ", I get the following error:"attempted to perform a route when the source and destination are the same point."

When I try to select "Dev1/PFI0" or "RTSI0/DEV1", I get a timeout error in the wait_until_done.vi--> it does not appear that the waveforms are executed.

That means the PFI and RTSI acronym for, and why they appear as options when you select a source of the clock? Furthermore, why have they not worked as a clock source?

I would be very grateful to anyone who could clear things for me a little. Thank you!

Have you read the http://digital.ni.com/manuals.nsf/websearch/01C075FB9478F94A8625786A007435BA? manual The definition of PF and RTSI are here. They are designed using external clock signals. You have the choice of using the internal clocks of analog output (20 MHz) or external clocks. If you do not connect the RTSI bus or PF what, whether you have no clock so no data will be output. Selection of as source does not work because it is not a source. You provide a source for it.

-

I want to integrate the ANSI C sample program ReadDigPort - ExtClk.c in my own big package.

I want to use the internal clock of the BNC NI USB-6259 (.. 80 kHz 120 kHz).

In the document:

High speed M: Series Multifunction DAQ for USB - 16-bit, up to 1.25 MECH built-in BNC connectivity. / s,.

is written:

Or sample DI source clock: Any PFI, RTSI, HAVE sample or convert clock, AO, Ctr n out internal and many other signals sample clock

The digital subsystem doesn't have its own dedicated internal synchronization engine. Therefore, a sample clock must be provided another subsystem on the device or from an external source.How can I use internal clock case OR USB - 6259 BNC for the acquisition of digital data in my own big software?

With what other subsystem on the device can generate a source of the clock? How?It is possible to set a clock on an internal counter (for example ' Dev1/ctr0"):

Creates channels to generate digital impulses that define the freq and dutyCycle and adds the channel of the task that you specify with taskHandle.

DAQmxCreateCOPulseChanFreq (taskHandle, "Dev1/ctr0" units, clockName, idleState,

initialDelay, freq, the duty cycle); worksBut it is not possible to drive this internal clock to a terminal (for example "/ PFI0/Dev1"):

DAQmxErrChk (DAQmxCreateCOPulseChanFreq (taskHandle, "/ PFI0/Dev1", clockName, units, idleState, '))

initialDelay, freq, the duty cycle); does not work: error DAQmx: measurements: type I/O of the physical channel does not match the type of I/O required for the virtual channel you create. Name of the physical channel: PFI0. Name of the virtual channel: clockThe sample clock source can be derived from an external terminal (for example "/ PFI0/Dev1"):

Sets the source of the sample clock, the sample clock rate and the number of samples to acquire or generate.

DAQmxCfgSampClkTiming (taskHandle, "/ PFI0/Dev1", maximumExpectedSamplingRate, DAQmx_Val_Rising, ")

DAQmx_Val_ContSamps, bufferSize); works. Acquire or generate samples until you stop the taskBut it is not possible to derive the internal counter of the clock (for example ' Dev1/ctr0"):

DAQmxCfgSampClkTiming (taskHandle, "Dev1/ctr0", maximumExpectedSamplingRate, DAQmx_Val_Rising,

DAQmx_Val_ContSamps, bufferSize); does not work. Error: Acquire or generate samples until you stop the task: make sure that the name of the terminal is valid for the specified device. See Measurement & Automation explore valid names of terminals. Property: Property of DAQmx_SampClk_Src: DAQmx_SampClk_ActiveEdgeSource device: Terminal Source Dev1: Dev1/ctr0Hi datafriend,

using what it says is correct:

Or sample DI source clock: Any PFI, RTSI, HAVE sample or convert clock, AO, Ctr n out internal and many other signals sample clock

The digital subsystem doesn't have its own dedicated internal synchronization engine. Therefore, a sample clock must be provided another subsystem on the device or from an external source.This means that if you do not use an external signal as clock you can use the sample clock to HAVE it on board or at the output of the internal counter.

There are also 2 ANSI C examples in this regard:

http://zone.NI.com/DevZone/CDA/EPD/p/ID/4485

http://zone.NI.com/DevZone/CDA/EPD/p/ID/4488

So in both cases you have to use a fictitious task you need only for the generation of the internal clock (HAVE or CTR)

-

Control the Boolean commands and generate a corresponding digital output

Hi all

I'm working on a project of activation of the electrode, here, I thought that how could I order an electrode in a time and generate a digital output of it accordingly. I want to replace it with each electrode with a LED on the front panel and generate a numerical value to each LED on the block diagram.

If it can be divided into two parts

1 control the Boolean outputs

Here, my goal is that if I have 5 leds that are used as a Boolean control, must be ordered so that only one of them lights up at the same time and the rest goes off.

I mean for example if #3 was turned on and that the user pressed the #3 #2 should be turned off and only #2 lights.

2. generate the corresponding numerical value

Depending on the position of the LEDs I want to generate a corresponding numerical value, as previously released 3 coming and exit 2 then comes when the second LED illuminates.I ask all participants to this group to help me with this.

Concerning

Why don't you use the radio button control? You can replace the boxes if you want the buttons.

-

CV 1457RT and VBAI: Double digital output

I have a problem with the CVS 1457RT and the VBAI.

I configured two steps with the VBAI for the CVS.

The first step: I've read about the digital input which should trigger my second step.

the second step: I acquire an image (with an ACE of the Basler) and then I measured 8 distances and count 2 edges. After this, I generate a pulse on the digital output once.

After that I did a VI in LabVIEW that measures the time between the IO.

In this VI and on the module which is connected to the digital output, I see that the putput pulses twice but only a few times.

I guess you get noise on your digital input and trigger twice, so that it works the inspection twice, giving you two pulse output.

You can implement a digital filter, where the value that comes out of the filter does not change until entry remained at the same value for the N samples.

Bruce

-

Issue of two-channel digital output

Hello world

I need some aid on two output digital channel design

In short, I want to use a PCI-6731 with BNC2110 output. Two digital output channels will be used, eg Dev1/port0 / line0:1. I hope that $line0 could output a stable finite samples in f1 (for example 10 kHz) frequency and the total number of samples as N1 (e.g. 1E6); in the meantime, I hope that line1 could output samples finished frequency f2 = f1/M (for example 2 kHz) and the number of samples as N2 = N1/M (e.g. 2E5). In other words, I expect $line0 and line1 out same time length samples with different frequencies and different number sequence. Please note that setting should be controllable, and sometimes N2 and f2 are not exactly an integer (then we take round value).

Thank you for your help in advance.

Joined a vi that does what you want, I think. It uses two digital outputs timed by a meter. The digital outputs are fed waveforms generated by two frequencies with a full report. You can change the part of the code that generates the waveform as you wish and use the rest to make the exit.

Richard

-

How to quit smoking all the void s vi before resetting digital outputs and then closing

I have a project that contains a main VI called home screen that calls many different sub vi. I am monitoring for a press of physical button by a digital input with a DAQ Assistant on the main VI and in this case I want my program to abandon all of its VI running and reset all the digital outputs before the closure of Labview. No idea how I would go all this?

I have attatched the basic model of what I do.

Joelspider33 wrote:

The problem is more to do with some of my money that VI running a DAQ Assistant using the same digital lines like the ones I'm wanting to reset and causing it to throw up an error message.

This is why you must set the DIO AFTER all subVIs are arrested. And to do this, you must send messages to these subVIs telling them to stop. If done correctly, it is a very quick process.

Maybe you are looking for

-

install Windows 7 64-bit of the NIDAQmx

I try to install the latest driver NIDAQmx 9.2 on Windows 7 64-bit. The Setup is for multiple OS, including Windows 7 32-bit and 64-bit. When I try to install it, the installation program indicates (x 86) C:/Program Files /... When I try to force C:/

-

Can not play big fish games after installation of Microsoft security essentials

OT: Big Fish Games I just installed the microsoft security essentials and I started to play a game on big fish games but a message came and now I can't play the game can anyone help how can I please allow programs on mse

-

How to read the Landel Messages on a Microsoft XP computor?

Another question: how to read: http://www.att.com/econtactus/SharedSegments/livePerson, jsp? skill = all contactus9 #list And another: (Name removed) with the same information?

-

Get [error number: 0 x 80070424] when you try to install SP3 with Windows Update

I got [error number: 0 x 80070424] when I was trying to do the updates window to install sp3, whatever that means? And how to fix it?

-

HP pavilion p6604f Windows 7 Home Premium and the disk recovery.

Hi, my first time here. First of all, I'm in my late 70s and not very computer. My computer crashed during an update. So in the end I bit the big one and inserted my recovery disc I made 2 years earlier, when I bought the machine. Problem is the re