power of FPGAS on reset

I have a PCI-7833R. The FPGA is programmed so that it would provide two digital high constantly. We had a power outage and the FPGA was forced to power down. When I turn on the power, the FPGA provided is no longer the digital high two. I have the following questions:

-It seems to me that the FPGA VI did not at all after power off. The FPGA should not always run?

-For example, I have a new FPGA, and I run an application with bit, VI and VI FPGA host files. After that, I let the FPGA headlessly tracks. I guess that the FPGA has taken on the personality of the bit file of the application that I ran before. If this is the case, what part of the application he associated the file bit for the FPGA?

-If I don't have in my LabVIEW FPGA module and I get a bit of my colleague file, how can I associate the file bit my FPGA and FPGA works headlessly?

-After what a FPGA is configured with the personality of a bit file, what are all the means to clear that or corrupt that?

-If I have an FPGA that is running headlessly, and I want to do a reset, so that the FPGA runs again from the beginning. Is power cycle an option for this? Are there other options? Can I reset an FPGA without power cycling it?

Thank you!

jyang72211 wrote:

-It seems to me that the FPGA VI did not at all after power off. The FPGA should not always run?

N ° the FPGA loses its configuration when it loses its power and must be recharged again. In most of the FPGA systems (not just NO), this is done by keeping a copy of the configuration in an EEPROM or similar and load at startup. Some FPGA OR cards allow you to download a bitfile to flash memory built-in so that it will be loaded at startup, see downloading an FPGA VI to the Flash of a target FPGA.

jyang72211 wrote:

-For example, I have a new FPGA, and I run an application with bit, VI and VI FPGA host files. After that, I let the FPGA headlessly tracks. I guess that the FPGA has taken on the personality of the bit file of the application that I ran before. If this is the case, what part of the application he associated the file bit for the FPGA?

I don't know what you're asking here. Within your program of LabVIEW you specifically load a bitfile on the FPGA and run. You can also stop the FPGA and load a new bitfile within the same host application - this is useful when you want to perform several tasks without overlapping on the FPGA and there is not enough space to fit all of them in the same design.

jyang72211 wrote:

-If I don't have in my LabVIEW FPGA module and I get a bit of my colleague file, how can I associate the file bit my FPGA and FPGA works headlessly?

See "using LabVIEW FPGA Interface without the FPGA Module". When you do headlessly, you mean with no applications running at once, LabVIEW or something else?

jyang72211 wrote:

-After what a FPGA is configured with the personality of a bit file, what are all the means to clear that or corrupt that?

-If I have an FPGA that is running headlessly, and I want to do a reset, so that the FPGA runs again from the beginning. Is power cycle an option for this? Are there other options? Can I reset an FPGA without power cycling it?

There is LabVIEW FPGA method nodes to abort and reset the FPGA, so you can write a simple LabVIEW application for this. I can't say that's the only way, but it's the only one I know. I don't know of anyway to clear the FPGA without turning off, but the reset method can be close enough.

Tags: NI Software

Similar Questions

-

FPGA FIFO (reset and stop) release

I have a question regarding the release of FIFO. In VI, I use for the collection of data through DMA FIFO, before collecting all loop, I use FPGA reset and after the while loop, I use FIFO.stop. I have attached the picture. However I think it is the last great of data I have collected and wrote in a text file of a single keystroke, appears in the second run, after I stop vi (by Boolean JUDGMENT in vi) and then restart the vi. Seems the data remained in a certain part of the FIFO and has not been emptied by RESET or FIFO. STOP the service. Is there something that I did wrong? Is there some FPGA or the vi setting I know not?

Thank you very much!

OOPS. I solved the problem. It has nothing to do with the FIFO. I need to empty the table at the end of execution so that it cannot be read and written to the file that I use for recording data. Thank you very much anyway.

-

Zero power WRT160N V2 light reset

Reading the FAQ which is flashing power, have pressed reset for 30 seconds, unplugged and plugged in power. I think my only course now is to set up a static IP address and ping exercise.

To do this, I need to set the suggested IP addresses and two DNS servers.

No problem of course with the IP addresses as they are provided in the FAQ.

For the DNS servers that I understand that we can get them on the Web based on the Linksys configuration page.

Unfortunetaly, with the power light flashes, I can't go to this page.

If not, how can I find the DNS numbers?

I am using Windows 7 64 bit and my ISP is Optusnet and my ADSL 2 service.

Help, please.

Dan has soon

Thank you all. The best solution that I think will relate to almost all of the routers Linksys is (perhaps) over the top. It solves the two power light flashes and interrupted or doesn't have a firmware update.

Thanks again for all your help much appreciated.

Dan

-

HP Jet 11: Administrator or power on password recovery/reset (disabled system 82148628)

Trying to help my girlfriend to recover his computer. She must have accidentally put the Admin/power on password and don't remember. I tried a few entries in recovery I found other messages by searching the Web, but none of them have worked.

If the password entry fails three times I get a message "system disabled/82148628".

Any help would be wonderful.

Hello

Come in:

33820208

-

Pavilion dv5 1000s: power of bios and reset admin password

can not access my admin of the bios because I did a really complicated password and now I can't find it anywhere:

After entering password wrong three times, I get this code: 55772809

could you please send me reset code based on the number I have provided above?

Thank you!

Hello

Please try

40650229

Kind regards.

-

100th mini power HP about password resetting

Hello

I have a series of mini 100th hp [edited by Moderator] IS THERE ANY POSIBILITY TO CRACK or PASSBY

NET.

BIOS master password generator.

REO

I must inform you that these services are not endorsed by HP, and that HP is not responsible for any damages that may occur to your system using these services. Please be aware that you do so at your own risk.

-

Keep the power settings for battery reset.

Hello Forum. I have an Ideapad Y570. For the management of energy, there are two settings: better battery life and better health of the battery. Whenever I start the laptop, lenovo energy management becomes automatically the setting better battery life. I want to it must be defined to the better health of the battery to save energy and keep my battery in good health. Help, please!

try to optimize the parameters of battery in safe mode.

-

Dead CMOS

Hello

The threads have been merged since they are both on the same subject.

As most high is not a Windows problem.

Contact the system manufacturer or the manufacturer of the motherboard (for custom systems).

Or refer to a real computer store (the one that makes its own domestic service on this

brand/type of system and not of the leeks and peaks at a Best Buy or other large surfaces

Stores).========================================================

Also you posted again in the comments that are for your comments on the responses

Forum and not for technical questions.For technical questions please post on the Forum of answers corresponding to your version of

Windows, Office, IE or other bodies as required.Answers - Forums

http://answers.Microsoft.com/en-usI hope this helps.

Rob Brown - Microsoft MVP<- profile="" -="" windows="" expert="" -="" consumer="" :="" bicycle=""><- mark="" twain="" said="" it="">

-

reset question and encryption Time capsule

I have reset my Time Capsule with a hard reset (power off and the reset button on TC). I've reset with the same password but do not know if my TC drive is always encrypted with the same password as before the hard reset.

I lost control of my time Capsule when I changed to "DHCP and NAT" bridge mode My TC works in an existing network with an Ethernet connection to the modem router modem/router for the broadband (Comcast) data and a separate wireless network. I was watching my TC and noticed a few unidentified wireless clients. Without thinking carefully, I asked myself why I was in Bridge mode and past my TC bridge DHCP/NAT form. Oops.

I believe me who put in a double NAT situation and I have lost visibility and control my TC - I couldn't see or effect framework with Airport utility, running on a client computer wireless. I tried several things but finally reset the TC and the same password of TC and set mode Bridge (the default value). The backup disks safe when I look into TimeCapsule, I still show want to ensure that they have the same password as before I have not reset or tenant an encryption password.

Reset a Time Capsule will not change the format of the disc. This requires the use of disk utility with the time Capsule disk tab Airport utility. The drive isn't yet sure unless you also reformatted it. It does not read like you did.

If the Capsule worked properly in bridge mode, then be sure to return to this mode if you connect to another, not Apple, router or modem/router. If the Capsule is your only connection to a cable or DSL modem device, you can use normal DHCP.

-

MacBook Pro Late 2011 startup questions - SMC reset necessary after each shut down.

I was asked to look at a friends end 2011 Macbook Pro.

Initially, it seemed dead. No power, no response. I did the Shift + Command + control + Power to try to reset the SMC nothing helps.

I opened the back and disconnected the battery and the magsafe. I help the power button down for 5 seconds. reconnected the dough tried power on and it didn't work until I plugged the magsafe. Ah ha I thought it, BUT. Once started it works very well, some check everything looks good and battery shows healthy with 70% of load.

I restart the machine and it starts fine. HOWEVER. I stop the machine and I'm back to square one. Power supply photo and battery connected.

So I rinse and repeat. battery disconnect power hold button wait 5 plug in back and then turn it on. As before it works only after the power supply was ALSO connected. to test this situation I tried again without connecting the battery and just the power supply. Since then only the battery was in, nothing until that I plugged the battery ALSO.

So the Macbook will start only after a stop if the battery and power are both removed, button / help for 5 then BOTH the power and battery are reconnected.

I've seen people with similar questions but no one seems the specific symptoms that it requires this reset each STOP but restarts not on the list.

Clues, help, correct?

See you soon

Paul

Hi deep:

Have you tried resetting the NVRAM?

Try reseting NVRAM. How to reset the NVRAM on your Mac - Apple Support

Then try reseting SMC. Reset the management system (SCM) controller on your Mac - Apple Support

Then, try a safe boot. Safe mode try if your Mac does not start-up

Also, see this help file. If your Mac will not turn on - Apple Support

Kim

-

Multiple Ukraine power measurement

Hello

I use the card Ni SMU 4143. I have a VI that propels a certain voltage level card. Now, I'm trying to create a separate VI which will only measure the voltage and current on the power supply without a reset provision. I understand that I must "log on" to the device before I use the "power measurement multiple.vi Ukraine", but whenever I use the session initiate, it will my device and set my level of back tension reset. Can you please explain how I can create a VI that measures only the voltage and current without changing their level?

After the opening, why don't call you the VI that determines the level? Not this separate VI also call the lance function? Think that the flow of data.

-

Download Bitfile to Flash on FPGA in VeriStand

Hello

I was wondering how to download a FPGA bitfile for flash memory on a FPGA using VeriStand. I use a PXI chassis and a FPGA PXI R series.

I hope that the answer is

(1) configure the FPGA VI to run when loading on FPGA

(2) open the VeriStand System Explorer, set the initialization of the system to run a system to reboot definition.

(3) deployment.

Or is the bitfile stored on the hard drive to the chassis and then imported on the FPGA whenever the chassis is started?

If I cancel the deployment of the system definition file I guess the flash on the FPGA is deleted, is it true?

Thank you

Brent

Hi Brent,

I heard R & d today. VeriStand uses the open FPGA VI reference, which means that the bitfile will not be replaced if it detects the correct bitfile already running.

"(Par défaut pour certaines cibles FPGA, cette fonction s'ouvre et exécute le VI FPGA compilé sur la cible FPGA si le VI FPGA n'est pas déjà en cours d'exécution)." - 2012 help FPGA open Reference VI.

When the system definition is canceled the FPGA is reset to zero, which is the default behavior of the close FPGA VI reference.

"Farm the reference to the FPGA VI and resets the VI if no other references to the VI is open. Reset of the VI returns VI orders and States flags by default defines global variables uninitialized shift registers default values and clears FIFOs. "- 2012 Help close FPGA VI Reference.

Zach

-

FPGA code will stop when the code RT

I developed a FPGA code to manage a piece of hardware. It's the installer to read some default Panel control configuration values and then sit there constantly respond to signals input and output signal. The bitfile FPGA is written in flash to load FPGA memory and starts almost immediately. So far, everything is good.

Then I layered on the code of RT (cRIO-9075) system that opens a reference FPGA to the FPGA façade and allows me to follow a few indicators and change configuration settings and cause the configuration settings is changed be used by the FPGA. So far, it seems to work too when I run the RT code interactively (eventually there will be an interface for a host system).

The problem occurs when the code RT is ordered to stop. If you stop the RT code also, the judgment of the FPGA code and I will not stop the FPGA code. The RT code does not all calls to order the FPGA code to stop execution. When the RT code is stopped, the only thing she does in regards the link to the FPGA is to close the reference FPGA VI which was opened when the RT code was started.

What should I do to cause the code FPGA to continue to operate as the RT code is started and stopped?

I have to wait that I return to the office tomorrow to test this, but I think that this link has the answer to my problem.

http://lavag.org/topic/16412-confusion-regarding-FPGA-Deployment/#entry100294

It is said: "close FPGA VI reference. If you right click you have an option to close or by default close and reset. This means the VI FPGA is reset (read aborted in standard LV talking) when we close the reference. »

-

CM1312nfi: Recovery run out of food, Fax Reset Settings & invalid parameter

The machine will not fax. Error message is two lines which are superimposed:

Power failure recovery

Reset fax settings

Did a reset,

Download driver successful

Latest version of the software, full download failure at end with error message on computer - invalid parameter.

Tried cooking of the members of the trainer, no difference.

What's wrong?

Thank you.

Solved. Successfully installed the complete driver in wired Ethernet package. Everything works.

-

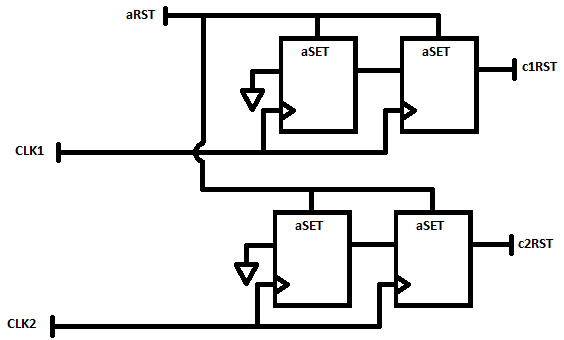

How the resets are generated in LabVIEW for FlexRIO

All,

My background is VHDL and Verilog for FPGA and ASIC implementations. I guess LabVIEW has a point, an only synchronous reset to all of its logic. I create a design that is going to be sections of VHDL IP, through IP integration node is instantiated. When writing to the top of my spec, I need to describe how a reset is spread to all the flops in the design that will be peer-reviewed of accuracy of the results. I need to understand exactly how LabVIEW handles resets to other areas of the clock.

A simple case is the following: I have a 50 MHz external source synchronous data interface and will be a limited treatment of data in this area of 50 MHz using an IP integration node. This IP is designed to have the flops to reset synchronous on the 50 MHz clock.

Separately, I have my most of my treatment and storage to the host (via DMA FIFO) in a field of 100 MHz clock, derived from the clock of 40 MHz I base I must transfer data from 50 MHz to 100 MHz using a FIFO. This treatment at 100 MHz contains a floating-point operations that are reset to zero synchronously to the field of 100 MHz.

In this scenario, you see I have two areas of clock with synchronous resets. I need to understand how LabVIEW FPGA create reset signals which are entries to my integration IP nodes, in order to understand if I need to incorporate any reset synchronization within my VHDL circuits.

Thanks for any help and if you need further details or context, please let me know and I find out additional details.

-Jim

Hey Jim,.

So, option 2 then... in this case, you are looking at a signal of asynchronous reset and must realize in your VHDL similar to the following to ensure that your resets are say synchronously.

Maybe you are looking for

-

Satellite A660 - Touchpad does not

I have a Satellite A660-16Z and touchpad work not at all even if it is enabled with F9.I have to use a mouse external usb. I tried several times to uninstall and reinstall the touchpad driver from toshiba site without success.Initially, after the pur

-

Synchronous triggering of two HP3458A - delay time

Hello I would like to get the time difference between synchronous HP3458A 2 trigger instruments. Estimated time is in nanoseconds or microseconds. Find hatched VI. Set the project includes reseting the two HP3458A, adjust settings, obtaining data, av

-

I recently had a meeting with microsoft and went into safe mode, but now when I boot it opens in safe mode and I don't know how to get back to normal, I powereddown and removed the battery and tried agin selecting normalmode bit still opens in safe m

-

Once I connected my e200 either to upload or download music, I have problems when I log out. I'll click the 'Remove hardware safely' and remove the device, I get a message "disconnected" on the device. But when I physically disconnect the device from

-

Printer LaserJet 4100: Should which cable I for Laserjet 4100 connected to the laptop with USB port

I have the HP Laserjet 4100 printer. I bought a new laptop with USB ports. What type of printer cable I need to connect the printer to my laptop? Is there some kind of printer cable adapter, or something else that will do the trick? I have the same