Behavior PWM PXI R series

Hello

I created a simple PWM using a PXI-7851R and it worked very well for the past month or so but now it behaves strangely. Previously, so I've provided a min and max power, the impulse generated would be between these two values. Now what is happening, is that the momentum generated is always centered above zero with a min and max value equal to half the distance between my input values. So for example if I wanted a 0 - 6V pwm signal, I previously would enter a 0V min and max of 6V, but now that translates a signal from-3 to 3 ' [(6V-0V) / 2]» As you can see in the snippet, everything I do is update the AO channel with the max value, pending, then update with the min value so I can't understand why he behaves in this way. I use a block of SCB-68 connection so I thought maybe the position of the switches I messed up, but they seem to be on the direct crossing. Any ideas why this happens?

-Va

One of AO channels on another block of connection has been hit before, so I thought it's a similar problem, but it was actually only a few error simple user stupid on my part and I forgot to put my field in DC mode  .

.

Tags: NI Software

Similar Questions

-

How to read the analog inputs of one Board of R for (PXI-7851R) series

You can guide me please with the steps for reading of the analog inputs of a series a. card I use as the target fpga PXI-7851R.

Have you looked at the examples provided with LabVIEW? There are examples showing how to read the analog inputs.

-

I can't read thermocouples on the PXI-6225-series M 1 connector.

I'm reading 30 measures by thermocouple in differential mode. I use AI0 as the CCM. Attached are the connections that I use. Negative contributions all relate directly to the GND AI.

I have no problem to read the thermocouples in slot 0 (AI1 by AI 7). I have install Connector 1 direct feed by mode (switch 1 & 2 right and switch 3 upwards). In MAX, I get a normal reading, but it does not vary by heating the thermocouple. In my real program, it is as if there is nothing connected. Any ideas as to what I can hurt?

Thank you

Mark

Mark,

Thanks for posting. I think the question might be to see you about the how the SCB-68 must be configured in mode of direct crossing to be used with the connector 1 on the PXI-6225. When the switches on the block are defined for a direct crossing, the Council is not connected to the CJC. Do not have a connection to a CCM on this connector could cause this problem.

A potential solution, you can try is to connect a temperature probe to AI16 and follow the steps in this KB, using that channel instead of the CJC channel. Let me know if it helps!

Kind regards

Joe S.

-

Number of reading through cvi pxi-4110 series

Hi all

Is it possible to read the serial number pxi-4110 programmatically?

I can see that she displayed in the attributes for the instrument section

Max under NOR-DAQmx devices.I use NI-DCpower 1.2.2 in cvi as a pilot and saw not a way

to do.Any suggestions would be greatly appreciated.

B

Thanks Chris! I tried and it works fine. Best regards, Bill

-

How to generate the clock 8,192 MHz on the labview FPGA 7854R series card?

Hello

I use the NI PXI-7854R series card that has 5 FPGA from Xilinx Vertex on him. I'm drifting clockwork 8,192 MHz to 40 MHz on board the FPGA clock. But he ended up giving me a single clock 8 MHz. is it possible to access the PLL located on FPGA Xilinx?

Concerning

If you are familiar with VHDL you can make your own "component-level IP' (aka CLIP) with a PLL Xilinx inside. There are topics for help and examples of how to define a CLIP. Here's one that shows how instantiate a DCM (similar to a PLL) in a CLIP:

http://zone.NI.com/reference/en-XX/help/371599F-01/lvfpgahelp/fpga_clip_clock_ex_code/

-

I have a PXI - 6040E DIO P0.0 (52 PIN) port is hooked up to a module OPTO - 22 G4ODC5 (TTL Input). When I run DIO Port COnfig.vi with map direction line the value - 1 (all the value entries Digital Out) it lights up all the inputs(PO.0-7). When I turn actually WE DO using DIO Port Write.vi the, it turns OFF. Tried to reverse the line maximum work don't wilt. All entries?

Hello lilocomotiv,

The behavior you describe is the default behavior of the E series. To set the States of digital lines see 266KK6YF knowledge base: affecting the default state of the digital lines on maps DAQ of E series.

-

Download Bitfile to Flash on FPGA in VeriStand

Hello

I was wondering how to download a FPGA bitfile for flash memory on a FPGA using VeriStand. I use a PXI chassis and a FPGA PXI R series.

I hope that the answer is

(1) configure the FPGA VI to run when loading on FPGA

(2) open the VeriStand System Explorer, set the initialization of the system to run a system to reboot definition.

(3) deployment.

Or is the bitfile stored on the hard drive to the chassis and then imported on the FPGA whenever the chassis is started?

If I cancel the deployment of the system definition file I guess the flash on the FPGA is deleted, is it true?

Thank you

Brent

Hi Brent,

I heard R & d today. VeriStand uses the open FPGA VI reference, which means that the bitfile will not be replaced if it detects the correct bitfile already running.

"(Par défaut pour certaines cibles FPGA, cette fonction s'ouvre et exécute le VI FPGA compilé sur la cible FPGA si le VI FPGA n'est pas déjà en cours d'exécution)." - 2012 help FPGA open Reference VI.

When the system definition is canceled the FPGA is reset to zero, which is the default behavior of the close FPGA VI reference.

"Farm the reference to the FPGA VI and resets the VI if no other references to the VI is open. Reset of the VI returns VI orders and States flags by default defines global variables uninitialized shift registers default values and clears FIFOs. "- 2012 Help close FPGA VI Reference.

Zach

-

SCXI and acquisition with Windows 7 x 64

Our just updated IT to update our phones and we have received Windows 7 x 64.

Data acquisition, we use the SCXI hardware in the SCXI-1000DC chassis and an acquisition of data SCXI-1600 USB card. Doing my gear OR set up on the new laptop, I discovered that neither does not support Windows 7 x 64 for the SCXI-1600. The other options to connect the SCXI-1000 chassis to a laptop are the DAQcard-6062E and DAQcard-6036E, nor which supports Windows 7 x 64. According to the information below, there are no plans to support x 64.

What are my options to continue the use of the material, we have invested with the laptop running Windows 7 x 64?

You will need the NI SCXI-1349 connection block and SH68-68-EP cable. The SCXI-1349 plug at the rear of your SCXI module and cable connects the 1349 the USB device series M mass termination. The rest of the configuration is identical to any PCI/PXI E Series device. The USB M Series device will be the analog-to-digital converter for the system instead of the SCXI-1600.

-

Reference with 6215 trigger: error 200452

I am trying to create a trigger for reference to the analog inputs of sample. However, I get the following error:

Error DAQmxBase-200452:

specified property is not supported by the device or is not applicable to the task. And here is the code (which is actually from one of the sample codes)

.

Trip parameters

Char [] triggerSource = ' / PFI0/Dev1;

uInt32 triggerSlope = DAQmx_Val_RisingSlope;

uInt32 triggerSamples = 100;

..

.

DAQmxErrChk (DAQmxBaseCreateTask("",&taskHandle));

DAQmxErrChk (DAQmxBaseCreateAIVoltageChan(taskHandle,chan,"",DAQmx_Val_Cfg_Default,min,max,DAQmx_Val_Volts,));

DAQmxErrChk (DAQmxBaseCfgSampClkTiming (taskHandle, clockSource, sampleRate, DAQmx_Val_Rising, DAQmx_Val_FiniteSamps, samplesPerChan));DAQmxErrChk (DAQmxBaseCfgDigEdgeRefTrig (triggerSource, triggerSlope, taskHandle, triggerSamples));

DAQmxErrChk (DAQmxBaseStartTask (taskHandle));

DAQmxErrChk (DAQmxBaseReadAnalogF64(taskHandle,pointsToRead,timeout,DAQmx_Val_GroupByChannel,data,bufferSize,&pointsRead,));printf ("%d samples\n achievements", pointsRead);

Print only the first 10 points

for (i = 0; i< 10;="">

printf ("data [%d] = %f\n", i, data [i] ");Reference trigger not taken the 6215? I m using the following:

OpenSuse 11.2

MX NI DAQ base 3.4.0

LabVIEW 10.0

I m basically just make use of the C API in my own program and do not use other software to configure the DAQ.

Unfortunately, reference trigger is only supported in DAQmx Base 3.4 for the PCI, PCIe, PXI M Series (see the DAQmx Base 3.4 readme file).

A possible solution would be to sample lines HAVE continuously and implement the reference trigger yourself in the software.

Best regards

-

Hi all

I'm still fairly new to labview and I need your help for a matter of timing:

This is the material that I own:

Chassis _NIPXIe-1073

_NIPXI-6259 DAQ

_NIPXI-6722 DAQ

_NI5751 FPGA with digital module 2147 (analog input) and 2148 (e/s)

The software I use is Labview 2012 64bits.

Now, here's my question:

For now, I use only the Council of NIPXIe-6259DAQ which has inputs and analog outputs.

What I have to do is record an analog signal, a couple of matemathical asks about it and send it to an analog output. I do this in a while loop Labview (attached is my vi).

However the process of acquisition and output signals must be performed in 1 microsedonds.

For the time being with the NIPXIe-6259DAQ card when I try to run this kind of tasks, I can write only 10samples/ms... When I use probes in labview to check how many samples are written.

Don't see an obvious solution to my problem with the material that I own?

If not, should what kind of material I buy for my needs?

Thank you very much

Best regards

For the recovery of the microsecond, I really think you want to go with an FPGA, something in the Councils of PXI R Series should work for you. I do not trust Windows at all to be able to turn around that data in a microsecond, consistantly nevermind.

-

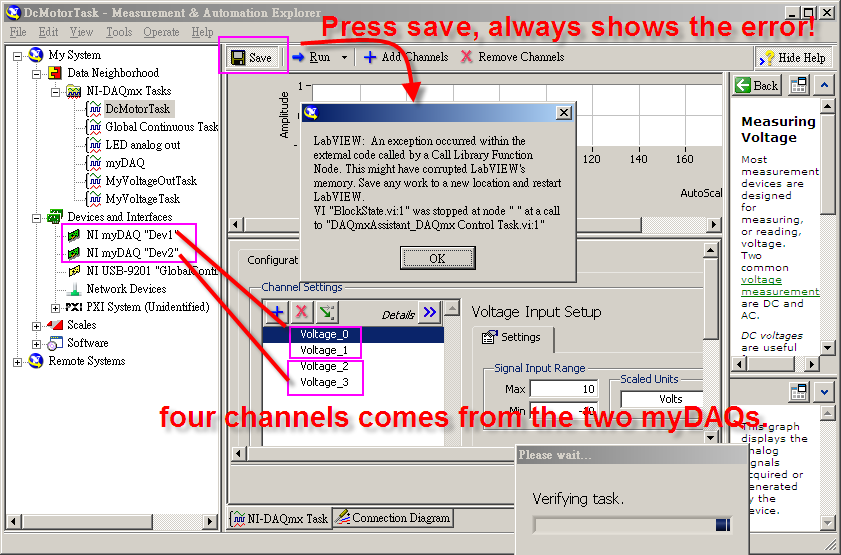

Cannot combine channels HAVE in a four lanes of two myDAQs

Hello

I used the MAX Explorer to add two channels analog input (AI) of myDAQ in a task. It works very well for this.

For now I need application of analog input a four lanes, so I get two myDAQs for this. I add both of two channels of the two myDAQs AI in a task, but still get the message:

An exception occurred within the external code by a call call... VI 'BlockState.vi:2' was arrested in node "" a call to 'DAQmxAssistant_DAQmx control Task.vi:1 '.

Showed as below:

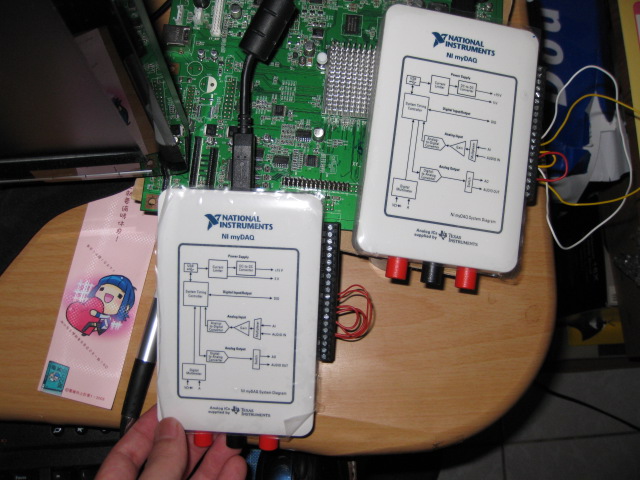

The photo below shows two myDAQ are used simultaneously for an application to HAVE four channels.

Could you please help or give some advice? The situation is fairly easy to reproduce. Just get two myDAQs and add both of its two channels of each myDAQ AI for combine four channels in the tasks of the Explorer MAX.

Thank you!

LKKSPP

This restriction is common to many materials DAQ. Some devices do not support having channels of several devices in the same tasks, but it is still quite rare (DSA and devices in the same chassis. PXI X series) and the modules in the CompactDAQ same chassis come to mind

The main reason for this is that all devices in a single task share the same source of synchronization. Unless you use a CompactDAQ or PXI chassis or using a RTSI cable between PCI devices, it is not a way for multiple devices to share the same source of synchronization. So, each device must be in its own task. This is the case for all devices no USB CompactDAQ, not only myDAQ.

I hope that clarifies what you see.

-

NEITHER SMU 7965R for emulation

Hello

I want to develop applications for RIO Flex NI SMU 7965R in emulation mode as I do not have any hardware connected to my system, but creating FPGA project that I select Create new system whereby only the PXI-795xR series is available. How can I get the objectives of series PXI-796xR for my project?

As after testing in emulation mode I will run this application in the other system where SMU 7965 FPGA board is connected, so that I can directly export the project to the other system otherwise I can export only the VI where I should create new project under which I will add elements of memory needed each time.

Thank you

Chandrasekhar R Polska.

I found the solution to the problem of updating to NI RIO 3.3.1 which can be found using the following link

http://Joule.NI.com/nidu/CDs/view/p/ID/1528/lang/en

Now I can find maps of the series x 796 SMU for emulation.

Thank you.

-

Hello world

I am trying to interface a M833 Monochromator with my pc using labview. My system is actually running

LabView 2010 sp1

MAX 5.0

3.8.1 OR serial

NI-VISA 5.1

on Windows XP.

Open my present instrument Device Manager (this is a plug-and-play device and works well with the softaware factory, so I think the drivers are ok).

Max in devices and Interfaces are listed only:

-Network devices

PXI-

-Series and parallel

What can I do to grab votes usb peripherals and interfaces in Max?

Thank you, uge

Hi uge026,

Since your M833 monochromator is not a material OR and DAQ compatible, it can be registered OR max.

Kind regards

uge026

-

I would like to synchronize the nine 6123 cards (100 kHz analog) with six 6561 cards (LVDS 2 MHz). Correct me if I'm wrong, that the correct technique is to use meters. Use one count 6123 to generate a pulse of 100 kHz'd sync analog acquisition. Then set up a second 6123 meter as continuous trigger (20 - Pulse), trigger some of counter1 counter2, which gives an impulse of 2 MHz clock had analog acquisition. Then set TClk of LVDS to trigger 6123 counter2. Hey presto, all channels are overall sync.

Writing down is easy, but write the code a bit more complicated. If applications engineers or congratulations looking for members of the community have achieved such a feat, send the example code, it would be much appreciated.

Hi all

I just wanted to post the summary:

In order to synchronize, you must share a sample or reference clock. With the HSDIO as the master, you cannot share it except using the ClkOut Smb, impossible to write trigger lines connection in in a way that can receive the S series.

Using the S series as the master, you can easily generate a 2 MHz clock signal using a task of the meter output. This signal must be routed to the HSDIO device. This is only possible with the help of an external connection (ClkIn smb connector or line Strobe), since the card cannot be written in PXI_Trig7 or line STAR PXI S series (HSDIO device can accept signals of sample ClkIn STAR PXI and Strobe clock; it can accept clocks of reference on ClkIn, PXI_CLK10 and Trig7).

See the attached example, I created to do exactly this.

I realize that using external connections may not be the preferred solution. Another idea we had, it is possible to use a build task in conjunction with script on a device HSDIO markers in order to effectively generate the 2 MHz clock that can be shared on a line of PXI_Trig. This can be broken down on the S series to the sample clock cards HAVE.

Kind regards

James Hillman

SR: 721280

-

Aspire ES1-731, startup very slow upward

A new machine, have Mozilla browser... Find much slower start than the series E5 - 571, which is a little more expensive. Problem: there is a startup program that drags the whole process. It takes some minutes. I did the following: categorize any task not important start-up as non-priority; McAfee has a bad habit (such as AVast!) of hard immediately from the HD to 100% occupancy. Disabled scan started upward.

Immediate disabling Scan at startup and even disable AV does not resolve the issue. Looking at the Task Manager, there is a host program that is initiated. What is it? It takes just as long to start with LAN disconnected, so I assume that the procesessor continues with TSR programs.

Even with Hardware acceleration switch makes no difference. Doing the simplest things.

If I bought a laggard with a slower processor; or someone else got sim behaviors? E5-571 series was pretty darn fast.

rich

Thanks for the responses... but I made my way... because the laptop crashed under warranty... I took it to where I bought it; only to be informed within 3 weeks... (Acer products are so rude?) While it was cheaper to clean HD 100% clean, knock out the boot sectors (copies saved before, even if it is on the motherboard) and reinstall windows 10 without attachments of ACER and all other patter and the absurd cortana, the Add-ons that don't work on multilingual machines. It took a full day, but the result is back to basics, a much faster machine; and child's play to use. I can recommend to other budget users, if known best from the sytem complex, to remove all that start programs are not necessary, but beware the Windows 10 programmers have deceived by the bits from other programs such as office for the program Win 10-cleaning function.

Be sure to powerful how forage with Win 10... It's pretty things undebuggable.

Maybe you are looking for

-

I can't install version 1.1.1 in my open ZTE (Movistar).

I read that Version 1.1.1 is available for update. It includes the ability to import contacts from gmail and other email accounts.When I check my version of the OS, it appears 1.0.0 and the message I get is 'Last update'. How can I update? Thanks in

-

HP Pavilion Elite e9280t PC: need a fan spec for HP Pavilion Elite

Hello. I have a copuple HP Pavilion Elite PCs (round box) e9280t I buy several years ago. Now refresh their place with new hard disks. While I am, thought I would replace the old dusty case fans (I understand the fans can go wrong, after many years,

-

Focus between two applications

Hello I work with both applications at the same time, which is made with CVI and the other not (e.i. Explorer). The application made with CVI every 20 seconds displays a new Panel and take focus (hence the other app lose focus), but I would still kee

-

My account has been deleted. Can you please restore it?

E-mail address is removed from the privacy * id has been removed, you can reopen? I tried to connect with evil passward. I changed the password in error and do not know what it was. my account has been deleted. Please restore it. * deletion of pers

-

Hp4630 all-in-one: printer copy

My printer looks like it's the copy but the page comes out blank