cRIO-9104 .vi running on subnets

I have a .vi I'm out of my computer with Labview version 8.2 and a cRIO-9104 running an another .vi plugged into an ethernet switch. My problem is this: when I'm connected to the same switch and am assigned the same IP as my cRIO system, I am able to run the program without any problem. However, when I try to connect to the same cRIO on a different pattern of ownership intellectual my program spits out an error. I can ping successfully and deploy the program on the cRIO across different subnets; It's just when I go to run the program on the computer it throws the error. The error is: code:-1950679022 source: LVVAR_RTSinglePointRead bool.vi. It is the error in the program on the cRIO. Thanks in advance for your help.

After talking to tech support of NOR the solution to this problem is to use sockets of data at the same time with shared variables. This article: http://digital.ni.com/public.nsf/allkb/474BC0745F63B7378625754D0069ECE8 explains how to do this.

Tags: NI Software

Similar Questions

-

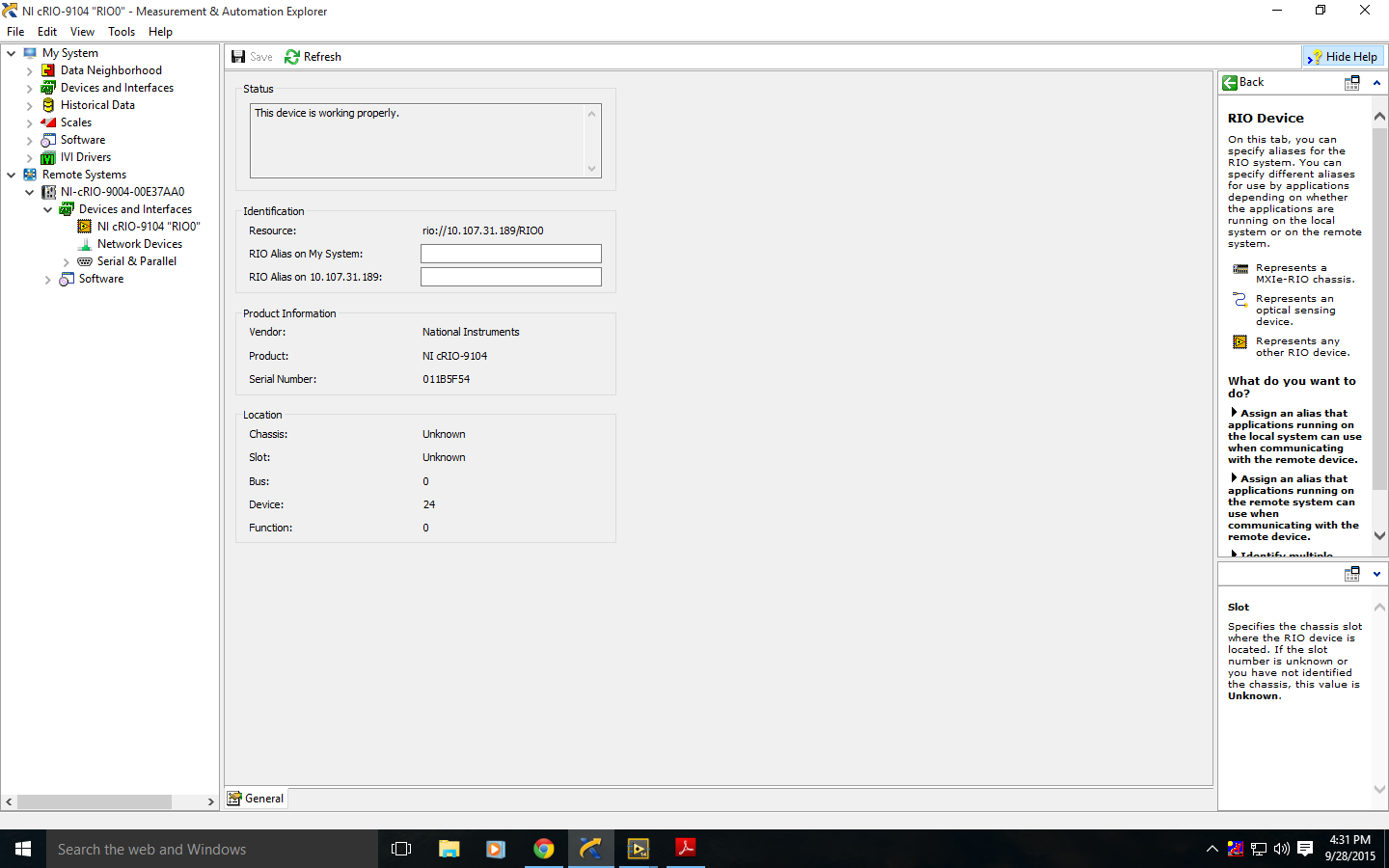

facing problem in communicating with chassis cRIO-9104 NI Max

I tried to communicaste with my cRIO-9004 using the ethernet cable that is connected to the same subnet as the PC master. It is mounted on the cRIO-9104 chassis that has a reconfiurable FPGA and 8 slots.

But I could not find cRIO-9004 in the specified window NOR MAX chassis as unknown.

I am new user of this module and the software. Help, please

Hey, Vinayak,.

I'm not sure that there is a problem here. Usually, you'd do anything with Max modules are you able to add them to your project in LabVIEW?

-

Compliling VI in LabVIEW with cRIO-9004 controller and chassis cRIO-9104

I tried to compile in LabVIEW with cRIO 9004 and cRIo-9104 connected.

It has three options

(1) use the server local compilation.

(2) to connect to the network compile Server

(3) to connect to the service of LabVIEW FPGA cloud compile

But I'm unable to compile my program using one of these.

How can I get my compilation made? Help, please.

Thanks YouCp

Service provider shared's Standard Service program is an annual fee of NOR, which in turn allow you to update your modules and LabVIEW and benefiting from the support of NEITHER.

-

Hello world

I am beginner in LabVIEW and LabVIEW FPGA and RT. student internship that I work this month on FPGA project and my goal is to schedule a stand-alone on cRIO application.

I got a CompactRIO 9002 with an AIO 9215 analog input module and use LabVIEW 13. This cRIO Gets an ethernet and a RS323 port.

My request is to:-code FPGA by ethernet

-acquire a signal input of the NI 9215 module

-Send the data measured on a device (first on hyperterminal on PC and on an SD card or a storage device) by the port COM (RS232)

My development was to: 1. create a new FPGA project

2 code for the target FPGA vi and compile (InOut.vi)

3 code another vi to run the cRIO from my computer (OpenCloseFPGA)

At this stage, everything goes well and works and I followed the signal measured on OpenCloseFPGA.vi and my Pc Hyperterminal.

Can I track this topic 'http://zone.ni.com/reference/en-XX/help/370622L-01/lvrthowto/rt_building_rt_app/' on the creation and deployment of a stand-alone application in real time. But my RT generated and deployed application nothing happens. I followed other tutorials on standalone RT but I still stuck...

Could someone give me any tips or tutorials to help me?

I found the solution, there is a mismatch and a mistake in my project.

First, I use a cRIO 9002 and in building'step to unplugging it SSE2 option in "Advanced dialog box.

The second was a mistake from myself, I give an ethernet address to RT host that cannot run in a standalone application (wireless).

Thank you for all your help.

-

You try to run the scan mode and mode interface fpga at the same time is causing errors

I'm reading a 9236 9237 and a 9215 with the scanning engine and read from two 9211 modules with the fpga. It's because I need to acquire to 200 Hz with the 9236 9237 9215 but maximum rate of the scan engine is limited by the slower module in the system, which in this case is the max of 15 hz the 9211.

So to use both interfaces (scan engine and fpga), I followed the percisely given in this article for instructions.

1. the project has created and added the peripheral crio using the interface of the scan engine.

2. Add the target fpga and drag and drop the 9211 inside modules

3. has created the fpga in interface file with and compiled with no error.

4. interfaced with the file fpga at almost exactly the way the sample project of "getting started with 9211' by using the engine of analysis in the interface with the other modules.

5. after the errors to discover that I created a VI that tests for just the portion 9211 code (called "thermocouple FPGA method Test.vi")

The data returned by the interface fpga was nothing else than zeros on all channels, even if thermocouples were hooked on some of them. (all zeros as entries in the convert temperature vi gives-410, 6160 degrees F, if you happen to have the material to try this.)

I get the following error from the open fpga vi reference:

code error-61141

"Thermocouple method Test.vi FPGA.

Activities FPGA:Open FPGA interface reference.

Reserved outside LabVIEW FPGA: turns The RIO Scan Interface. You must set the mode Interface FPGA chassis in order to unlock the FPGA. »It's extremely frustrating, because as I explained, I've been very attentive not only follow the instructions for concurrent fpga and analysis but also to model my VI by the example of VI, even if only for the moment, just to try to work things out.

Any help would be appreciated as I need to fix this for the further development and I am somehow in a lack of time. I opened a support ticket (reference #7256226), but the app engineer had no time to answer.

My system:

cRIO-9014 controller RT with crio-9104 bottom of basket.

LabVIEW 2009

Latest drivers and peripheral software pc and rio (RIO scan 3.2 engine support june2009)

rex1030 wrote:

I'm reading a 9236 9237 and a 9215 with the scanning engine and read from two 9211 modules with the fpga. It's because I need to acquire to 200 Hz with the 9236 9237 9215 but maximum rate of the scan engine is limited by the slower module in the system, which in this case is the max of 15 hz the 9211.

This should not be the case. 9211 data will not update with each sweep, but you should be able to run the scan faster than 15 Hz without problem. Do you have specific issues with this?

So to use both interfaces (scan engine and fpga), I followed the percisely given in this article for instructions.

1. the project has created and added the peripheral crio using the interface of the scan engine.

2. Add the target fpga and drag and drop the 9211 inside modules

3. has created the fpga in interface file with and compiled with no error.

4. interfaced with the file fpga at almost exactly the way the sample project of "getting started with 9211' by using the engine of analysis in the interface with the other modules.

5. after the errors to discover that I created a VI that tests for just the portion 9211 code (called "thermocouple FPGA method Test.vi")

You can try making sure that the chassis is set to mode Interface FPGA and the setting is deployed. I wrote that article that you referenced says will select the deploy option later and not explicitly speak to deploy the chassis later. Run a VI with a reference open FPGA vi not automatically deploy chassis settings if you need to do it explicitly. Try the following steps.

1. right click on the frame element and select Properties. Make sure that the Interface FPGA option button is selected. \

2. right click on the frame element and select deploy.

3. repeat your VI.

The data returned by the interface fpga was nothing else than zeros on all channels, even if thermocouples were hooked on some of them. (all zeros as entries in the convert temperature vi gives-410, 6160 degrees F, if you happen to have the material to try this.)

I get the following error from the open fpga vi reference:

code error-61141

"Thermocouple method Test.vi FPGA.

Activities FPGA:Open FPGA interface reference.

Reserved for LabVIEW FPGA outside: The RIO Scan Interface is running. You must set the mode Interface FPGA chassis in order to unlock the FPGA. »The likely cause of this error is that the setting of the FPGA Interface on the chassis has not been deployed. If the chassis is still Mode Scan fixed personality bitfile will be loaded on startup and the FPGA will be locked.

It's extremely frustrating, because as I explained, I've been very attentive not only follow the instructions for concurrent fpga and analysis but also to model my VI by the example of VI, even if only for the moment, just to try to work things out.

I'm sorry that you have had difficulties. Assuming that I'm wrong about the source of your problem, it seems we have to update less than Ko to include the deployment step.

Any help would be appreciated as I need to fix this for the further development and I am somehow in a lack of time. I opened a support ticket (reference #7256226), but the app engineer had no time to answer.

My system:

cRIO-9014 controller RT with crio-9104 bottom of basket.

LabVIEW 2009

Latest drivers and peripheral software pc and rio (RIO scan 3.2 engine support june2009)

-

cRIO exe "before the communication of the Commission" and no LabVIEW

I have a project with a cRIO VI and an FPGA VI. The cRIO VI is run with 'communication front' which means that the front is open on the Windows host. Is it possible to create a stand-alone executable file that I could place it on a laptop that has no installed LabVIEW (just free runtime) which allows the façade with the cRIO VI communication?

If not, is it possible if I used a web interface or another method instead?

If this is not possible, what is the solution preferred - create a host VI that communicates via variables shared with the cRIO VI; make a cRIO exe and deploy as that of starting on the cRIO; can make a host exe?

You want to use a remote façade. Once you set up, you can communicate with the front panel on the network, even through your browser if you want.

-

seeing cRIO of State flashes 4 times, but the prog works well until you restart cRIO

I have a cRIO 9073 with a significant program in RT and FPGA, using a front-end for Windows communicating using the network of shared on the cRIO variables. Great short program if I simply deploy the RT VI main (with of course built FPGA code), or if I deploy the RT version. However, if I select 'run as starting", works to deploy on the main façade of RT VI opens and I see activity (it works very well), but then I click to restart the cRIO, and the cRIO restarts only to run for a second or two before the status light blinks 4 times (soft error).

I doubt it's a problem of memory as suggested by the manual as if it were the case, I expect the deployed application would fail as well, but it works very well. I have check the fault log and see nothing useful. I see also on the deployment of the cRIO dialog box has ~ 12 MB free after the deployment, if I deploy against a target with the "NOR-RIO 3.6.0" software - January 2011, and further if I use a minimum package with additional components, I need (network engine Variable and editor of State system).

It was a project of years which worked beautifully and recently required change. In the meantime, my development PC has been updated with Windows 7 64 bit. I am running LabVIEW 2010 SP1 Professional Development System with RT and FPGA packages. CPU utilization on the cRIO when I run the deployed application (with the cover available for diagnostics) is about 20%.

Any suggestions?

Thank you

Erik

I found my problem, and it was mine and not Windows.

I ended up using the Console output for help and saw Exception Code 6 (0 x 00000006) appear on the console, ultimately ending with Safe Mode - software in Max error message unfortunately, I can't find anything looking for this exception code, so I went back and looked at my VI in real-time , and I found my problem: I had added two new network static Variables (NSV) and had not fixed the reference to the Relative target Mode. I have so many DRVS in this VI that I had not also wired their outputs error to an indicator for troubleshooting. Since I have it, but even that resulting in still mode safe, if I have returned the absolute reference Mode.

I suspect that the VI has run in interactive mode, as the project was the IP address of the cRIO set when the RT build was made and later failed, because the IP address changed when the cRIO was on the network. Oddly, I had a lot more luck for the cRIO to run in mode interactive (then disconnect from it) if my PC and the cRIO were connected by a crossover cable, and both have been using link-local addressing. In this way, I could get my project running every time. When I later tried connecting via the network, it is when same interactive mode would fail most of the time.

Unfortunately, a mini-project, I created to test this situation was not the issue - it could not run (if I built the RT build by setting the IP address of the target to an imaginary device) or ran very well (if I put the address IP target correctly prior to construction), but never caused the cRIO enter Safe Mode.

What I want to know is, can be an option somewhere to make all default DRVS for the target Relative to the reference Mode? I have not yet used an intentionally used this absolute addressing. I also recommend to the reference on the NSV Mode indicator something more obvious than a tiny symbol OR in the lower left corner.

Thank you

Erik

P.S. I created a support for this request and the console log provided to support engineer if this is useful.

-

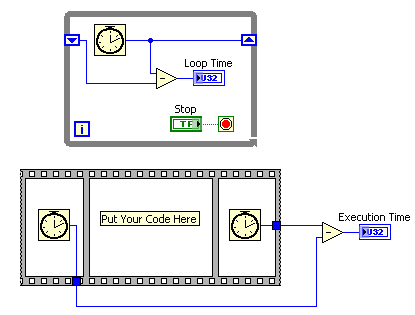

Host VI and cRIO execution time

Hello

I have a cRIO 9014, I run an application real-time with two loops and a host of VI in my PC, the host VI is slow kynda, but I would like to know if there is a way to check if the cRIO rotates at the speed it should run.

Thank you.

-Luis

Luis,

Here are the two methods for timing your code that I described in my last post. The top then loop uses a shift for you register say how long (ms) takes of each iteration of the loop. The structure of the bottom flat sequence will measure how much time (ms) a section of code takes to run.

-

Unable to connect to cRIO (OK in MAX)

Hello

I am exploiting my cRIO from a different computer than usual (after the usual hard drive has failed) and having connection problems. The two are running LabVIEW 2013 and Max I can see LabVIEW 13.0.0 in real-time as well as NOR-RIO 13.0 and NOR-RIO IO Scan 13.0 are all installed. MAX said that the cRIO is connected and running.

However, in my project, I can't connect to the cRIO properly (right-click, 'Connect' does nothing, and the "LED" on the icon stays dark). If I open a new VI on the cRIO, he can run and read data from the modules, but has no function or the controls available in the menus. In the Project Explorer, the RIO appears with the message "features not available."

I've attached a screenshot of diagnosis to explain the situation.

Thanks in advance for your advice.

See you soon,.

Elizabeth

It would be useful to see what software is installed on your local computer, rather than on the cRIO. Most probably, you have not the Toolbox in real time on the PC.

-

Hello. My name is Jason. I'm working on what should be a very simple project to form a collaborator on the material OR that we work.

I used this equipment in the past to remotely control a ranger xp. I tried to use the exact configuration of the code... I'm not sure what I did wrong.

Screenshots of the Project Explorer, and the screw runs on the PC, the cRIO FPGA have all set up and.

The goal

I want to be able to Flash an LED using the crio and control the speed of the flashing of a VI running on my PC. The VI running on the PC has a slide to control the speed of blinking and a Boolean switch to activate and deactivate. The VI on the cRIO multiply the speed by two and shows the State of the Boolean switch. These values are passed to the FPGA VI which is supposed to turn off the led market and stop.

The problem

The PC code and cRIO seem to do exactly what I want to do. Digital i/o does not value. There is no error coming out blocks of reference or FPGA read/write.

I didn't know where to post this because I can't see the error is coming from. The only error I have found is when I right click on the program, I wrote and respected to run on the fpga and try to download it. This error - 50001 and causes "an attribute whether explicit or implied is not relevant or is not relevant given the current state of the system. The operation could not be performed as indicated. »

The system hardware

I have a PC running Labview 8.2 (ip or subnet address 192.168.0.70 255.255.255.0) it is connected with a cable crossed to a cRIO 9004 (address ip 192.168.0.2 255.255.255.0 sn) and a cRIO-9104 chassis. The cRIO has a digital I/o module (NI 9401).

Software

LabView 8.20

Module FPGA 8.2.0

Module time real 8.20

any help/advice/tips would be greatly appreciated.

Thank you

JAson

Hi jcoates,

Please take a look at this knowledge base article: Why do I get error 50003 when you run an FPGA VI on my real-time controller?

If this does not resolve the problem, you are able to get a simple FPGA VI, which does not interact with the LED work?

-

[FPGA] Problem with the sinusoidal signal generator

Hello!

At first I want to apologize for my English is not my mother tongue.

Hardware and software I use is:

LabVIEW 8.5

NEITHER RIO 2.4.1

NEITHER cRIO-9014 (controller in time real CompactRIO)

NEITHER cRIO-9104 (chassis and FPGA)

NEITHER 9264 (16 channels, +-10V, 16-bit voltage analogue output Module)

I made a very simple FPGA VI: a while loop, generator of sinusoidal signal and a FPGA of e/s node in the loop. I've specified the Gnerator settings by following the path:

Frequency = 50 Hz

Amplitude = 1

Phase shift = 0.00

Size of the table look-up = 1024

= 16-bit amplitude resolutionFPGA clock frequency (40 MHz)

But the wave of "sine" I got is not what I wanted to get. First of all, its amplitude is 1 V. shouldn't it be coded on 16 bits? If I wanted to get 1V I should have specified Amplitude as a 3277. In addition, 'sine' is not very detailed, it's look like "steps", as many samples vere missing. What I did wrong? I checked the samples and tutorials, I did everything the same way. A I forgot something or not has not specify other parameters?

Thanks a lot for your help!

OK, I solved a problem. It's embarrassing to admit, but maybe this will help someone else

I blame my inexperience

I blame my inexperience

The main solution to the problem was changing calibration of calibrated RAW Mode. After that, everythoing works as expected. I had a problem with a sample because I was using a multiplier to control the generated sine wave amplitude. But... She was set to 1 in the sinusoidal signal generator. That was the reason for waveform Gradin. Please, don't laugh too much

In any case, thank you for an answer! It is now resolved

-

Unable to connect the server compilation

I am trying to load the FPGA VI tutorial on my 9004 cRIO device and get this error when compiling

The compile server doesn't have all available worker who can make a compilation of Xilinx 10.1.

* You may not have installed the correct build tools.

* The worker local compilation can be configured to a different compile server.

* The local compilation worker can be in an error state.Details

123002 error occurred in niFpgaCompileFarm_OpenJob.viPossible reasons:

NEITHER the farm: no worker has registered the name of given capacity.

«"" "String of full appeal:»»"»

niFpgaCompileFarm_OpenJob.vi

niFpgaCompileWorker_OpenJob.vi

niFpgaCompile_Worker.vi:1Departure time: 17:50:14

End time: 17:51:07

Total time: 00:00:54I try to acess manually the worker compilation .exe file and it says that the installation of xilinx tool should be checked. and that it could not load a file. (SEE ATTACHMENT)

I'm not trying to connect to any remote computer. its local server. Here are my computer details

WIN 7 32 bit

LV 2010 full dev

LV fpga in real time all the latest

Xilinx 10.1 (my chassis is crio-9104 using a virtex-II Bridge)

I read that xilinx has no full support for WIN 7 not yet. and seen on their website too. But I do not see other ppl with a few problems on the server for compilation with WIN 7 OS, but seems to have solved the problem (although not similar to mine). Which means they made it work somehow. (xilinx Web site says also that he has LIMITED support for win 7)

I'm really stuck here. I'm still in my learning and (just trying to compile the tutorial VI!) and I don't want to waste time. I feel really stuck here. any help would be great!

Thank you!

Rajesh

Ok. I think I got it. I've reset my network connection and asked to labview to compile. could not connect to compile the server. While crossing retry to connect, I launched the server compile manually, by clicking on the compilation server.exe and then done labview link. I guess I have overlooked some instruction somewhere that compile server.exe must be launched before making an attempt on the compilation.

-

Causing problems of custom data type to deploy the shared target RT variable

I seem to have some difficulty in using a shared variable published network created from a customized data type when it is deployed as an executable on a target of cRIO RT. I'll start by describing why I think that this is the rub. I created my RT VI in the LabVIEW (LV 2012) development environment and everything works fine. This VI is quite simple, because these were quickly devolved into an exercise in debugging. The RT VI begins by simply flashing the LED to a couple of times and then starts a loop simple acquisition to read some values out of the material using the analytical engine (while still flashing the LED of the user). After reading the material, the values are grouped in a cluster and written in a shared variable published to the network defined by a custom control type def. The custom control contains five floats double precision. If it's important, the RT cRIO system hosts the shared variable in this case.

So I have that deploy in the development environment, and everything works fine. The LED flashes merrily along, telling me that the program runs correctly. Running a VI host who reads the shared network has published variable gives the desired result. Everything is good.

Now, I want the cRIO system to run this simple program by itself at startup. I build, set it as start VI, deploy it, and then restart the cRIO target. The LED never flashing... the VI doesn't seem to work. I'll spare you the major part of the work of debugging and access to the end. I basically "diagram Disabled" various sections of the code up to the VI began to run correctly in an executable file. I kept reducing the size of the disabled code until something has been disabled: the writing in the shared variable for the custom data type.

So, I guess my question is this: are custom data types defined by type def would be personalized orders authorized executables to RT? I read through the cRIO Developers Guide, my book of development in real time course of NOR and the white paper using shared Variables and I see nothing that forbids it. I know that there are things not allowed in the executable files that are allowed in the development environment (property nodes façade, dialogue live, operating system specific calls, etc.), but no mention of the shared variable type custom data. Any ideas as to why my VI is running in the development environment, but does not update unless I have delete the entry on the published network variable shared?

Thank you in advance for your help!

You must disconnect the data types of variables and then recompile. You can find it useful to keep on disk, a copy of the original lvlib.

Don't know if this is a bug or not. It was suggested by someone in the forum that putting the ctl files in the right position (the disk? in the draft?) would allow the rtexe start; I did a quick check and it didn't work then I dropped the tests more far.

-

FPGA and RT - change rtexe and little file FTP

Hello

first of all, you can use WebDav to transfer files to your cRIO-9066 (which runs the operating system Linux RT).

You can check the file of ni - rt.ini in the folder/etc/natinst/share /.

You can also read this and this for the programmatic framework for the startup application.

I hope this helps!

Bye!

Licia

-

execution for FPGA parallel code problem

Hello

I have a problem with the execution of the code in parallel on the FPGA to a cRIO-9073.

Running the code takes more time than expected.

The problem is described in the attached PDF file.Kind regards

Beurms Jasper

Hi Jasper,.

the first problem is due to DATA streams! THINK THE STREAM!

You have three simultaneous sequences. The loop iteration time depends on the slowest component in the loop. If you don't need to ask why the 'low frequency sequence' minimalist other sequences?

The 2nd problem cannot be discussed looking at the pictures. What are those who wait function? milliseconds, microseconds, ticks?

Did you know that the IO nodes also take some time to treatment?

Maybe you are looking for

-

When I enter on: config page and try to change the new settings of the about tab: empty it changes them, but when I opened a new tab it opens this "quick start" and it shows windows with a few sites I visit, but there is no option in which I choose i

-

where is my junk e-mail folder

Quite simply, I find no junk e-mail.

-

Has anyone installed Ubuntu netbook remix 9.04

Last weekend, I downloaded and installed the beta version of UNR 9.04 on a USB key. Had a quick play with it on the Toshiba and it seemed to work OK in addition to being unable to scroll with the touchpad, I think it's related to this bug https://bug

-

Is the another way to get the download from the support section

Is there another way to get the download from the support section? Because the download speed is very slow. For example, in the new version of the value-added packaging and its 116 MB big need. A normal download time would be approximately 5-10 minut

-

How can I retrieve a deleted program? (DBMS)

We have a HP G50 laptop. He started running extremely slow about a week or two ago, so I went in programs/features and the only thing that has been installed in the last 2 weeks has been a microsoft program. Fearing that it was a type of virus, I d