Delay of data acquisition

Hi all

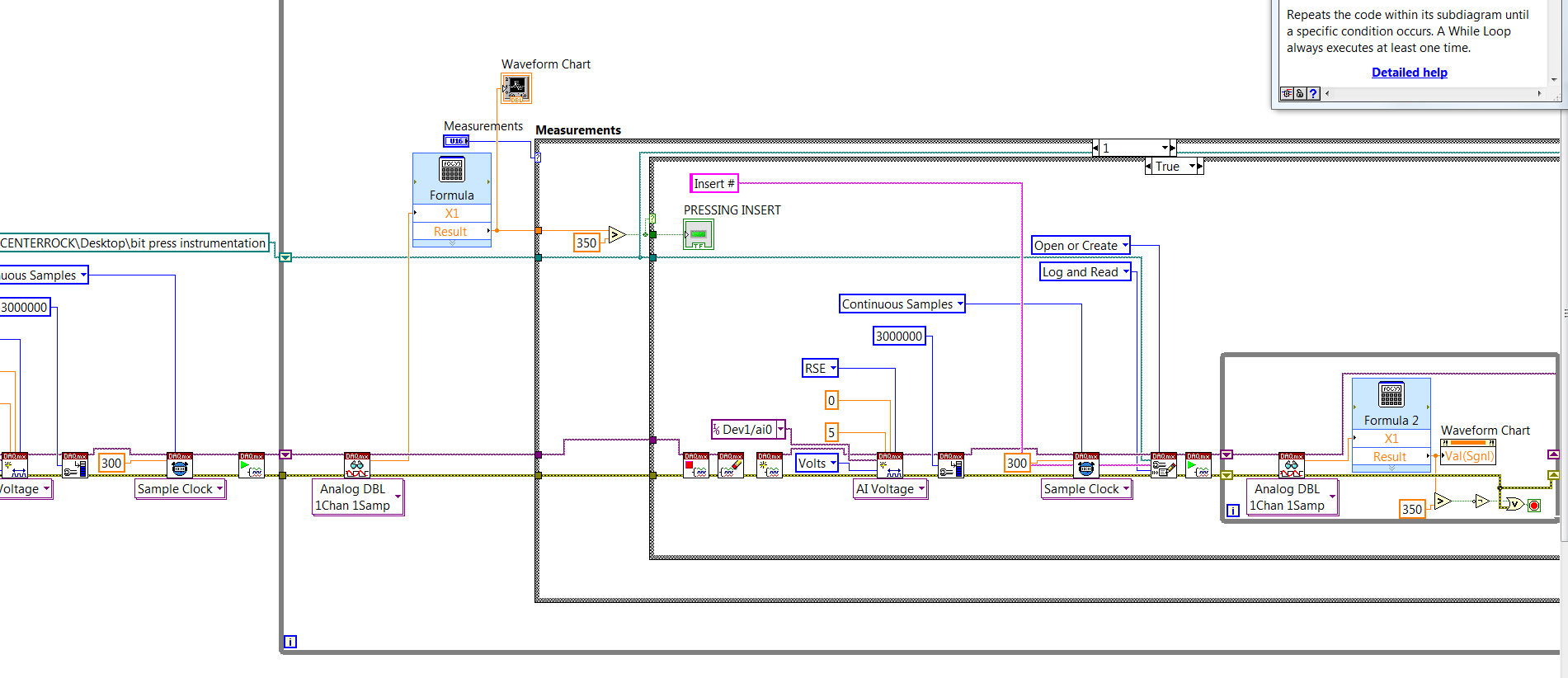

I have a problem with my code (appropriate section below image) and I hope you guys can help me understand why I encounter the problem that I am. The problem has to do with the rate of acquisition the daqmx sample clock. When my VI is running, there is no prblem with the data displayed on the wave at the start regardless of the acquisition rate specified by I. However, when the true case is initiated within the structure of box 1 and I reset my daqmx task, I experience extreme data late (the waveform chart recording of data and user input lags far behind data changes) problems if I put more than 400 Hz acquisition rate. Because as long as I keep less than 400 all acquisition rate seems to work fine but once I go above this rate, I experience the problem only when the true condition is satisfied within the structure of box 1 and so I spend to acquire and read that data in time in loop that are inside the structure of the case. I hope that my explanation of the problem is clear enough and I would appreciate any idea as to what could happen here. Thank you.

I think that your delay is due to this property node. A property node is HORRIBLY slow to write. The simple solution would be to replace it with a local variable.

A better solution would be to use producer/consumer architecture. Since it seems that you care only about saving data when above 300, you could just enqueue the data when above 300, then your just recorder are there and waiting for the data to be when you are less than 300. This will help since you won't have to destroy and recreate your task, and duplicate code. This is one of the few times that I would recommend not not to use DAQmx Logging ability.

Tags: NI Software

Similar Questions

-

Configuration of delay IO in 6587 of NI Data Acquisition

Hello

I'm reading LVDS data using adaptation module with module FPGA 7966R 6587. The external clock that I receive is identical to data (just hi-lo swing). In order to capture the data I need to move to the phase of the clock by a quarter clock cycle to get more stable data values. As the clock of TIME is not accessible (always set to 0) I think spend all my data accordingly. I have some questions on how to use DATA_IDELAY_INCREMENT to do this.

(a) high-level logical DATA_IDELAY_INCREMENT increases the delay of data by a single tap by ACQ_REGIONAL_CLOCK, where a single tap is 78.125ps nominal, so what do I do to get a period of 400ps? Is linked to the number of edges mounted on DATA_IDELAY_INCREMENT?

(b) how I use IDELAY_CALIBRATION_CLOCK?

mbothra,

To answer your first question, you must have a loop configuration that sets DATA_IDELAY_INCREMENT to true for a lot of clock ticks that you need to reach 400 ps. The DATA_IDELAY_INCREMENT node sets the entry activate the primitive IODELAY Xilinx to true, and the direction of the IODELAY is hardcoded to always increment. This means that for each beat clock where the node DATA_IDELAY_INCREMENT is true, the delay increases by 78,125 ps.

In your case, you would need to graduations to 400/78,125 or 5.12 (is rounded down to 5 graduations for 390,625 ps or delay up to 6 ticks for a delay of 468,75 ps). For this implementation, you might have a loop single cycle timed for the number of iterations, you need, stop the loop, and then start your curls for the acquisition of real data.

For your second question, the IDELAY_CALIBRATION_CLOCK is locked at 200 MHz. There is no change that you can do with this value to cause any kind of delay.

-

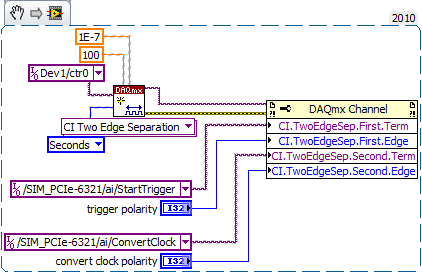

delay between the trigger and data acquisition

Hi, I use NI SMU-6368 as a tool for data acquisition. In my experience, I use an external digital trigger to start taking measures of a thermistor.

However, before the experience, I want to know the time that elapses between the detection of the trigger signal and data acquisition start time.

Is there a way to do this?

Here's the kind of thing I configure to get an accurate measure of time of t = 0 trigger signal to the

the actual first A/D conversion. It may be too much for a measurement of the temperature, but you should get

the right track.

-Kevin P

-

Several timers loop data acquisition

Hi all

I am developing a VI for FPGA Deployment. My equipment consists of a chassis/controller for cRIO-9072 with module 1-9211 thermocouple, card SD-1 module, 3-9215 HAVE modules and universal modules 2-9219. I will collect data of two thermocouples on the 9211, 14 channels on 9215 channels and 6 on 9219 modules. This system communicates to the host via ethernet.

I have prepared a vi (see attachment), which used two DMA FIFO for writing data to data acquisition at a different speed. I will be sampling the s and 9211 9219 much more slow (500ms by samples), than other channels (40 ch/kech. / s). Currently, my FPGA vi trying only to taste two different modules. When I run the present on the host vi and try to read the data, I get only extracts of the data at different intervals. If either of her would reveal latency with the connection or the host vi failed to refresh quite quickly? I am relatively new to labview, so any help is appreciated. Thank you.

Gaussy

Hi Guassy,

There are a few things that you need to change:

(1) you must separate your acquisition in the FPGA in two separate loops if they have to operate at different speeds. As it is, probably will run at the slower speed of the two parameters.

(2) you must do the same in your VI in real time, or set up the DMA readings so that they will be read at the same pace. For example, suppose that a single module acquires 1000 hz and the other at 200 hz. If you want to read 100 samples from the first module (so your reading will occur at 1000 hz / 100 samples = 10 hz), you will need to read 20 samples from the slower module, so it is synchronized with the first module.

(3) your timeouts are too short on your DMA readings. Your slow acquisition is 500 us. It will take 50 ms to read 100 samples requested, but the delay is set for 10 ms, so 4 times over 5 playback will return nothing.

(4) you use graphics and no graphics. A chart will only show the current data buffer that was written for her. Refresh rate of the façade is nondeterministic, so that you can't see every update. If you use a chart, the chart will record all data written on it to the indicated depth (default is 1024 elements).

Also remember that you can have three FIFOs DMA between the host and the target FPGA, so use them wisely. It is often easier to perform your purchases on the FPGA at the same pace and send them through the DMA FIFO even in VI in real-time. If you need a few channels to connect at a lower rate, you can always throw the excess samples (there are some decimate wave screws that are perfect for this).

I hope that helps!

-

How to find the time between two channels of entry in the data acquisition card or pci 6036

Hello

I read a lot-related posts on the simultaneous measurement of two input voltage of similar channels in map data acquisition. I know that the best material is "simultaneous measurments of the Series DAQ cards" but I only pci data acquisition card 6036 and I try to understand what is the time between the reading of the two channels . This period is always constant? (must it rely on a voltage (amplitude, frequency, waveform..). I send the sine wave (s) to the two channels and read the values of V, if they read the same value, the difference should always be zero but I get-0,002 to 0.002 Volt difference (I must find a way to convert it in time). A screenshot of my VI is attached. I wonder how I can accurately measure the time delay between the channel.

I am open to any suggestion, my final goal to read exactly two channels at the same time ((ou connaître le délai exact donc je peux correspondre les données correspondantes étant donné le temps de retard))

Hi spinup,

better you should post your question in the forum of LabVIEW, LabWindows/CVI is used

Good luck.

-

the relay control data acquisition

I am creating a vi that controls (press and release) several relay using a USB 6501 data acquisition. This should be a task relativily easy but I get flumoxed by errors. I tried to use the examples, but I get an error telling me that I need to use the mode of generation 1 sample (on request). Help, please

Sure. The easiest way is to have a DAQmx writing followed by a function of delay, followed by another entry, followed by another period. Simply plug the error links in order to control the flow of data. However, the VI would be insensitive so you can use a state machine or function elapsed time so that the VI can be stopped without waiting for waiting for him at the end.

-

You can trigger through communication Modbus TCP/IP PLC data acquisition without using a loop for?

Hello

I am trying to contact a facility through a Modbus TCP/IP communication PLC. I'm new to this method, but the idea is that the installation will send the logical (Boolean) values 1 bit by ethernet to my workstation which read and then will begin data acquisition. Basically, I need a triger to come to my pc. I placed my vi inside a structure case T/F which will run according to the signal, it receives data acquisition. However, for it constantly waiting, I put this in a loop for. The works of vi, but playback signals sometimes lagging behind due to the loop for. If I take the loop out and just run labview permanently, it works perfectly, but I know that the option is only for debugging and should not be used. So my question is, is there a better way to wait for an incoming signal?

Hello!

Please note that the order of execution of the write operations on the shared variable 000002 is not determined.

For example, nothing prevents this order of execution:

(1) value false 000002

(2) set to true 000002

(3) execution of the loop

In what concerns the delay, you might consider placing a waiting vi in the case of 'false', or the loop uses 100% of CPU if I'm not mistaken...

Kind regards

Marco

-

Real-time display at the high frequency of data acquisition with continuous recording

Hi all

I encountered a problem and you need help.

I collect tensions and corresponding currents via a card PCI-6221. While acquiriing data, I would like to see the values on a XY graph, so that I can also check current vs only voltage/current / time. In addition, data should be recorded on the acquisition.

First, I create hannels to analog input with the Virutal DAQmx channel create, then I set the sampling frequency and the mode and begin the tasks. The DAQmx.Read is placed in a while loop. Because of the high noise to signal, I want to average for example every 200 points of the current and acquired for this draw versus the average acquisition time or average voltage. The recording of the data should also appear in the while loop.

The first thing, I thought, was to run in continuous Mode data acquisition and utilization for example 10 k s/s sampling frequency. The DAQmx.Read is set to 1 D Wfm N Chan N Samp (there are 4 channels in total) and the number of samples per channel for example is 1000 to avoid the errors/subscribe for more of the buffer. Each of these packages of 1000 samples should be separatet (I use Index Array at the moment). After gaining separate waveforms out of table 1 d of waveforms, I extracted the value of Y to get items of waveform. The error that results must then be treated to get average values.

But how to get these averages without delaying my code?

My idea/concern is this: I've read 1000 samples after about 0.1 s. These then are divded into single waveforms, time information are subtracted, a sort of loop to sprawl is used (I don't know how this exactly), the data are transferred to a XY Chart and saved to a .dat file. After all that's happened (I hope I understood correctly the flow of data within a while loop), the code in the while loop again then 1000 samples read and are processed.

But if the treatment was too long the DAQmx.Read runs too late and cycle to cycle, reading buffer behind the generation of data on the card PCI-6221.

This concern is reasonable? And how can I get around this? Does anyone know a way to average and save the data?

I mean, the first thing that I would consider increasing the number of samples per channel, but this also increases the duration of the data processing.

The other question is on the calendar. If I understand correctly, the timestamp is generated once when the task starts (with the DAQmxStartTask) and the time difference betweeen the datapoints is then computed by 1 divded by the sampling frequency. However, if the treatment takes considerable time, how can I make sure, that this error does not accumulate?

I'm sorry for the long plain text!

You can find my attached example-vi(only to show roughly what I was thinking, I know there are two averaging-functions and the rate are not correctly set now).

Best wishes and thank you in advance,

MR. KSE

PS: I should add: imagine the acquisition of data running on a really old and slow PC, for example a Pentium III.

PPS: I do not know why, but I can't reach my vi...

-

Card FPGA and data acquisition synchronization

Hi, we are control and data acquisition of several hardware devices (including Photodetectors and translational stages). Until last week, we used all the controls and acquisition using a PCIe-7852R FPGA board. However, we decided to move the acquisition part to a PCIe 6363 DAQ card to improve the sharpness of the tension. During the test, I found that the internal clocks in the FPGA and the DAQ cards are slightly inconsistent (not just a phase delay, but a difference in the period).

I know because I have generated a square wave (period = 20) using the FPGA and gains using the data acquisition card (at a rate of 200 kHz, that is, 1 taste every 5). I have observed acquired place shifts 5 every 5 seconds approximately. Such a change does not occur if the production and acquisition is done using the same Board. Therefore, the only explanation is that the data acquisition and FPGA cards clock frequencies are different. According to my calculations, the percentage difference between their time clock must be 5/5 s = 0.0001%.

Therefore, I wonder if there is anyway to synchronize clocks between them. Or, is it possible that I can drive the FPGA clock-based DAQ hardware, or vice versa? Also, please let me know if there is something trivial as I fix.

Thank you very much.

Kind regards

Varun

Hi Varun,

my post was only one solution...

Your data acquisition card may take an entry to control sampling of trigger. In this mode, samples draw on a rising edge of the external clock signal. As long as you stay within the limits of the DAQ (100 MHz for your card) material sampling works perfectly. There are even examples coming with LabVIEW explaining how to program your data acquisition card...

This mode use you your FPGA as clock source sampling for data acquisition. Both will run on the FPGA clock in sync. When the FPGA is a bit out of 40 MHz, so it won't matter because both devices are triggered on the same clock signal...

-

I get upgraded my laptop (HP for laptop - 15-r224tx) for Windows 10 but I can't find the driver for the controller of PCI Data Acquisition and Signal Processing. Please help me find the right one.

Thank you!

You are the very welcome.

It is the latest version of the W10 driver for this card model... see if this solves the problem, if you have not already installed this driver.

This package contains the installation package driver for the controller wireless LAN Realtek RTL8723BE/RTL8188EE in the laptop models running a supported operating system.

File name: sp72517.exe

-

PCI Data Acquisition and Signal Processing controller driver

I installed win 8.1x64 on my HP Probook 450 G2, but miss me the driver of PCI Data Acquisition and Signal Processing controller.

Can you please help?

Thank you

Leontina

Hello:

Please see if installing the Intel Chipset driver installs this device.

https://Downloadcenter.Intel.com/Detail_Desc.aspx?DwnldID=20775 & lang = eng & ProdId = 816

-

I just installed Win7 Pro x 86 on my Z600 workstation. It was an upgrade to Windows XP Pro. I'm missing the driver for PCI Data Acquisition and processing of the Signal and Hardlock USB 1.02 controller in Device Manager. Can someone help me find these drivers. I looked on the page of Support/Drivers for this model, but could not find anything.

Hello

You can get assistance on the HP Enterprise Business Forum since you have a professional worktsation.

-

Hello

Need driver for PCI and Signal Processing controller HP 240 G4-328TX Data Acquisition

Can anyone provide me please the link for download it for windows 10

Thank you

Hello:

See if this driver works...

-

Hi, it is impossible for the moment to install the driver for PCI Data Acquisition and Signal Processing.

I downloaded the driver from Intel, and it did not work... I found a version of this site for windows 8.1 unupdated and it does not work.

A little help?

Thank you!

Hello:

It could be one of two different drivers.

Try this one first, and then restart the PC.

This package contains the Intel Chipset Installation utility. This utility allows the operating system to show the correct name for the Intel hardware that is installed in the Microsoft Windows Device Manager. This package is provided for the laptop models running a supported operating system.

FTP://ftp.HP.com/pub/SoftPaq/sp75501-76000/sp75561.exe

If this does not work, try this one...

This package contains the driver which allows Intel platform dynamic and thermal firmware setting. Intel platform dynamic and thermal environment information system temperature and power use for the thermal protection of the system to work properly. This package is provided for the laptop models running a supported operating system.

-

Hi team,

I just install windows 7 edition integral and peripheral Bluetooth windows 8.1 is not be detectable, when I search for problem that I came across this PCI data acquisition and Signal Processing controller driver is missing and a unknown device driver missing shownup in my result of troubleshooting. Please help me

Please find the screenshot for your reference

Thank you

Hello:

See if these drivers work...

CQI PCI controller:

This package contains the driver which allows Intel platform dynamic and thermal firmware setting. Intel platform dynamic and thermal environment information system temperature and power use for the heat of the system

protection to work properly. This package is provided for the laptop models running a supported operating system.File name: sp71638.exe

Bluetooth:

This package contains the installation package driver for Realtek bluetooth in the laptop models running a supported operating system.

File name: sp71288.exe

Unknown dev:

This package provides the HP 3D DriveGuard software (HP ProtectSmart Hard Drive Protection) for the laptop models running a supported operating system. HP 3D DriveGuard software protects the drive hard by parking the heads if cell phone accidentally falls, or is suddenly struck by another object.

File name: sp71811.exe

Maybe you are looking for

-

Beta iOS provisioning profile but remove the software update still shows a update available

If I open the software update menu, then it shows that my iOS is updated. How to get rid of the '1 '? Thank you!

-

HP Deskjet D1660: Cannot install printer or Scanner, does not meet the min requirements

I recently spent computers, from Windows 7 to Windows 7 Professional, and I seem to have install my HP Deskjet D1660 and my scanner, a HP Scanjet G4010 of questions. Both gave me the same problems. When I connected my Deskjet, my PC tried to install

-

A few Questions on the updating of 8.0 to 8.5.1

Hi all I am updating to 8.0 8.5.1 and have a few questions: 1. the drivers I installed in 8.0, I guess they must be installed again to 8.5.1 version correct? Simply install these drivers OR again since the 8.5.1 disc? Is there something I need to wat

-

Lenovo 3000 N200 0769 - could I strap a video about this card?

Hello I know that this question is asked before, but I have not found an answer that is relevant to me. I have a 3000 N200 series, version 0769. the original specs are: Windows Vista Home edition, processor Intel Celeron 550 2.0 Ghz, 1 GB RAM, 160 GB

-

Hello, I'm having a problem with my VPN configuration. I have two locations each with she is has a subnett. I have a VPN site-to site between the two locations. The site to site VPN is up and fully functional without any problem. Now if I'm away from