FIFO DMA

Hello / Hello

I try to pass some trought DMA FIFO data, but I have a timing problem.

I hope to read on rt 0 as 1, 1 as 2nd etc...

Any idea?

I test data paser (0,1,2, 3.6, 7) since an FPGA to a RT but I can't read the data into an orde fixed kind, the then 1 0 en 1 etc...

Any idea what's wrong in my code?

BR/thank you

Found!

I read 100 element and write 8 by 8 element, 100 is not a multiple of 8.

read 80 work item

Tags: NI Software

Similar Questions

-

Hi all

I'm under LabView 2013 and have updated all drivers and versions on my local computer and also on the Single Board RIO 9636 I use. My goal is to measure 4 similar entries corresponding to four different microphones and then each individual signal as an output wave form. I try this using the FIFO DMA 4.

The problem that I am running is that I am not able to read data from the RT Microprocesssor VI using the FIFO 4. Reading methods. I'm relatively new to using a FPGA and labVIEW programming. I attach two diagrams for information purposes. I thank in advance for any help, you may be able to provide.

mcoe12 wrote:

What happens is that data from the FIFO are just 1 and the real are not the case of the incoming data.

AH! If you said that in the first place, I have identified the problem in the first post. It seems that your data types do not match - fixed point for the FIFO DMA configuration does not match data from the analog input. That's what the small red "points of coercion" you are showing on writing of FIFO. My guess is that's why data is not properly through.

While you edit digital representations, also change the sampling frequency is an integer, to match the input of the timer.

-

Accuracy of size for the FIFO DMA

I started to develop a code of RT for cRIO with DMA FIFO function application. A few questions have very fundemental

fluctuated around in my mind. The FIFO DMA is supposed to be made up of two components FPGA)

side & on the RT side).

1 the total THAT FIFO composed of FPGA side FIFO + RT side FIFO?

2. the FIFO of DMA size that I put inside the FPGA target in the Project Explorer refers to what just FPGA)

FIFO or Total size)? If it's just FPGA side FIFO, how big is the RT side FIFO together (is

It automatically assigned by RTOS free memory function)?

3. in addition, size defined programmatically by using DMA-configure is the equivalent of setting the size

in the Project Explorer?

4. Finally, how can I estimate the maximum size of the FIFO that I am allowed to use?

Thanks in advance for any response.

Hi Shiva419,

1. Yes, at least a DMA FIFO has these two sides

2. I just read in another reply that the size you set for the FIFO in the Project Explorer is the size of the FIFO on the side FPGA. The size of the FPGA on the side of the RT is much larger (default is 10000 items).

http://forums.NI.com/NI/board/message?board.ID=280&message.ID=5108&query.ID=99697#M5108

Mandar-

-

Hi al, it's a long!

I noticed a strange behaviour when I read from a FIFO DMA between FPGA and RT host on my crio (9014 controller and 9104 bottom of basket). The FPGA is writing data to the FIFO 2 points every millisecond and the loop of the RT is the reading of 500 data points each loop of the MS 250 CR period is controlled using the hold until the next ms multiple function.

Wait until the next use means ms that during the first round, the wait will be not so I gave the FIFO DMA read method a timeout of 750ms to allow data points to accumulate on this first iteration.

I then ran the VI and it read the data as planned and it was always 0 in the FIFO. Then using the system monitor, I noticed the CPU usage on the RIO and was surprised to see that it was 30%

!

!After a lot of puzzle and many other attempts as to set the timeout to zero if delays fair read until here, I've decided are enough data points and then executes a little behind so that there is always a constant number (non-zero) of data points in the FIFO. Now, the VI runs and only use about 3% CPU.

I thought that in the first case as I read exactly the number of points in the FIFO that I was tripping some kind of voting behavior in the playback feature which has been hogging the cpu.

So I ran a business with a zero time-out, where I was reading with 0 points of data to the left in the FIFO as in the first case and waited to see if the delay of read but it never does and the CPU usage is normal.

So what's happening? I'm puzzled!

Thank you

Steve.

Hi Steve,.

I think I can explain the use processor behavior that you are experiencing:

Case 1: Loop with nonzero time-out

-Your code starts with wait a multiple ms: This means that a 0-250 ms timeout occurs (on average 125 ms)

-Then your code tries to read 500 data points in the DMA FIFO (if 500 points come in every 250 ms). All data cannot be presented yet.

-If 500 points are not yet ready, polling occurs until they are. During the time of the poll, the CPU usage is high. Finally, the data is read.

-The next iteration of the loop begins.

-The code is now expected up to 250 ms after the last function call until the next ms Multiple. Roughly the same amount of data should be available by the end of this expectation as in the last iteration. Therefore, the question about the next FIFO DMA read should be roughly the same, and the CPU usage will remain high.

Case 2: Loop with zero time-out

-In your code, immediately after the first call to wait until the next multiple ms, you "synchronize" by reading all the remaining data from the FIFO.

-In the next iteration of the loop, we can expect the call until the next ms Multiple wait the entire 250 m means that the data DMA FIFO (discount jitter) should be ready. If jitter is low enough, this will result in delays very little of the read DMA FIFO and a low CPU usage.

I would recommend either using a timed loop and read the exact number of data points available (if your application can handle variable size data sets), or using a while loop as you are and make sure that the loop priorities are defined such that the CPU usage high does not affect critical functionality.

Thank you for the very good question; I personally really like thinking through these issues! Please let me know if you have any questions that deserve further discussion and have a nice day!

Kind regards

Casey Weltzin

Product Manager, LabVIEW Real-time

National Instruments

-

NEITHER 9234 fifo dma file samples

Hello

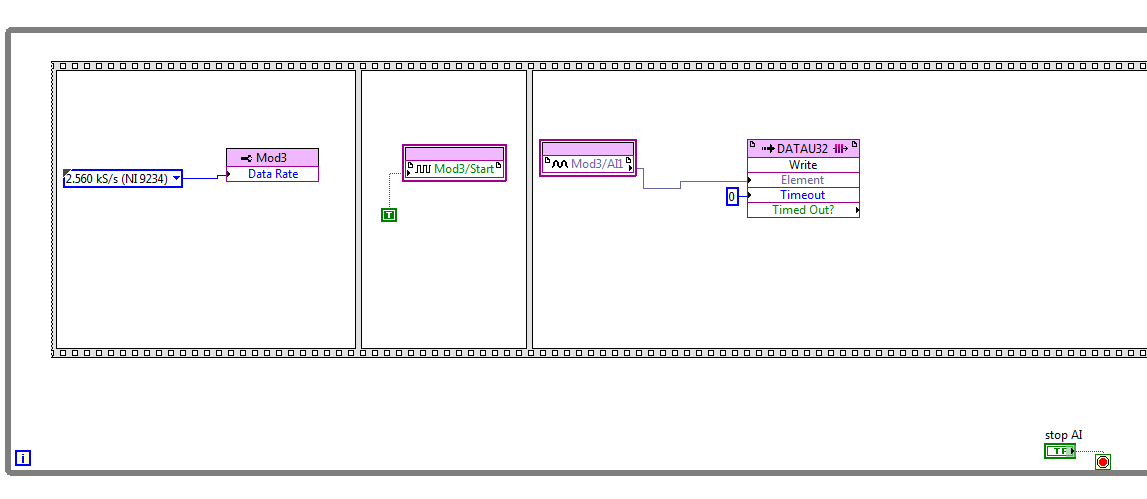

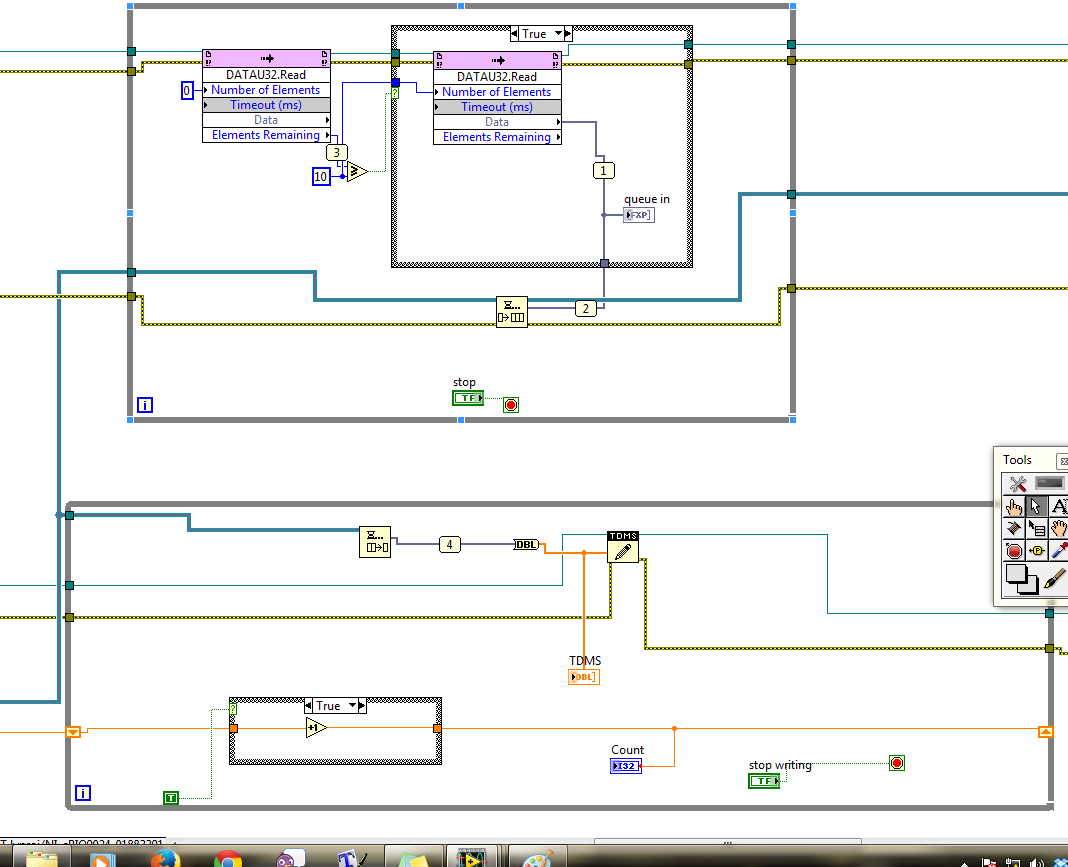

I have a problem when sampling using the cRIO and map AI NI 9234, currently configured to sample a signal of Hz 1 k of the side signal generator FPGA goes directly to the DMA which is (1023 elements in size) on the side of the host (size of the element 1 million). With the help of the producer, architecture of consumption and saving on PDM on the consumer side. The producer has read dma fifo. Please see pictures any help would be great!

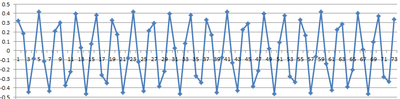

If I plot the data, I get this:

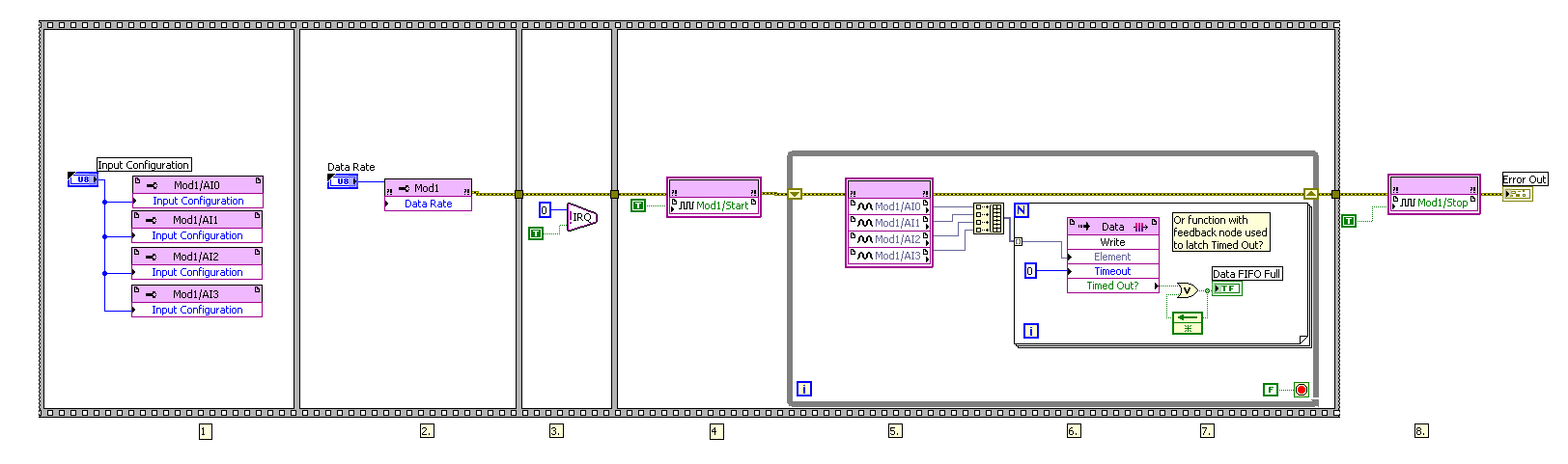

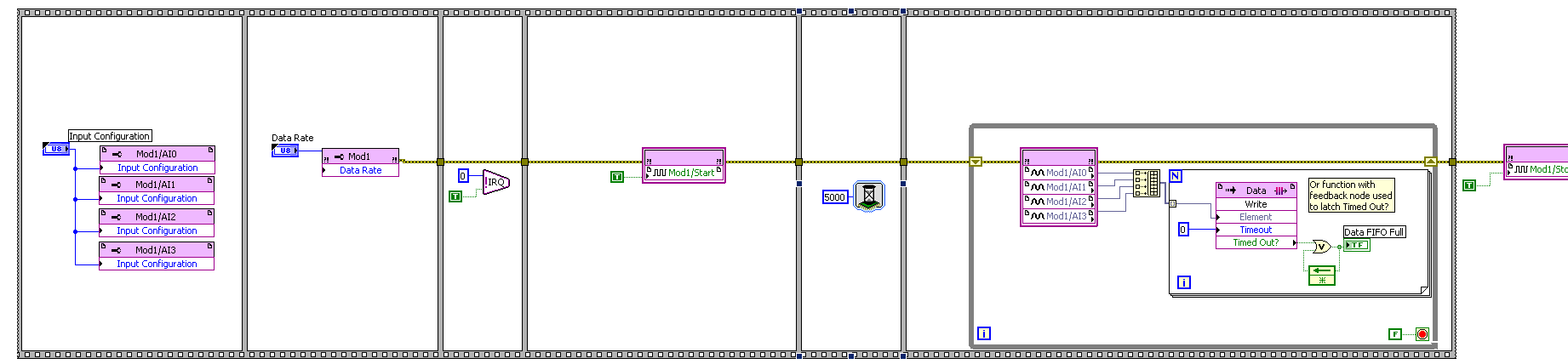

Here is my code FPGA:

Here is my version of the host:

Hello

The problem has been resolved on this post.

Thank you

-

Read and write in two separate FIFOs DMA on RT host

Hello

I have two parallel loops running on a host of RT on a CRio9022. There are two DMA FIFO: one of the FIFO is written for in the upper loop, another FIFO is read from the bottom loop. I've attached a screenshot of my code.

The problem I encounter is that I seem to be only able to run one of these loops - for example if I disable the first loop, I can see data through the second loop. Trying to run them in parallel because I think I've coded it means only one of the tracks-it loops is always the top loop in the code that I have attached the screenshot. Each of the FPGA VIs that run only use a FIFO so I think they should be able to run independently... I was wondering if anyone could shed some light on this?

Thank you

Hello.

You can only have a single call to the FPGA in HOST mode, the algorithm that you post, that is make two calls to the VI 'Reference of VI FPGA open', this is not allowed, this is why the program works only with one of these cycles.

Kind regards.

-

Number of FPGA FIFO DMA channels

Hey there,

to understand some of the problems in my FPGA VI, I wanted to know, as I need to see the count of 3 FIFO of DMA channels available:

(1) the total number of DMA FIFO created in the LabVIEW project

(2) the number of DMA-FIFO-method-nodes of the used in the FPGA VI

In the case of #1, is there a limit using the FIFO-node, or placing them in cases very intertwined Structures?

I've known a few problems in my FPGA VI, while using only two DMA-FIFO and access with the 3-node method on the FPGA VI hole I got the following error message:

There are insufficient DMA channels available on the current target. Too many DMA channels have been requested or some channel requests are conflicting. The current target has 3 DMA channels. Review the list of requested channels and remove one or more to free up resources.So, I looked everywhere, but I have not found the target list of channels requested.

I had only created 2 DMA FIFO in the project, I used only 3 DMA-FIFO-method-nodes in total, and I used only a buffer size of 511 items in each FIFO.

So where can I find the list of channels requested, to see what goes wrong in this VI?

Thank you very much!

In my view, that the limit is the number of DMA channels, referenced in the VI. You can create as many as you want in the project, you just can't use more than three in a FPGA design. You use the scan mode? Who will also use the DMA channels.

-

Release NiFPGA 7842 DMA FIFO after reading memory

Hello

I use the card RIO de Ni7842. I've implemented a block for the acquisition of data on my FPGA (target device) and filling a FIFO to transfer the data from the target to the host machine. I've implemented the FIFO to a size of 10 k. The number of samples that I'm gaining is 16 K on three channels simultaneously.

I read the data from the FIFO DMA implemented on a host machine with the support of the C API for the Council. I have setup the FIFO for read in three steps by launching calls to methods:

-ConfigureFIFO - configure FIFO depth

-FIFO reading - read items in a host DMA - it runs in a loop playback of 1 k datapoints at each iteration (the data type I16's not 2kb which is playing)

-Stop the FIFO

What is the memory allocated on the host DMA by calling method configureFIFO need to be released explicitly by calling ReleaseFIFO? Note that AcquireFIFO is not called here.

Please advice.

Thank you!

In my view, all memory is allocated out during the call to NiFpga_Finalize, but I was not able to find a specific documentation to confirm that.

There is a specific example of FIFO included with the C API of FPGA that my be of interest to you if you have already looked at him.

-

iHi.

My apologies if this is the wrong Board... not sure where it should go! Just to clarify from the outset, I cannot share screws due to issues of IP etc... sigh.

Basically I have a sbRio 9626 and the software that runs on the FPGA to interface with analog converters / digital external. This is done using a machine to States (single cycle loop timed with a structure of business inside, so it passes between cases each tick of the clock FPGA). In one of the cases (the States), I have a little routine that takes data from the ADC and place it in a buffer FIFO of DMA of target-to-host. In fact, there are 4 FIFO DMA buffers to send various information and the value of the sample. It is then read by the software on the host of RT and processed to produce an array of values which I then send to the PC using a shared variable.

What I wanted to check, is that data sent from FPGA to RT host (and PC) are contiguous (that is, I have my right to lengths FIFO). I modified the code FPGA to use a counter instead of the data sampled for the FIFO must simply send numbers in a sequence (1, 2, 3, 4, etc.). I then examine this sequence to ensure that it is correct, and no data has been overwritten.

I think it's the FIFOs, 2, 3 and 4 are very good. FIFO 1 sends data that is continuous but every now and then I seem to get a glitch at random. This glitch is * not * appear to be due to lengths of FIFO, but seems to be an error in the data transfer. For example, I get something like 1, 2, 3, x, 5, 6, 7, y with x and y the seemingly random values. The positions x and y in the sequence are also seemingly random - they have not held in the same place every time. Code written to the FIFO 1 is * exactly * the same thing others - in fact, it's the same group of data being written.

Has anyone seen anything like this before? I am trying to determine if it is due to the goal to receive FIFO or some problem with the shared variable in the network. Any suggestions as to what I could check? It almost seems as if there is IME peaks on the transfer... does not suggest this is the case but it gives an idea of what I see. I'm using Labview 2013 and BIOS on the sbRio is up-to-date. I have sbRio another I'll try again later to see if the problem is specific to a particular board.

It seems that you have found the wrong path here: since you are dealing with the programming of FPGA, which is essentially played woth LabVIEW you should post this question to the Office of LabVIEW or, perhaps, to the Office LabVIEW Embedded

-

DMA with FIFO data acquisition

Hi all

I would like to ask you a favor to get some help to understand FIFO. I have attached the files here and simply the target more basic FIFO of host data transfer. I put the required number of elements to 4095, I understand the depth of the FIFO on FPGA. The sampling rate in FPGA is 10 kHz. The loop on read host rate is 10 ms. The depth in the host FIFO.configure is 10000, which I think is the number of items in the part of host of the FIFO DMA memory. So I guess that the total thickness of the FIFO is 14095 elements. I put the points of reading in each iteration to 2000 points. However no matter how to change the combination and number of points to read, the program performs an iteration and then displays a different error message.

Can someone please help me understand how to calculate each parameter and to optimize it, if the sampling frequency I want on FPGA is data of 10 kHz I16? Thank you very much. I appreciate your help!

Best,

Charles

I have attached all the files here, which is very similar to the example on ni.com

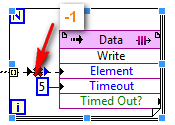

Charles Hey,

Regarding the second question, it's what I wanted. I'm not 100% sure how the constraint point converts a dbl in unsigned int, so it would be good to use a node of conversion and to probe this value, to ensure that you get the value you expect.

As for the second question, I told you that you should wiring in a contstant-1 in the field timeout of your fifo method on the RT VI and VI FPGA read.

Thank you

-

Two DMA FIFO fill and asynchronous playback?

Hello

I work lately on the Labview for my system which includes the acquisition of data from two sensors in FPGA vi and communicate to RT vi, where I treat the two sensor data and subtract. I am facing a problem of synchronization. I tried 4 data points, 2 of each sensor to each 25th microsec. Here I attach a pseudo-code that is just one of my original code that shows the same problem.

When we run the code, acquire US 4 data points each 25 microsecs in the FPGA vi and storing in the fifo DMA 2.

Then, I read this in RT vi and display them.

When I have a single loop in the FPGA and RT vi. the number of elements left in the two fifo should be identical, I perceive.

But in this case, it is not. Please enlighten me why?

Concerning

Intaris is right. How work DMA FIFO is that they fill a small pad on the FPGA, and when this buffer is almost full, the data is copied (automatically and at the bottom) of a larger buffer in the memory of the host. The remaining items is the amount of data is left in the buffer of the host. The automatic copy of the FPGA to the host will happen precisely at the same time to the two FIFOs, so you will get different amounts of data in each. The total number of items (between the pads FPGA and host) should be the same, although there is no way to see that, except for read all data (until the two buffers are empty) and confirm that the total number of items of reading was the same.

-

Hello

Let me describe the problem:

I have a FlexRIO (5751 + 7961) in a PXI system with a controller SMU - 8133 RT. (LabView 2011 SP1)

The 5751 writes each data of 100µs in a FIFO DMA and the RT controller he reads every 100µs.

But after reading in the RT controller several spikes occur as indicated on the attached figure.

The FPGA is also attached.

I tried a lot of things, I really think that the tips come from the DMA FIFO.

Can someone help me?

Your

Hello

Finally, we have found a solution!

I don't know why, but the problem was the FPGA VI. We did as it is done in the example of NI5751 oscilloscope with a state machine.

Maybe the IO need the Module e/s 0 clock to work.

Thanks in any case!

-

Hi people,

Is available on the FPGA FIFO DMA the only type of file transfer while transmitting data from FPGA to HOST? Most of the examples I've met DMA, so I used them blindly.

On a somewhat related topic, can a period be introduced in this transfer from FPGA to the HOST, without touching the concerned loop?

-

Number of items in the target to host DMA FIFO

Hello world

I would like to transfer a set of datapoints of an FPGA to a RT-host controller using a fifo DMA. If I use the 'Get number of items to write' function on the FPGA target, can I get the total number of items in the two buffers, or just one on the FPGA target?

(see http://zone.ni.com/reference/en-XX/help/371599H-01/lvfpgaconcepts/fpga_dma_how_it_works/)

markus_a wrote:

If I use the 'Get number of items to write' function on the FPGA target, can I get the total number of items in the two buffers, or just one on the FPGA target?

The FPGA will have no idea how big the DMA is on the side of the host. He can't see his own DMA buffer.

Get the number of items to write just tells you how many items are not used by the DMA (ie the number of items that currently write to the DMA without waiting for items to be offered by the host reading).

-

DMA FIFO of FPGA to host RT is full

I transfer data via DMA FIFO of FPGA to host RT.

DMA FIFO is full, I have tried everything I know:

-increases the size of the FIFO DMA up sideways FPGA

-set the depth of the FIFO DMA to 100000000

-increases the amount of DMA FIFO reading in each iteration of the loop

-use a timed with a frequency of 1 MHz, instead of a normal life all loop

Please find attached my project folder, FPGA code and code RT.

I solved my problem.

Below you will find my FPGA code before solving the problem and after resolution of the problem.

Solution: I just added a function of 5000 milliseconds (5 seconds) to wait before getting the analog input nodes samples (AI).

Before:

After:

Maybe you are looking for

-

Satellite M60 and the display driver installation

Help people to the display driver "installation cannot continue because the size of the specified directory path and the name of the installation folder exceeds 88 characters.Shorten one or both of the limit specified below and try again"! that to me

-

Toshiba 40TL900A: no connection to Toshiba Places

Hello I'm the Australia my model TV set is 40TL900A with the latest firmware. I have the same problems as the original since 13/01/2014 poster.I couldn't get past the Toshiba Places menu, it's just loading and loading with nothing happens.I updated t

-

How can I use a FireWire on Equium L350 adapter?

HelloMy laptop an Equium 350 has no ports to transfer video from a camcorder.There is only the Express card slot. Is there a way to get around this while I am able to use the i-link cable?

-

I have a CD of reinstallation of Microsoft; but does not have my product key to activate Windows.

Series of Microsoft Windows XP Home Edition 2002 SP3 I lost power when a transformer blew on my street. I'm short Windows XP Home Edition Series 2002 Microsoft. I DO NOT have the original version that has been installed on my computer when I bought t

-

SanDisk Ultra 32 GB class 6 (20 MB/s) SDHC Memory Card

Hello; The playback speed is about 18 MB/s, but the write speed of the peaks at about 7 MB/s using H2testw 1.4 in a card reader internal / writer (Windows 7 x 64, 12-core processor). Is this normal for this category of cards? Thank you.