FPGA read/write eeprom I2C

Someone at - it an example of LabVIEW for I2C communication to read/write an eeprom?

I use sbRIO-9636 with FPGA.

I already tried with the "Advanced I2C" example, but it works...

Can someone help me?

Another suggestion:

You know about the VI package manager? There, you can install an application open source I2C & SPI API (worms. 3.0.0.22). It is an easy way to implement a system of Bus I2C on an FPGA target.

In this way is a little bit smarter.

Maybe you like it.

Tags: NI Software

Similar Questions

-

FPGA read/write does not not in cRIO-9073

Hello.

I'm stuck with a problem in the use of the FPGA Read/Write control please suggest a solution.

I use cRIO 9073 and I'm trying to place an order ON / OFF of GUI-> RT-> FPGA host. I use a shared variable of the network to transmit the control GUI form to host RT and I use read/write control to FPGA. I also put a Boolean flag in the FPGA VI to control if the control is transferred to the FPGA.

When I toggle the button in the GUI, I see the same change in the host of RT (shown as 16 probe in attachment 1). However the FPGA indicator (indicated as probe 19) remains the default false state. The FPGA VI is on attachment 2.

Thank you

Guilhem

Your FPGA only reads the control once before entering the loop. If you want to read control permanently, you must put it inside the loop.

-

Frequency of calls to control for the FPGA read/write

Hello

I use a cRIO-9076 with a module NI 9476 DO spend some faucets. It is sometimes necessary for faucets with a pulse time down to a few ms of impulse.

The FPGA VI Gets the power tap queries, executes a logic of security, and routes the numerical results for the exits. It gets applications power of the VI on RT target that uses the function ' Read/write FPGA control' interaction programming of the FPGA VI front. The loop on the RT runs with 1 kHz, no iteration is missed. That means, it should be possible to switch the valves with a resolution of 1 ms.

What I see on an oscilloscope, is that the output digital are high for multiples of 50 ms, the system does not reach the valve for example 80 ms pulse or pulses shorter than Ms. 50 is a kind of limitation for calls of "FPGA read/write control"? I tried both options for arbitration, but it does not help.

The best knowledge of the limiting cRIO/module/features or ideas? Thank you in advance.

Karsten

Hi Karsten

You use any time in your FPGA VI?

It is useful to your code by sending as an attachment so that I can have a look.

Kind regards

-

In the target FPGA read/write control function?

Hi people,

I learn a lot from the sample project FPGA, including how you can easily retrieve and set controls and indicators in an FPGA using the read/write control function running in an RT target.

However, I can't find a way to do something similar in a FPGA target. I've been down this road before - that is, trying to move the data in/out a looping VI FPGA (void) to a (parent) FPGA VI - where my memory points to reach what I needed use.

So I was happy to see the palette FPGA enabled me to drop the control functions to read/write on a FPGA vi target. But alas there where tons of errors (not compatible son for target, etc.) and I guess now it's not possible.

So, just to be sure, I'm not missing something, is there something like control functions to read/write to use in an FPGA for read/write in an another FPGA (looped)?

In addition, why would I be able to read/write on a FPGA vi control functions if they are not supported? (Sorry for the n00b question)

Thank you

Steve

maherhome wrote:

You're right that I don't have this knot in my palette. However, I also do not seem to have a Refnum Occurrence in the palette is in the FPGA (see below), but I need to synchronize several loops of FPGA and added research using the textfield in the VI editor (and if compiles and runs). So 6 months to Labview and I'm fuzzy on how the palette is restricted

I don't know what you're trying to prove here. There is no control of refnum in search in your image. Occurrences are available in FPGA, and for control of refnum for one you just right click on a function of the instance and create a control. If you can create a valid thread of a certain type of data, then you can create a control or the indicator for it, regardless of the question to know if this type of control or indicator appears in the palettes. However, the functions that you can use in the block diagram are limited by what is available in the palettes.

maherhome wrote:

Regarding orders read/write for the FPGA/lights, I'm surprised that the infrastructure developed to allow read/write between RT and FPGA has not mobilized to allow read/write between FPGA and FPGA. The elements of memory function, but they are less convenient.

You may have noticed that you cannot compile the individual parts of an FPGA VI and combine them later; This is because when you compile an FPGA VI, all its subVIs are essentially merged to create a single block diagram (with additional logic if one not reentrant Subvi is used in multiple locations, this is why it is not recommended on FPGA). The subVIs no longer exist in the FPGA compiled; reading and writing a control on them would make no sense. If you want similar behavior, use global variables - but understand that global variables store values in FPGA logic resources. Using the elements of memory (or FIFO, which can also store in memory) leaves more fabric available FPGA logic by storing data in resources specially designed for this purpose.

-

Effective use of the FPGA read/write

I am writing an application for a CompactRIO real-time and I am looking for ways to simplify my code and reduce the CPU usage. I use FPGA to do much CAN e-mail and signal processing, then I have a VI running on the real-time processor that reads values in the FPGA, does some processing and outputs data in the FPGA. My code running on real-time parallel uses several loops running in a master/slave architecture. A single loop reads all necessary information in the FPGA in indicators and writes the values of the controls in the FPGA. The other loops read entries and manipulate the outputs via local variables.

My question if it would be more effective to get rid of the loop which is dedicated to the communication of FPGA and has of each loop to read and write directly on the FPGA. If I use a reference block FPGA open and use the reference of the output in several loops, each read/write operation block others until it's over? Each output is changed only in one place in the code, but there are several entries that are used by multiple loops. It is even more effective for each loop of read/write for the FPGA on request? How will this affect determinism?

Thank you

Jon

Jon,

Read/write controls is not deterministic, but I think that your previous method should work just fine, as long as you have that unique writers. If you have multiple writers, you start affected by race conditions.

I don't think you will see a significant improvement in the performance/CPU in the alternative method. You would see big performance gains if your master loop reads more slowly indeed, but it's always a compromise.

-

Control of read/write of FPGA Interface

I need help on control of FPGA read/write Interface. I would like to connect data TCP Read (String) directly to VI FPGA Read, but the entrance is an FXP... How can I do this?

Then change your FPGA control to be a byte (U8). On the side of your host, use the array of strings of bytes, then Index Array to get the specific byte you want to write on the FPGA.

-

The control law of read/write FPGA on the loop of the root / the UI thread?

Hi all

As the title suggests, the read/write control FPGA, https://zone.ni.com/reference/en-XX/help/371599H-01/lvfpgahost/readwrite_control/, is on the loop of the root / the UI thread?

Watch, https://zone.ni.com/reference/en-XX/help/371361J-01/lvconcepts/multitasking_in_labview/, this would indicate as that, but I would get a good response.

Kind regards

David

While I'm not 100% if it acts on the loop of the root / UI thread - calls to the FPGA (e.g. control of read/write operations FIFO) block permanently. I remember having a weird problem in the past where my FPGA operations have been suspended because I was expecting given FIFO elsewhere.

You should be able to test this easily enough - try to open a file dialog during playback of your FPGA. If playback crashes while the dialog is open, you have a loop of root problem.

-

How to add more variables to a read/write control?

See how the read/write control is connected to global variables? I want to add more variables, I created the globals (some are listed in the table above), but as you can see that they are not available in the read/write control. How can I add them? I also tried to create a new read/write control, but as you can see that didn't help.

Any help would be appreciated.

Hi count3r5tr1ke,

It seems that you are referencing a particular bitfile in open FPGA reference. I think that even when you save your FPGA VI, VI real time still referencing an older bitfile. Have you tried re - compile and referring to the new bitfile once finished compiling? A sure way to make sure that you have the most up-to-date bitfile is to check the VI option when you right-click on the FPGA Open reference and select Configure the reference open FPGA. When this option is checked, if you make changes to the FPGA code, it will force you to re - compile the FPGA VI before you reference it on the real-time side.

Best regards,

-

Read/write function reads a bad value?

HY,

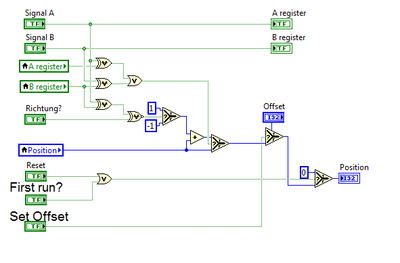

I'm using on my FPGA OR Quadrature encoder.

(http://www.ni.com/white-paper/6608/en/)

I add a few entries, so that its possible to set an offset value.

In all the VI on the FPGA, works very well with my encoder.

If I start the VI on my FPGA, the position value is 0, because of the "first round"? Element.

Now, I used the command of read/write in a while loop on my host VI to get the current value of the encoder.

After I start my host vi the defiler position always shows the value "2".

If I use the highlight function, the value remains at '0 '.

This is a really strange behavior, I don't know what can be the cause of this problem.

All positionsoffset values are 0 and encoders on my 9401 module entries are tied to the land.

The position value is only written on the fpga, nowhere else.

Anyone have any idea why?

Thank you very much.

-

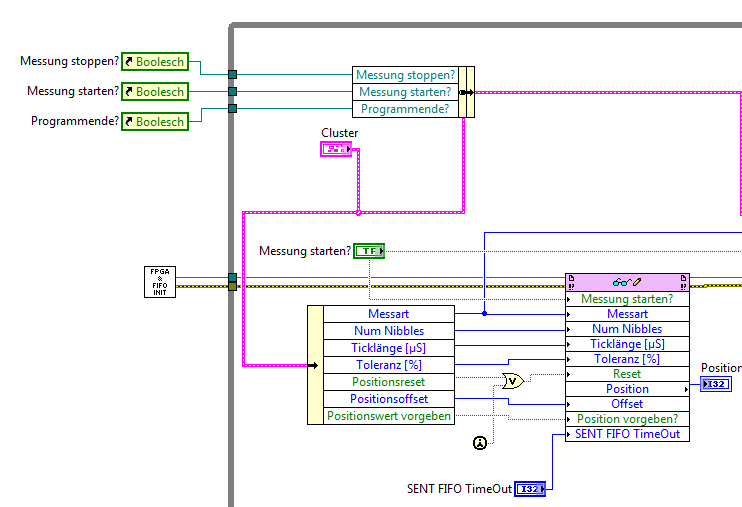

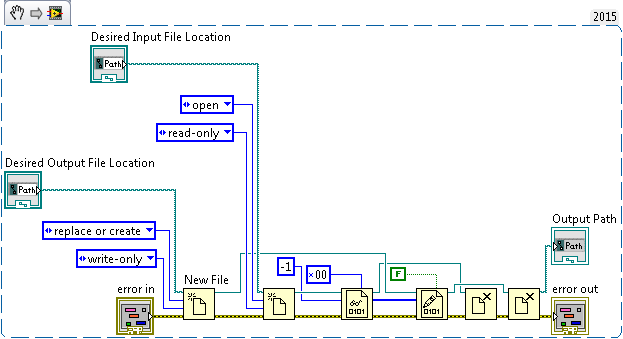

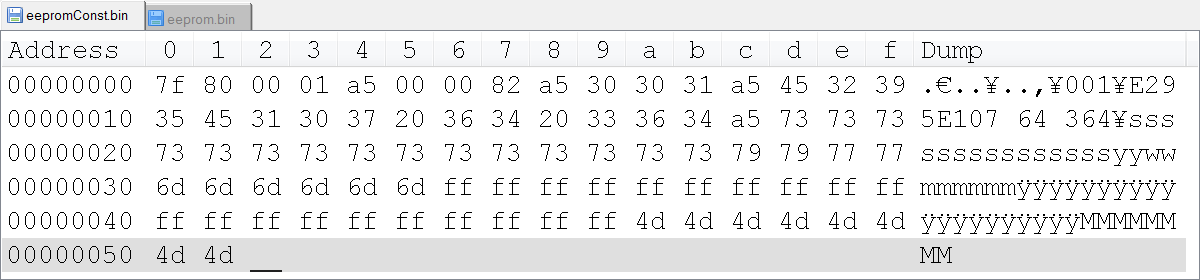

Read/write file binary change greater than 128 bytes.

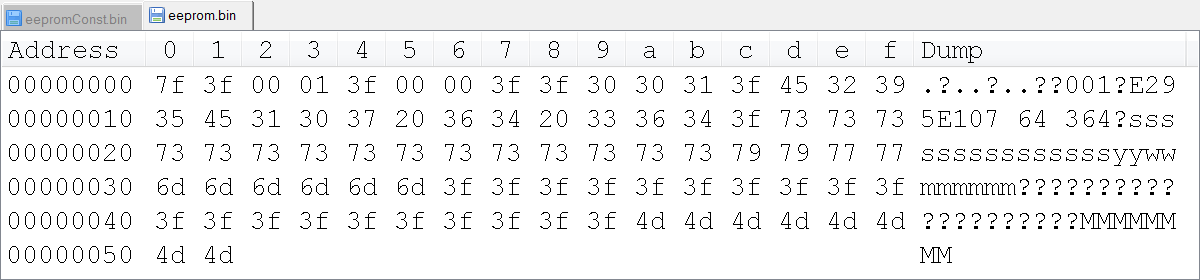

Hi all, maybe a strange question, but I'm scratching my head on this one. There is undocumented behavior in the function of read/write binary file, where U8 a value greater than 128/0 x 80 get automatically converted to 0x3F value?

I try to use LabVIEW to generate a binary file custom that we'll load in an EEPROM, so all data in the binary file is stored as values of U8. I have a "template" file, and eventually I'll take the logic implemented to replace the fields with the data from the true value. However, I am struck by the anomaly that when I just read the file in LabVIEW and then réécrirait, all the values 0x80 and more are truncated to 0x3F value. Has anyone seen this before, and is there a solution?

I noticed writing the value 0 x 80 directly to one generates a binary file (such as a U8) 0 x 90, 0 x 70 being written in the binary file. It is also rather undesirable, as it adds additional bytes in the bytestream, and the bytes of EEPROM must be in exact locations.

Join your data file.

This program is to give the images below? Are you sure that LabVIEW is to write the bytes differently? I really doubt that.

-

Help? the source volume is read-write and can not be disassembled...

I use 10.11.5 on an iMac 21.5 ", end of 2009 and I want to restore the OS X 10.11.5 to HD on an external drive but I get this message" Source volume is read = write and cannot be disassembled, so it cannot be copied from block. " I can find answers do not address El Capitan. Help would be greatly appreciated.

.. .Goldie

You use disk utility's restore feature?

If the HD has a recovery partition, you can make starting in place of the recovery.

Or you can use SuperDuper! (the basic version is free and can copy the entire disk, the paid version allows "smart updates", which copies only files that are different, saving time) running on externally to perform the copy.

-

Tecra A8 DVD don't read/write DVD-R 1-16 x.

Using Sonic Record DLA, Tecra A8 DVD don't read/write DVD-R 1-16 x. Ok work on DVD - R 1-8 x and CD DVD - R 1-16 x has tested successfully on the two recent Toshiba Satellite Pro and HP Office. Have updated the Bios, software DVD-RAM and Sonic DLA.

Hey,.

What exactly do you mean? This means that you can t burn DVD-r with 16 x speed?

In this case, you should check the specifications of your CD/DVD drive. Not all models support this speed of combustion. In addition, I recommend using 8 x only, he speed will give you a better quality of the burned data/average.You must also use different types of media. I believe that your other computers have different drives in order to test different mediums. I have a good experience with Verbatim DVD-R.

-

DVD recorder is not read/write discs DVD-RAM on Satellite A200-1GH

Hello!!

I have the problem as the topic - my DVD drive is not read/write DVD-RAM discs (recorder: HL-DT-ST DVDRAM GSA-T20N). Unfortunately, there is no any drivers (more recent than I've got) for this recorder on the Toshiba, not even site on LG or Microsoft. What should I do?

Greetings

Hello

To be honest, it's quite strange. If the laptop is preinstalled with recovery image, it should work. I tested it on my laptop 5 minutes ago and it works. The DVD-RAM disc is readable and different documents can be saved on the disk too.

Do you use your own installation of OS, or you still have some factory settings?

-

Carpet * a UJ-830 cannot read/write DVDs on Equium L10

Hi, I have a laptop Equium L10. My DVD RAM mast * a UJ 830 cannot read/write to DVD discs. But it can read and write CDs.

I have installed the latest driver but no luck. Any suggestion will be appreciated.This problem appears since day one?

I ask because it looks like a hardware malfunction, to me it seems that the lens can not calibrate properly and that's why the drive can read and write DVDs.

What burning software do you use?

For the most part a burning like Nero program provides an error message if the burning process failed -

Enter a share with read rights and have read/write rights

I have a folder with my photos on my Mac. In this folder, I have all my photos in subfolders and will add new pictures once I created the share. I want to make them accessible to my family there own PC/Mac. But only with READ ONLY. My problem is that a user (account to share on my Mac) with reading rights can access my shared with read/write rights.

I have my Mac with 10.11.2 the following users/groups:

- (Jens) My Admin account

- (Erika) Account sharing

- (Family) A group

Group of members of the family are:

- Jens

- Erika

My folder permissions to "/ Volumes/ExtHD/Bilder" are:

- Family: read

- Jens: Read/write

- everyone: read

I enabled file sharing in the system settings and the 'Pictures' folder added to the share list.

Now I go to another Mac with Yosemite, go to network in the Finder, select the computer with the share, connect to the "Erika" and open the folder "pictures". I can generate records or files, delete files, so I have read/write rights. Why?

Finder don't show me no option 'Erika' should have rights to write to this folder. Why is she able to delete files?

If get you information on the drive, it is the checkbox ignore verified property?

What is the format of the disc?

Maybe you are looking for

-

Yahoo page does not work. It seems that java does not work, but I have the latest version installed. Yahoo email page has all the links scrambled together on the left side of the page. Same thing with face book page. All use them to work properly. 64

-

I forgot the password for PRS-650

I seem to have forgotten the password for my PRS-650 4-digit. The reset switch does not work to reset the locking of the device. Any help would be greatly appreciated.

-

Win 10 d/l itself on our computer. All HP games have disappeared, and the boss is unhappy. Solutions? Win 10 can be easily uninstalled? Ron. Pavilion P6

-

Satellite L40-139 and WXP - how an audio device to work?

I recently reinstalled Windows XP on my laptop and after having managed to download the drivers for my wifi video ect I arrived to the sound I have downloaded the driver but it still does not that my laptop doesn't show any recorded audio device. How

-

DHCP server running Hyper-v comments

Original title: Hyper-V DHCP Hi all I'm having a problem with a DHCP server hyper-v guest. The DHCP server is seeing demand fall, assignment of an address to the pool, but the client pc never receives the details. Hyper-v host is 2012r2, the guest is