Control of read/write of FPGA Interface

I need help on control of FPGA read/write Interface. I would like to connect data TCP Read (String) directly to VI FPGA Read, but the entrance is an FXP... How can I do this?

Then change your FPGA control to be a byte (U8). On the side of your host, use the array of strings of bytes, then Index Array to get the specific byte you want to write on the FPGA.

Tags: NI Hardware

Similar Questions

-

The control law of read/write FPGA on the loop of the root / the UI thread?

Hi all

As the title suggests, the read/write control FPGA, https://zone.ni.com/reference/en-XX/help/371599H-01/lvfpgahost/readwrite_control/, is on the loop of the root / the UI thread?

Watch, https://zone.ni.com/reference/en-XX/help/371361J-01/lvconcepts/multitasking_in_labview/, this would indicate as that, but I would get a good response.

Kind regards

David

While I'm not 100% if it acts on the loop of the root / UI thread - calls to the FPGA (e.g. control of read/write operations FIFO) block permanently. I remember having a weird problem in the past where my FPGA operations have been suspended because I was expecting given FIFO elsewhere.

You should be able to test this easily enough - try to open a file dialog during playback of your FPGA. If playback crashes while the dialog is open, you have a loop of root problem.

-

In the target FPGA read/write control function?

Hi people,

I learn a lot from the sample project FPGA, including how you can easily retrieve and set controls and indicators in an FPGA using the read/write control function running in an RT target.

However, I can't find a way to do something similar in a FPGA target. I've been down this road before - that is, trying to move the data in/out a looping VI FPGA (void) to a (parent) FPGA VI - where my memory points to reach what I needed use.

So I was happy to see the palette FPGA enabled me to drop the control functions to read/write on a FPGA vi target. But alas there where tons of errors (not compatible son for target, etc.) and I guess now it's not possible.

So, just to be sure, I'm not missing something, is there something like control functions to read/write to use in an FPGA for read/write in an another FPGA (looped)?

In addition, why would I be able to read/write on a FPGA vi control functions if they are not supported? (Sorry for the n00b question)

Thank you

Steve

maherhome wrote:

You're right that I don't have this knot in my palette. However, I also do not seem to have a Refnum Occurrence in the palette is in the FPGA (see below), but I need to synchronize several loops of FPGA and added research using the textfield in the VI editor (and if compiles and runs). So 6 months to Labview and I'm fuzzy on how the palette is restricted

I don't know what you're trying to prove here. There is no control of refnum in search in your image. Occurrences are available in FPGA, and for control of refnum for one you just right click on a function of the instance and create a control. If you can create a valid thread of a certain type of data, then you can create a control or the indicator for it, regardless of the question to know if this type of control or indicator appears in the palettes. However, the functions that you can use in the block diagram are limited by what is available in the palettes.

maherhome wrote:

Regarding orders read/write for the FPGA/lights, I'm surprised that the infrastructure developed to allow read/write between RT and FPGA has not mobilized to allow read/write between FPGA and FPGA. The elements of memory function, but they are less convenient.

You may have noticed that you cannot compile the individual parts of an FPGA VI and combine them later; This is because when you compile an FPGA VI, all its subVIs are essentially merged to create a single block diagram (with additional logic if one not reentrant Subvi is used in multiple locations, this is why it is not recommended on FPGA). The subVIs no longer exist in the FPGA compiled; reading and writing a control on them would make no sense. If you want similar behavior, use global variables - but understand that global variables store values in FPGA logic resources. Using the elements of memory (or FIFO, which can also store in memory) leaves more fabric available FPGA logic by storing data in resources specially designed for this purpose.

-

Frequency of calls to control for the FPGA read/write

Hello

I use a cRIO-9076 with a module NI 9476 DO spend some faucets. It is sometimes necessary for faucets with a pulse time down to a few ms of impulse.

The FPGA VI Gets the power tap queries, executes a logic of security, and routes the numerical results for the exits. It gets applications power of the VI on RT target that uses the function ' Read/write FPGA control' interaction programming of the FPGA VI front. The loop on the RT runs with 1 kHz, no iteration is missed. That means, it should be possible to switch the valves with a resolution of 1 ms.

What I see on an oscilloscope, is that the output digital are high for multiples of 50 ms, the system does not reach the valve for example 80 ms pulse or pulses shorter than Ms. 50 is a kind of limitation for calls of "FPGA read/write control"? I tried both options for arbitration, but it does not help.

The best knowledge of the limiting cRIO/module/features or ideas? Thank you in advance.

Karsten

Hi Karsten

You use any time in your FPGA VI?

It is useful to your code by sending as an attachment so that I can have a look.

Kind regards

-

How to add more variables to a read/write control?

See how the read/write control is connected to global variables? I want to add more variables, I created the globals (some are listed in the table above), but as you can see that they are not available in the read/write control. How can I add them? I also tried to create a new read/write control, but as you can see that didn't help.

Any help would be appreciated.

Hi count3r5tr1ke,

It seems that you are referencing a particular bitfile in open FPGA reference. I think that even when you save your FPGA VI, VI real time still referencing an older bitfile. Have you tried re - compile and referring to the new bitfile once finished compiling? A sure way to make sure that you have the most up-to-date bitfile is to check the VI option when you right-click on the FPGA Open reference and select Configure the reference open FPGA. When this option is checked, if you make changes to the FPGA code, it will force you to re - compile the FPGA VI before you reference it on the real-time side.

Best regards,

-

FPGA read/write does not not in cRIO-9073

Hello.

I'm stuck with a problem in the use of the FPGA Read/Write control please suggest a solution.

I use cRIO 9073 and I'm trying to place an order ON / OFF of GUI-> RT-> FPGA host. I use a shared variable of the network to transmit the control GUI form to host RT and I use read/write control to FPGA. I also put a Boolean flag in the FPGA VI to control if the control is transferred to the FPGA.

When I toggle the button in the GUI, I see the same change in the host of RT (shown as 16 probe in attachment 1). However the FPGA indicator (indicated as probe 19) remains the default false state. The FPGA VI is on attachment 2.

Thank you

Guilhem

Your FPGA only reads the control once before entering the loop. If you want to read control permanently, you must put it inside the loop.

-

Effective use of the FPGA read/write

I am writing an application for a CompactRIO real-time and I am looking for ways to simplify my code and reduce the CPU usage. I use FPGA to do much CAN e-mail and signal processing, then I have a VI running on the real-time processor that reads values in the FPGA, does some processing and outputs data in the FPGA. My code running on real-time parallel uses several loops running in a master/slave architecture. A single loop reads all necessary information in the FPGA in indicators and writes the values of the controls in the FPGA. The other loops read entries and manipulate the outputs via local variables.

My question if it would be more effective to get rid of the loop which is dedicated to the communication of FPGA and has of each loop to read and write directly on the FPGA. If I use a reference block FPGA open and use the reference of the output in several loops, each read/write operation block others until it's over? Each output is changed only in one place in the code, but there are several entries that are used by multiple loops. It is even more effective for each loop of read/write for the FPGA on request? How will this affect determinism?

Thank you

Jon

Jon,

Read/write controls is not deterministic, but I think that your previous method should work just fine, as long as you have that unique writers. If you have multiple writers, you start affected by race conditions.

I don't think you will see a significant improvement in the performance/CPU in the alternative method. You would see big performance gains if your master loop reads more slowly indeed, but it's always a compromise.

-

Someone at - it an example of LabVIEW for I2C communication to read/write an eeprom?

I use sbRIO-9636 with FPGA.

I already tried with the "Advanced I2C" example, but it works...

Can someone help me?

Another suggestion:

You know about the VI package manager? There, you can install an application open source I2C & SPI API (worms. 3.0.0.22). It is an easy way to implement a system of Bus I2C on an FPGA target.

In this way is a little bit smarter.

Maybe you like it.

-

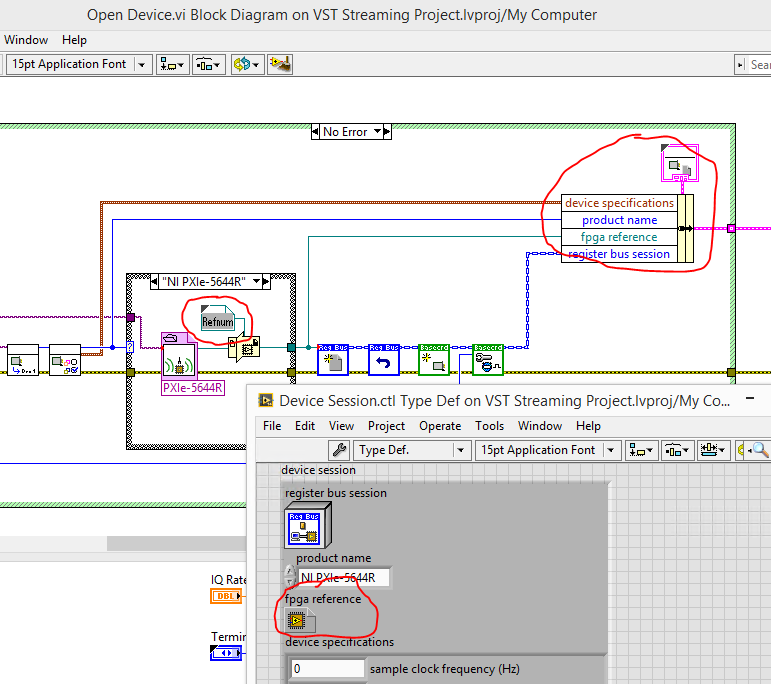

I play with a VST 5644 and model VST streaming. On the FPGA VI, I added the code, then added an indicator of the face before of the FPGA VI and compiled. Executes the FPGA VI in interactive execution mode, the indicator works well. Side host, however, I can't access the new indicator with read/write control.

Coming out of the open FPGA VI reference I can see the indicator on the wire, but in the Dynamic Cast of Interface FPGA function is have rooted out the refnum somehow. If I connect to control read/write directly to the output of the function of open reference I can access the indicator very well.

No idea what I am doing wrong?

Thank you.

You re-configured your FPGA VI reference with the new bitfile interface? The cast of dynamic interface defines the lead as all methods and indicators according to the type of wire connected. You can right click on the constant of type and select "Configure the FPGA VI... of reference". In the pop up window that follows, select "import of bitfile...". "and select the new bitfile you've built.

You must update the fpga reference type in the "Device Session.ctl" type def as well. This is the type that you will be able to access throughout the project.

-

Safe multithreading NI FPGA Interface C API?

Hello

I use the FPGA C API interface to communicate with the software labview on my FPGA OR. Some calls take a while to run, for example, reading on a FIFO so long timeout. So far, I assumed that the interface was not safe multithreading. It has now become annoying given the timeout problem described above. Try simply was not good, it can take a long time to create a "collison.

Is the FPGA interface safe multithreading C API? Or, more specifically, the functions of FIFO reading can be called in parallel with read/write variables on the FPGA?

Thank you.

Hello MKAP,.

It has been a while since I used the NI FPGA Interface C API, but it is what I remember and seem to be able to remember (and also found in the documentation):

Functions related to the unloading and loading of the library are not thread-safe:

http://zone.NI.com/reference/en-XX/help/372928D-01/CAPI/functions_required/

On itself, this should be a problem:

Your application should require that the NiFpga_Initialize is called before any other function associated with function calls NIFpga.

In a similar way that unloading (NiFpga_Initialize) lof NiFpga brary should occur only when you are finished using it.

With regard to multithreading, you must also keep in mind its mono-thread interrupts IRQ (if you plan to use them):

http://zone.NI.com/reference/en-XX/help/372928D-01/CAPI/functions_interrupt/

-

Sharing of Variables does not not under an FPGA interface?

Hi all

I have a controller 9074 cRIO 9074 chassis.

I defined a number of variables shared under my RIO controller and writing a UI VI in my host PC, where I feed some variables of network shared in RIO and get another return to RIO on the front panel of my host. Naturally, the VI which deals with read/write variable network data to IO channels real is under my RIO controller.

The problem is that, although everything seems to work fine when my RIO is set to the interface of the Scan Engine, the same screws give the following error message when I pass my RIO FPGA interface dependent.

-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

Possible reasons:

CompactRIO: (Hex 0xFFFF0000) unable to communicate with the module. Re-insert the module and check the connections. If the chassis is in Interface FPGA programming mode, make sure that you have opened a FPGA reference bitfile or VI FPGA with the load of the Interface of scanning for the module you are trying to access using the scanning Interface.

This error or warning occurred when writing the following shared Variable:

\\AMR-cRIO9074\B1-DO\JCV1_C1_B1

\\160.40.15.231\B1-DO\JCV1_C1_B1-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

Note that I get this error message for each channel of e/s that I call my RIO. Also note that it is there still no reference FPGA currently in any of the screws... I want to solve the problem is because later, I'll have to add some FPGA in my code, so I can not just impersonating my RIO scan interface...

Any help would be appreciated,

Harry

When you disable scanning on the cRIO platform engine, you must have some runing FPGA code.

There is noway that knows your controller on any module, and he can't read anything from any module.

If you do not have an FPGA vi, which sends the values of a port of the module on your controller, you need to do active Scan Engine.

The error message clearly indicate that you must have an open reference FPGA vi or analytical engine to be able to read the values of and to a module.

You are able to have custom analysis engine and a footstool of FPGA code at the same time on an FPGA.

Is there a reason you do not run with the scanning engine?

-

FPGA Interface C API, error-63105, OR-RIO: C/C++ identifier is already in use and cannot be created.

Hello

Installation program:

1 x the NI PCIe-7841R

When I am trying to automatically generate a C++ API for my top FPGA VI using the FPGA Interface C API 12.0 I get the following error.

Error-63105

NOR-RIO:

The "NiFpga_FPGATop_IndicatorBool_DMAFIFOtimeoutoccured" C/C++ identifier is already in use and cannot be created.

Anyone know what this means? Is there some kind of limitation on the appellation of front interface controls?

/Mola

Problem solved.

I had placed two flags with the same name on the front panel - by mistake. It builds the FPGA without errors, but the C API generator was not in favour of that.

/ Mola

-

under condition of read/write terminals on the side of the connector (basic training 3)

Hello

During my practice towards the review of the CLD, I examine the Core 3 online training material too. I just read a few tips of 'best practices' on the forum, for example this post:

It should be noted, that we should not use terminals (which are on the connector pane) to the inside of while loop or condition of the structure. Neither control, nor indicators (read/write terminals): "terminals conditionally read or written on the side of the connector are BAD!"

I can find many examples in the online training materials, when the indicators and controls are placed inside while loop and the case of structures in a Subvi.

I guess I should not do this during my review of the CLD, as they will run benchmark on my project? Should not be the core training materials updated some time? Or it's just not too important to have terminals on the outside? I would lose points during the CLD Exam my project as in the Core 3 screws?

example 1: Core 3, exercise 4-6 design of an error-handling strategy:

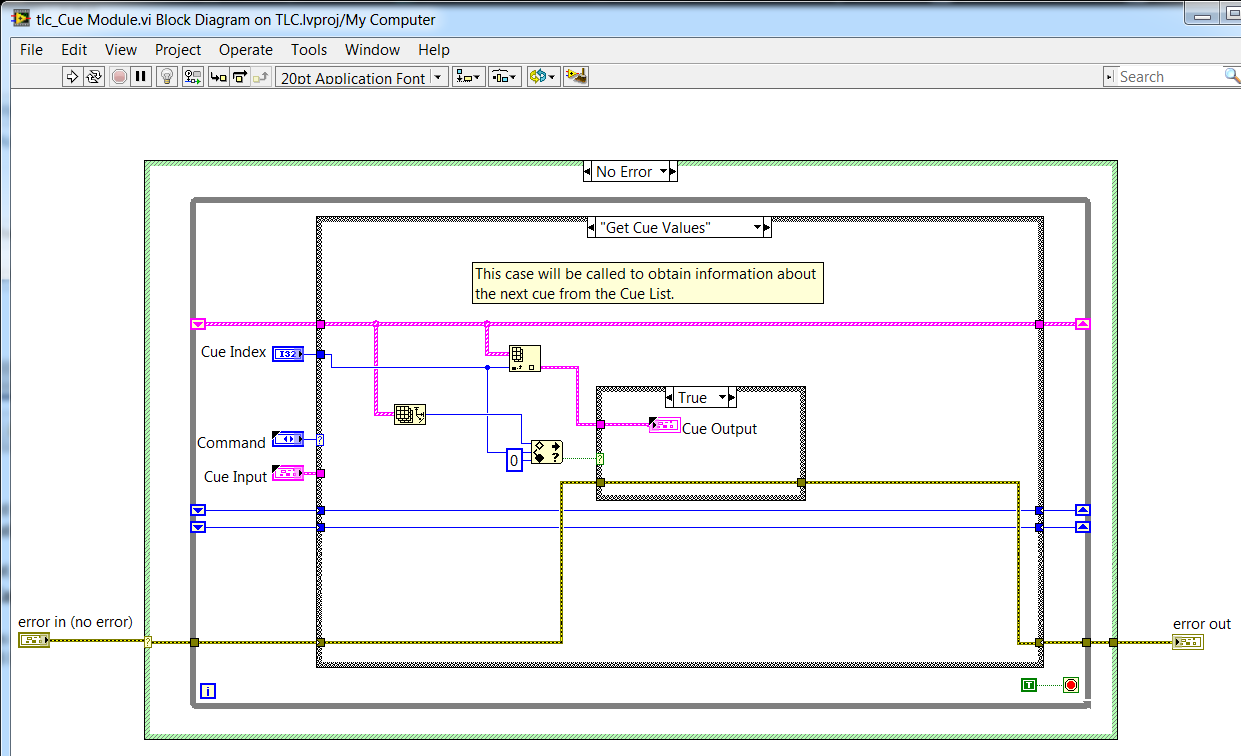

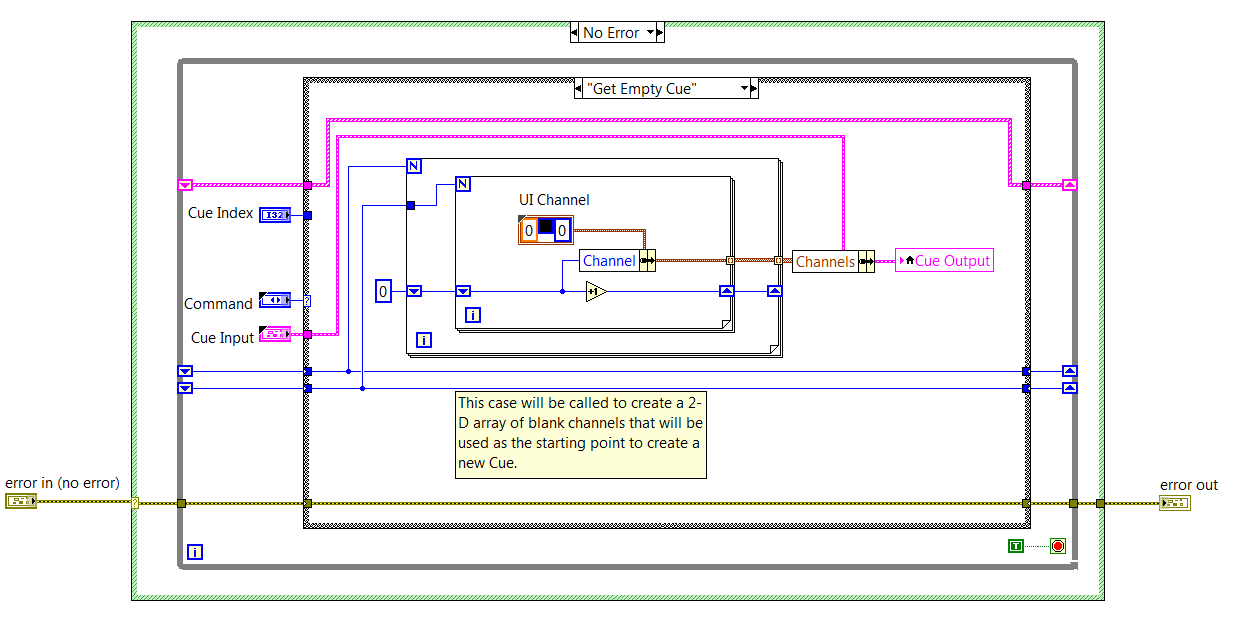

EDIT:

What's even more ugly in this project, is that, in the case of 'Get empty Cue', the Cue output indicator is updated via a local variable, because the indicator is not accessible via 'outside ': wire

Nice catch on the training material. that the application would take an if subject to a review of the CLD test graders.

As noted in the nugget: sentencing of perfomance for conditionally reached terminals is a function of the size of the data. So, it is sometimes acceptable for simple data. The larger point being to learn about compromise and make the right choice for your code.

Preping for the CLD on other means of hand knowing that VI Analyzer will run on your project. Like any other code review you walk in - know the guidelines for the review and code to ' review ' as well as 'reply spec.'

I've not seen an instance where an example of shipping (2013 and later versions) would fail this test VIA (there are a few screws deep inside the vi.lib which can date back to before the adoption of this recommendation from style)

-

Hello

I am writing a VI to control PWM with a microcontroller via a serial port. I wrote a simple code for the microcontroller that allows me to set the ratio of duty cycle on a scale of 0-65535. It works very well with Termite of Compuphase (RS-232 plug); The microcontroller invited me to an entry, expected that I would one, updates and expected another entry when I decided to send him. Now, I'm trying to get the same functionality on a LabVIEW vi but hit a snag.

When I tried to send my orders with a series read base and an example of writing, everything worked fine. I could see the prompt entry, write an entry and if I was quick enough, check out the update message. Even when I was not fast enough, I was able to check the update by monitoring the PWM pin with a Logic Analyzer. The problem with the basic example, however, is that I need to update the report to aura cyclical ratio, so I went for an example of reading continues writing. The problem I've met; is that I have to switch between reading and writing to make it work. When I do that, either I don't hold write it down long enough and nothing happens, or I get several updates when I switch to reading. Some of these updates don't even match and produce updates to defective upgrades for example; 16000 16000, 16000, 16000, 6000, 600, 60, 16000, 1600, 60, 0, 0, 0, 16000, 60, 0, 0 etc.

I tried which allows characters of endpoint in the hope that the writing would end at the end and go to reading where he would receive a termination character and wait for me allow writing once again, but nothing helped. I still have to alternate between the two and either get no response on reading several updates of variable accuracy. I tried to remove her allows read/write and their structures of matter in the hope that the loop flow, associated with the characters of endpoint would the case, but then the updates don't register at all. The funny thing is I did a VI like this before with an Arduino and that there not even no need to switch between writing and reading (I'm now using a Board of Freescale FRDM).

I was also the frequency of timeout errors; Error-1073807339 at VISA Read, reason Possible: VISA Hex 0xBFFF0015. I removed the option to stop the while loop if there is an error so I can run but always pops up an error on the judgment occasionally. Could the problem of synchronization always cause me problems?

Would appreciate all advice really, I am providing my slightly modified example screws and can provide the code for microcontroller on request, even if it's very simple.

Thanks in advance, it is

Yusif NurizadeIn other words, frankly, a good bad example you according to your code. Also, you have the order of writing and read upside down in your amendment if the instrument requires a command to return something. It should really be using a structure of the event. The structure of the event around a write and read and use a value change event. I have attached a quick change. This mod is still a reading after writing. If necessary, you may have two separate events to write and read.

-

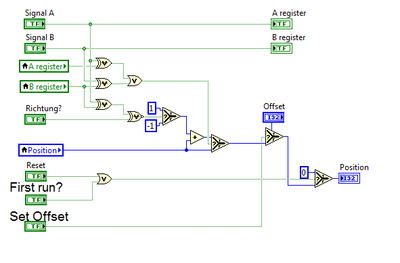

Read/write function reads a bad value?

HY,

I'm using on my FPGA OR Quadrature encoder.

(http://www.ni.com/white-paper/6608/en/)

I add a few entries, so that its possible to set an offset value.

In all the VI on the FPGA, works very well with my encoder.

If I start the VI on my FPGA, the position value is 0, because of the "first round"? Element.

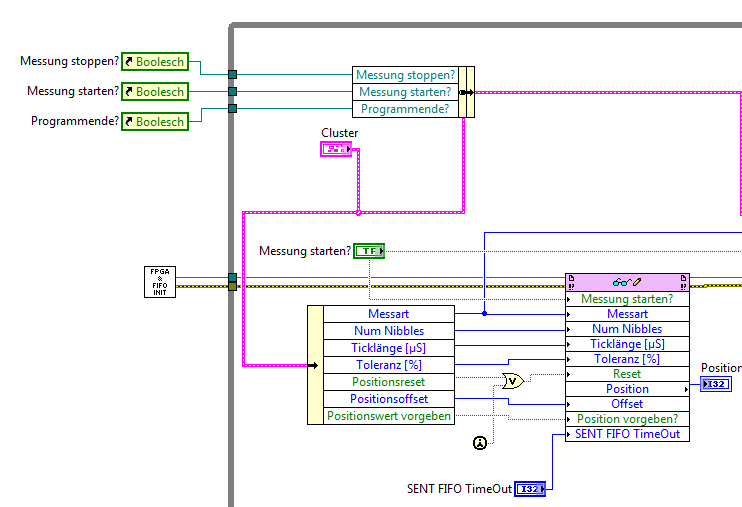

Now, I used the command of read/write in a while loop on my host VI to get the current value of the encoder.

After I start my host vi the defiler position always shows the value "2".

If I use the highlight function, the value remains at '0 '.

This is a really strange behavior, I don't know what can be the cause of this problem.

All positionsoffset values are 0 and encoders on my 9401 module entries are tied to the land.

The position value is only written on the fpga, nowhere else.

Anyone have any idea why?

Thank you very much.

Maybe you are looking for

-

I can't add a new contact on iPhone 6s

Recently got a new iPhone 6 s. I tried to add a new contact and phone number to my existing list. There seems to be no problem until I checked the list and the new contact was not there. I looked online and saw another way to do it, by dialing the ph

-

Hello. How can I make chain indicator scroll down to the bottom of the page using the block diagram? I some time that process loop data, whenever he finishes an iteration it will empty all the results in the string indicator. And I want to make su

-

How to get the external Bitmap of URL object

Hi all! I'm a developer starting with components of BlackBerry, I try to get a Bitmap of the outer objectURL, but my getImage method does not work correctly. I think that the problem lies in the getImage method. just at the moment where I try tocreat

-

To call the function in sql and script call

HelloI'll have a .sql script that returns the name of the partition and I need to run alter table Exchange partition something like thisget_part. SQLCOLUMN file_name new_value by sub_script_colaccept the start_date char prompt arguments ' input start

-

I had to buy a new computer. New computer is not the cd player. How to transfer the software to new computer?