JULABO RS232, FPGA, RT, FIFO

Hey there,

attempts to establish a connection to a Julabo F33 ME cryostat. I'm using cRIO9074 and module: NI 9870.

I got a model (FPGA.vi, RT.vi) of a colleague who runs his Circulator julabo on a similar system. Somehow, I can't return all of the controls on the device or get information.

RT.vi: I've amended the vi to send a command (String: in_sp_00) to the julabo (Mod1/Port1). I send you only empty strings to other ports because I just want to test one. It must respond to a temperature of these, but I can't get an answer.

I double checked the connections and settings for the COM port...

Find the screw in the attachment.

I hope someone can find mistakes.

Kind regards.

You can also include 'writing sub - VI'?

A common mistake with the serial communication is to forget to include the character of termination or line break after sending a string. The cooler waiting orders will end with a carriage return, linefeed, or both? If so, you must include in the chain that you send. Right click on the command string constant, choose "display codes"------"" and add to a carriage return ' \r' or '\n' for a line of flow at the end (or press just press enter at the end of the string constant to add a new line, that often works too).

Tags: NI Software

Similar Questions

-

for the FPGA fifo compilation error

Hello

I downloaded the example RS232 FPGA program and tried to make a small change to it. The original is like that; See attached file "beforeModification.PNG".

I wanted to reread the amount of data still in the FIFO where I had read everything so I changed it to that. See attached file "withModification.PNG".

The target is using the compiler 13.4 Xilinx 7841R. I'm not in the section summary with the following error message;

Details:

ERROR: HDLCompiler:1566 - "C:\NIFPGA\jobs\K7I4YEj_RQC5mWo\NiFpgaAG_FPGA_Main.vhd" line 869: Expression has 11 elements; official ocountfullcount wait 10I'm currently running;

LabView 2012 SP1 f3

12.1, the R Series multifunction RIO of NOR

I'm doing something wrong?

Thank you

Andy

The problem disappeared when I copied the source files in a different folder

-

Disable the extended FIFO FPGA target during execution

Hello

I use a FIFO extended target in my FPGA to constantly calculate the derivative of a measured value (dB/dt). Thus the FIFO stores all values during time dt. This means dt determines the number of items in the FIFO and dB is determined by the actual value less the oldest value in the FIFO. It works well when I initialize with the code in figure InitFIFO.

But the FIFO of compensation is not possible (see figure clearFIFO). In the while loop if "reset dB" is false, as the new value of B is written on the FIFO, then the oldest value is read from, for the number of items in the FIFO remain constant. To change dt during execution, I need to clear the FIFO and initialize it with a new length (number of items). I tried the next loop, but it does not work. The FIFO does not initilized with the elements. The length is zero and the loop counter for (#deltaB Length2) is 0.

What I am doing wrong? Is there a better way to erase a FIFO during execution in the FPGA? I'm now stuck for 2 days with this problem and looking forward to any idea or suggestion.

Thank you very much. Best regards

Andy

Hej,

Thank you for your response. You were correct, that deltab FIFO length was 0 because the defalt value was zero. The problem is that in my host vi on the RT system I put DeltaB FIFO length in a loop of high priority and as you can see when I restart the FPGA, DeltaB FIFO length has a valid value (the code in figure 1 works well with a local variable of DeltaB FIFO length in the FPGA). But the variable to set the variable "reset dB" is under the control of the loop of low priority of the host vi. And there, I had an entry DeltaB FIFO length unwired.

So, I learned that a control FPGA read/write unwired sends a '0' or resets the variable to its default value in the FPGA. I assumed that nothing is transferred and the last variable is retained if you let a control read/write unwired. Now, I learned of this stupid error!

Thanks a lot again!

Andy

-

Reach target FIFO / missing error methods

In my project, there are two FPGA vi and 4 pairs (reading and writing) of FIFO extended target that are used to pass data between the two vi.

A vi FPGA (named rs232.vi) writes the data it obtains from a port RS232 to READ FIFO; also, it reads data ENTRY FIFO and transmits to the ports.

The second vi FPGA (named griffin commands.vi) writes data to WRITE FIFOs and reads data from READ FIFOs. There is no other vi in the project.

When I try to run either of the vi, I get an error about missing methods to FIFOs. For example, when I run rs232.vi, I get an error requiring a reading memory FIFO so that the read method (see the image named side rs232) and who should write FIFOs have Scripture metod presend on the vi block diagram. However, these 'missing' methods are present in the second FPGA (as I described above). The same type of error appears when I run the second.vi.

Why the compiler can't see I have all the methods; However, they are in 2 separate vi? How can I avoid this error?

SophieJS wrote:

Why is - a VI is not the top level vi?

It would be nice too, as long as one of them call each other. I don't see in your screenshot, however.

-

Violation of FPGA Timing-> how to find?

Hello

I encountered a problem of violation of timing during my FPGA code compilation. Even if I change the options of compilation for "balanced" or anything else, the problem is still there.

My question now is, how do I find the function block in my code where the problem occurs? I use the SCTL several in my code.

Thanks in advance

Use the controls for the FPGA-host communications as long as you have enough of FPGA resources. It is recommended to use the communication between the host and FPGA DMA FIFO.

Only controls on the higher-level FPGA vi are accessible on the side of the host.

Global variables are used to communicate with an FPGA scope exclusively.

You use a device of sbRIO so I think the FPGA to communicate with the aim of RT (host)...

-

Accuracy of size for the FIFO DMA

I started to develop a code of RT for cRIO with DMA FIFO function application. A few questions have very fundemental

fluctuated around in my mind. The FIFO DMA is supposed to be made up of two components FPGA)

side & on the RT side).

1 the total THAT FIFO composed of FPGA side FIFO + RT side FIFO?

2. the FIFO of DMA size that I put inside the FPGA target in the Project Explorer refers to what just FPGA)

FIFO or Total size)? If it's just FPGA side FIFO, how big is the RT side FIFO together (is

It automatically assigned by RTOS free memory function)?

3. in addition, size defined programmatically by using DMA-configure is the equivalent of setting the size

in the Project Explorer?

4. Finally, how can I estimate the maximum size of the FIFO that I am allowed to use?

Thanks in advance for any response.

Hi Shiva419,

1. Yes, at least a DMA FIFO has these two sides

2. I just read in another reply that the size you set for the FIFO in the Project Explorer is the size of the FIFO on the side FPGA. The size of the FPGA on the side of the RT is much larger (default is 10000 items).

http://forums.NI.com/NI/board/message?board.ID=280&message.ID=5108&query.ID=99697#M5108

Mandar-

-

Cluster for the FPGA reference constraint

I have a cluster of clusters. One of the internal piles went 25-29 items, but I forgot to update several of my Subvi reflect. I remember before when I did, I got a broken line not executable VI, but now the result is a constraint. You can really force a cluster with multiple items to a cluster with fewer items? My outdoor group consists of some FPGA with clusters of register references.

Hi Adams,

FPGA reference is the special data of type "FPGA dynamic reference", which includes a cluster of records, elements, and associated with the referenced FPGA personality FIFO dynamically. Dynamic data types do not follow the same rules of coercion expected of them a defined data type statically to follow. The dynamic nature of reference FPGA son allow wire any FPGA reference in the entry of an order of read/write, regardless of whether the control of read/write was created explicility for the FPGA reference. This makes it much more practical FPGA programming.

-

Initialization of the DRAM in FPGA

To test my FPGA (FlexRIO 7966), I tried to test the error trapping. Generally, the error would be caused by an overflow in the FIFO of DMA process (EX: host VI is not reading fast enough causing the FPGA DMA fifo fill then causing my DRAM FIFOs to fill). When this happens, simply reload the bitfile does not seem to clear the condition. The memory is still in the complete state. Even restart the controller does not seem to clear the error. Electric bike does not work, but it's no possible to retrieve errors.

It is impossible to probe whose memory is in trouble, so I ask:

1. when the bitfile is loaded and running, the DMA FIFO is reset? What of the DRAM (configured as FIFO)? Or General FPGA FIFO memory (Blockram, registers, etc.)?

2. it would be of no use to manually clear the DRAM during the initialization of the FPGA (EX: switch from data_available to read in a SCTL initialization until data_available is set to false and ignore the actual data)?

File guides and aid users are very light on works the initialization of FPGA.

Thank you

xl600

-

FPGA acquires only the positive part of the signal

Hi all

I have the NI USB-7855R and using the personality of DAQ balanced example of e/s (http://www.ni.com/example/5961/en/). I plugged my generator Agilent to AI0 (in mode CSR) and I have the following problems:

(1) waveform graph in LabVIEW is only to show the positive part of the sine wave that I am providing to the Board of Directors (clipping at 0 V). Only by compensating the signal from the signal generator, I am able to get the two cycles.

(2) while I am out 5 Vpp on the generator of signals on the graph of a waveform in LabVIEW I see only 1.5 mVp.

Any suggestions on what could be the problem?

Thanks in advance or your help!

The first graph of "analog input" in your link shows the analog inputs are converted to unsigned integers (U32) before their passage in the FPGA-> host FIFO. Negative values will obviously be lost make this conversion.

-

How can I know what is the FIFO depth host side?

Hello.

In LabVIEW FPGA, the FIFO. Method to configure you determine FIFO depth host side.

If my screws have never included this method, is there a way to know how deep this FIFO has been all along?

I put my deep FIFO FPGA - side being of 8 k. How deep the FIFO by default host-side?

I ask because I have a few failures in my VI test that uses FIFO and I suspect that the excesses are to blame.

Thank you

AlejandroZ

Yes, it's always the default value 10 000. This can be verified with the FIFO. Write method and check the number of empty elements remaining, although this requires the FIFO be configured as host target.

For a target to the host, it is assumed by default to 10,000 without calling the FIFO. Configure the method, the only way I can think to test it is to loop FPGA VI writes in the FIFO and waits for a timeout, and then check the iteration count. It can be checked using the method of configuration and the depth reading, however it does not run the method.

In short, I believe that the default value is 10,000, although I'm not 100% sure for all cases. I checked 2 cases for my projects, using the write method and configures the depth using the reading.

Is it a fairly roundabout answer without committing?

-

UDP error 61 the cRIO - but the use of controller memory is < ~ 70%

Hi all

I'm having a problem with a program that runs on a cRIO-9074.

My controller code has 3 parallel processes (for the 3 banks in my controller) that each contain 3 while loops. Reads an array of FXP in a FPGA DMA FIFO values and pushes this table in a queue. The following loop then reads the table from the queue, it throws in a string, split that string in size of the UDP and puts these substrings in a second queue. The final loop reads a substring from the second queue and forwards via UDP.

Basically, a producer - consumer consumer/producer-architecture.

Now this works very well in my development version of spaghetti with just a first level vi code. To make things more readable even if I compacted things into subvis, using global variables when it is necessary to connect them.

My code is executed, but I get frequent errors during the broadcast channels UDP:

«UDP - 61 error: the system could not allocate required memory.»

I checked the memory usage from NOR distributed systems manager and my memory cRIO has a pretty decent amount of overhead. The sampling rate reduction - and corresponding memory use - does not make a big difference to the system time can go errors before. Even by reducing the sampling frequency straight down and disabbling that all except a loop (e.g. a Bank), I always get errors.

How I debug this?

-

VisualAnalog control with labview

Hi all

We bought an AD9643 that came with an FPGA based FIFO capture Board of Analog Devices, since they are just called VisualAnalog software to read the data and the control of the Board of CDA. Can I manage control this software under Labview?

We just need to make easy control as start, stop and get the data.

I tried the ActiveX method, but when I try to insert the ActiveX object, may not find all related objects.

Hey Martin,

I'm not particularly familiar with similar Visual but LabVIEW is usually good enough to communicate with third-party software. You said you tried to make calls through ActiveX (which was also my first try) and that doesn't seem to work. Below, I have included a link to an article that should be helpful when trying to interface with other software using LabVIEW.

http://zone.NI.com/DevZone/CDA/tut/p/ID/10060

Hope this Helps,

Doug B

-

Transmission of data to the host of RT to the FPGA via DMA FIFO

Hello

I try to write data from a host of RT on target FPGA using DMA FIFO and then process these data and read then return of the FPGA target to the host of the CR through an another DMA FIFO. I'm working on the NI SMU chassis 1062 q, with the built-in NI SMU-8130 RT controller and target FPGA NI SMU-7965R.

The problem I face is that I want to send three different tables, two of the same size and the third with different size, and I need one more small to be sent first to the FPGA. I tried to use encode dish with two executives in the FPGA VI. In the first image, I read and write the first table in a while loop which is finite (that is, a finite number of iterations). The second frame contains the process of reading and writing the second two tables (of the same size) in a while loop that can be finite or infinite (depending on a control). The problem is that it does not work. 2 arrays are displayed on the front panel of the RT VI host and works well, however, the table that should have been read in the first sequence does not appear on the front panel of the RT VI host. It is not sensible because if it is not passed from the host to the fpga and vice versa then the second image should not have been executed. Note that I'm wiring (-1) for the time-out period to block the while loop iterations until the passage of each item is completed. So the first while loop has only 3 iterations. Could someone help me undersdtand why this happens and how to fix this?

I enclose a picture of the host and the fpga vi.

Thank you.

If you vote for my idea here and it is implemented, you can even omit the loop FOR fully.

(I also propose the RE / IM divided inside the loop FOR and perform operations on complex table before the loop the transpose and reshape .) In this way, you only need one instance of these operations. You might even save some unnecessary allocations table in this way)

-

Element memory FPGA vs point FIFO

What is the difference between the use of a FPGA memory element (

) and an element of FIFO of FPGA (

)?

I am looking to unload data so quickly that possible between a host application and a target FPGA VI, but these two options seem to be sometimes used in the LabVIEW help documents and white papers. I understand the DMA from the computer point of view works and I would use this approach because it is the fastest (I need a very fast data acquisition system).

No one knows what what are the specific difference between these, and (especially), which will be quicker for entire U8 transfer data?

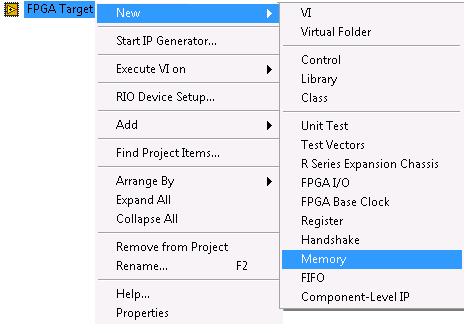

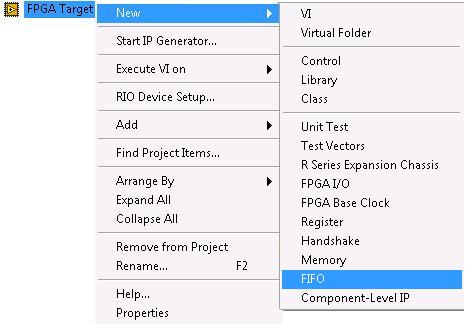

They are both created by click with the right button on the FPGA target:

Thanks in advance for any help!

To transfer data from the FPGA to the host, a FIFO DMA is your only option. Blocks are only to transfer data between the loops in the FPGA. A part of memory is not shared between the host and the FPGA.

A FIFO DMA is implemented by memory allocation on the FPGA and the facilitator. The DMA logic automatically moves data between them, but there are two distinct categories of memory, one on the host and the other on the FPGA.

For communication between the loops on the FPGA (without involving the host), the most important difference is a FIFO, as its name suggests, first-in-first-out, while a block of memory is addressable. There are also differences in how they can be used to transfer data between the different areas of the clock loops, as described in the help. If you have a question about a specific help section, please quote or link to the part you find confusing.

-

Sync in FPGA module between several FIFO

Hi all

I did a project in which I pass data with DMA FIFO for the FPGA and then return these values without treatment again to the host. I need to do in order, I mean, when the first FIFO is pass data to return DMA data, the others must wait all is to send to the host, then the second... so on. I did the path is in the picture, but does not work. With only a FIFO (first step in the project) worked right.

Is this the way to synchronize the FIFOs? Should be in a flat sequence all the loops instead of in separate dishes and no occurrences sequences?Thanks in advance.

Kind regards

Miguel.You actually create a dependence on the data with occurrences. A sequence structure must be completed before the next can even begin to run.

If you want that all FIFOs to browse together, why not just put them all inside the same loop? Then they will all play at the same time.

And what equipment do you use? A lot of material have only 3 DMA FIFOs. A lot of the newere who have 16 (which is what you use). Just worried about the problems of compilation here.

Maybe you are looking for

-

I have improved my storage and payment went on the wrong card. Is there a way I can change this? Or I have to cancel the upgrade and buy again using the right card?

-

How can I remove a picture background?

I need to remove the background of my photo in iPhoto so that I can convert it into an embroidery software so that I can take out. Any suggestions?

-

The Daily App Manager keeps print on my printer even if I never signed up for this. I want it to stop printing. Help, please

-

Pavilion 23-g013w: upgrade hp 23-g013w

I have a bad hard drive on this computer. I was going to rplace the hard drive and wanted to make it much faster... What is the best way to improve the system? This system is worth the upgrade? Any feed back would be useful. Thank you

-

Hello world I would use my software behavior of the boxes and I don't know how to do with LabWindows/CVI: I have a tree of options (the + symbol represents a check box): + opt1 - + opt1.1 - + opt1.2 If I Word * ONLY * the opt1.2 element, I want the o