Cluster for the FPGA reference constraint

I have a cluster of clusters. One of the internal piles went 25-29 items, but I forgot to update several of my Subvi reflect. I remember before when I did, I got a broken line not executable VI, but now the result is a constraint. You can really force a cluster with multiple items to a cluster with fewer items? My outdoor group consists of some FPGA with clusters of register references.

Hi Adams,

FPGA reference is the special data of type "FPGA dynamic reference", which includes a cluster of records, elements, and associated with the referenced FPGA personality FIFO dynamically. Dynamic data types do not follow the same rules of coercion expected of them a defined data type statically to follow. The dynamic nature of reference FPGA son allow wire any FPGA reference in the entry of an order of read/write, regardless of whether the control of read/write was created explicility for the FPGA reference. This makes it much more practical FPGA programming.

Tags: NI Software

Similar Questions

-

Impossible to check the FPGA reference with "not a number/path/Refnum?

How can I check if an FPGA interface refnum is valid? It seems (LabVIEW 2009) that "Not a number/path/Refnum?" always returns true when connected to the output of open FPGA VI reference. I write code that needs to be able to run without an FPGA for testing purposes, so I wrapped all calls to the FPGA in a case structure that I thought would run only if the FPGA reference is valid. Turns out that they run ever, even when the FPGA reference is valid (probe shows it has a numerical value, and the FPGA VI is running). I guess it's sort of similar to semaphore and appointment of references that have their own special function to verify the validity, but I do not see such a function for FPGA. I have to cast to int and check if it is not equal to zero?

-

No screws listed for option VI in 'configure the FPGA reference open '.

I have a cRIO and I used the function reference FPGA opened to load a bitfile by specifying the name of VI. It worked very well.

I've been compiling all day, and I just deleted a control and then changed to a DMA FIFO data type. When charge and ran the FIFO calls returned an error. So I tried refreshing the specification of VI, but now when the dialog box is displayed, there is no listed screws.

No idea what's not here.

(1) I put comment the FIFO when I compiled (forgot to turn it back on to the it); This is why the error occurred. Oops.

(2) I still don't know why I could not navigate to the VI, but I was able to drag and drop.

-

Frequency of calls to control for the FPGA read/write

Hello

I use a cRIO-9076 with a module NI 9476 DO spend some faucets. It is sometimes necessary for faucets with a pulse time down to a few ms of impulse.

The FPGA VI Gets the power tap queries, executes a logic of security, and routes the numerical results for the exits. It gets applications power of the VI on RT target that uses the function ' Read/write FPGA control' interaction programming of the FPGA VI front. The loop on the RT runs with 1 kHz, no iteration is missed. That means, it should be possible to switch the valves with a resolution of 1 ms.

What I see on an oscilloscope, is that the output digital are high for multiples of 50 ms, the system does not reach the valve for example 80 ms pulse or pulses shorter than Ms. 50 is a kind of limitation for calls of "FPGA read/write control"? I tried both options for arbitration, but it does not help.

The best knowledge of the limiting cRIO/module/features or ideas? Thank you in advance.

Karsten

Hi Karsten

You use any time in your FPGA VI?

It is useful to your code by sending as an attachment so that I can have a look.

Kind regards

-

What software OR do I need for the following references

Here is the list of the references that I have to solve for c# (visual studio 2010) project

I installed the developer NI 2010 costume that does not solve all of the people, but the installation itself took hours, now I'm going to try the studio measure 2013 which resolve some, but who has the wrong file version, I bit some older version, but we'll see how it works.

I'm still in the middle of configuration 13, waiting the feb13 DVD driver to finish downloading...

So what exactly should I get these? Especially DAQmx

My predecessor has not left me notes on this topic

notes in general, but that would be off topic...: manlol:

notes in general, but that would be off topic...: manlol:Thank you, in the meantime, I found the correct version.

I had to (find) and install the Developer costume 2012, it came with all the necessary libraries

-

Examples for the new reference value of data with LVOOP

Hello

I'm looking for examples on how to use the new function of data with the LV class reference to achieve access to the ByRef objects.

I would be very grateful for some codes.

Greetings

Hello

a reall call by reference is not possible in LabVIEW. A good method is to use a queue with the size of a single element - then you can always move the reference to the queue and to read and write the new items in there.

Or you use a FGV to store your object, which would work as well.

RMathews

-

generation of reports for the FPGA VI

Hello..

I want to include the number of resources used by FPGA (LUTs, slices, blockrams etc) in my report generation.

Time the build completed, a window showing these resources will occur. But, how can I add this report compilation in my generation of report...

Please let me know...

Thank you

Prashanth

Hi Julie

One idea would be to copy the data from the device file Utilization Summary in your report. See this KB for more information and an example of the layout of the file (which is quite complex, sorry) the path in the KB guess you LV FPGA 8.5, if you for example LV 2009 would be the path:

NIFPGA2009\srvrTmp\localhost\

\toplevel_gen_xst.log C:\. It must be remembered that this file only contains information on the latest compilation so you will only be able to get the info from this compilation, but that should be enough, if I understand your intent.

Best regards

David

NISW

-

Which cluster for the placement of DLR control VM?

Intend to have 3 groups for a design of the NSX - calculation, cluster management (Infrastructure) and Edge? Cluster Edge willl have GSE and controllers.

Who is the cluster recommended to place the DLR VM control, and what design considerations should be made?

Thank you

Ousmane

The implementation of cluster is pretty much arbitrary as long as you have sufficient resources and groups necessary distributed port. It would be wise to keep control of the DLR VM with the edges because it is a type of edge... Or it might be a good idea to move your DLR and the cluster in your cluster of right management controller, based on the logic function... that way the edge gateway data plane loads haveore has dedicated resources.

With the placement of the bunch, his main concern should be the availability of resources to workloads in the cluster. Secondarily, may give priority to the proximity of heavy workloads related? Other considerations are really just aesthetics.

It is perhaps a good idea to examine the way which you cut the clusters. What was your purpose behind this structure? Who is?

-

for the FPGA fifo compilation error

Hello

I downloaded the example RS232 FPGA program and tried to make a small change to it. The original is like that; See attached file "beforeModification.PNG".

I wanted to reread the amount of data still in the FIFO where I had read everything so I changed it to that. See attached file "withModification.PNG".

The target is using the compiler 13.4 Xilinx 7841R. I'm not in the section summary with the following error message;

Details:

ERROR: HDLCompiler:1566 - "C:\NIFPGA\jobs\K7I4YEj_RQC5mWo\NiFpgaAG_FPGA_Main.vhd" line 869: Expression has 11 elements; official ocountfullcount wait 10I'm currently running;

LabView 2012 SP1 f3

12.1, the R Series multifunction RIO of NOR

I'm doing something wrong?

Thank you

Andy

The problem disappeared when I copied the source files in a different folder

-

issue of timeout for the fpga 9870

I'm collecting series instrument (read-only) data, instrument using 115200 baud, 8 bits, no parity 1 stop and no control flow, none of which are configurable.

It works generally fine but sometimes it starting delay, by examining the properties of port, it says 0 bytes available there, but the instrument is always sending bytes. Disconnect the cable series and reconnecting gets it going again... But why?

I detect and recover with happiness (framing, etc) communication errors, but I can't get anything to recover from occurrence of timeout exception of physical intervention.

If I only connect the instrument and the start (forcing a real timeout) and plug in the unit, it will always be fortunately seems to start.

At this point, I would be 'reset' the port on a timeout, but I can't find a method/technique to do so.

It is a 9014 with 9114 chassis module 9870 (among others) and a labview 11 sp1

Eric416,

I had a 9870 running in a cRIO-9074 (scan mode) for some time now without any problems. I think I'd still try the isolator just to eliminate the posibility of equipment short. Then I hang a noculars on the TX/RX and see what kinds of things are spend on start-up/power. Have you tried to have your code close, then reopen the VISA session when the time-out occurs?

-

join query for the type of constraint and the type of the table column name

Hi, this is my request

Thank youselect table_name , column_name from user_cons_columns where table_name='EMP_CLASS' table_name column_name emp_class empno emp_class deptno select constraint_type,table_name from user_constraints where table_name='EMP_CLASS' constraint_type table_name p emp_class u emp_class I need query for this out put combining above two query. constraint_type column_name table_name p empno emp_class u deptno emp_class

Madam.Try this:

SQL> SELECT ac.table_name,ac.constraint_type,ac.constraint_name,acc.column_name,acc.position 2 FROM all_constraints ac, all_cons_columns acc 3 WHERE ac.table_name = acc.table_name 4 AND ac.constraint_name = acc.constraint_name 5 AND ac.table_name = 'TABLE_NAME' 6 / -

Use of FPGA references in a class

Hi all

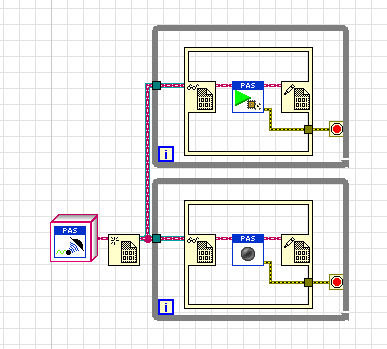

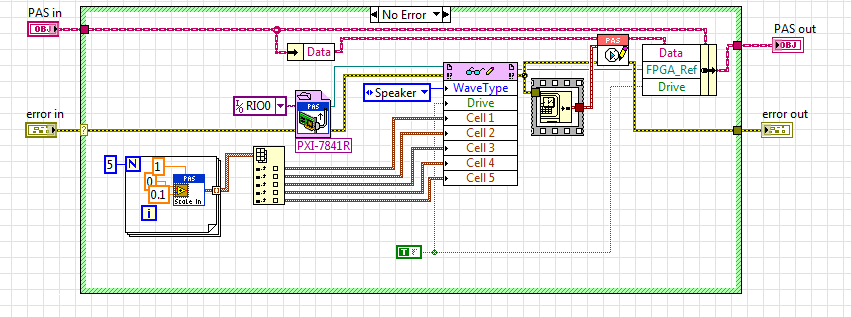

I found a work around for a question I had but it's not quite as elegant as I would like, so I thought I would post this question that I have. I am running a RT system on a PXI chassis. The system responds to commands from the user sent via TCP/IP. Much of the architecture is based on object-oriented techniques. In addition to the RT system, I have a card of the R series that I use for DIO and AO. For communication between the two loops (one that queries for the interaction with the user and the other that runs continuously measures), I use a data to encapsalate my main class reference. (simple example below)

In the main class, I maintain a reference to the FPGA session which I ungroup when necessary to change the settings on the FPGA. The reference is bound to strictly control type def' ed. I can manage to open the session for the FPGA (upper loop; vi below)

However, when I try to access the FPGA session open in the loop at the bottom, I get an error saying that the session is not open or is not valid.

I know it can be difficult to understand (I show the full set of screws, but they are large enough so those simplified should be enough), but someone has any ideas on this topic? I've linked the reference to a def of strict type for reference FPGA as for 2009, but I still get this error. Maybe there's something that I am missing?

Any thoughts would be much appreciated.

Peace, Matt

OK - I'm sorry. It works fine when group you in a class and use the reference data as described above. I came just to be able to close the reference where I expect it.

Peace, Matt

-

Open FPGA references change to no. target when compiled with executable in time real start

Hello again you useful forum fans! I have a problem that I hope someone can give me a hand with.

I have a project that has a Windows component and a component of the target in real time, that are running on a hypervisor type NI PXI-8110 system. Communication both sides between them using shared variables.

On the real-time side, I have four FPGA targets who are reading and writing various analog and discrete inputs and outputs. I several periods loops which opens a reference to one of the FPGA targets during the first call, then pass this reference in several subVIs that read and write to panels prior to the FPGA. The loops the FPGA reference thus made available and reuse it in the next iteration through the shift registers. Each FPGA target has only a single reference open to him. One of the loops is using the FPGA reference directly and does not pass it in any subVIs.

It all works very well in the development environment, I can read and control inputs and outputs FPGAS via the front panel of the application of the side Windows. It also works very well if I start the game real time in the development environment, and run the code of windows as a stand-alone executable file.

However, when I compile the code in real-time in an executable startup and deploy it to the target, it does not work. I enabled debugging on the executable, and when I connect to it via the operation-> debug executable in the menu, I see an arrow broken at execution. Further investigation shows that each of the four open screw reference FPGA is now empty, the text under them is "no target" and the thread for reference on their part to my first Subvi is broken. I need your help to understand how to operate as it does in the development environment.

I followed the instructions of these two knowledge base articles to compile and download the bitfiles FPGA on the FPGA target and execute on start or restart:

http://digital.NI.com/public.nsf/allkb/39795847AC67296D862575FB0046944F

http://digital.NI.com/public.nsf/allkb/BC513C2A0DC29C89862574BF0002B0B9?OpenDocument

Open FPGA reference screw are configured for the FPGA to build specifications that I created for each target in the LabVIEW FPGA project.

I called technical support, NO phone, and yet were able to determine this one out, so additional "brownie" points if you do!

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.Please let me know if you have any ideas regarding what is happening! I appreciate it.

Jon,

I'm always up for the challenge. Have you tryied recompile the FPGA VI that accesses the RT VI? I also suggest to try and open the bitfile instead of the FPGA VI. You run in dynamic mode (this is not a suggestion, it's just a question)? There is no difference if you try to open the FPGA VI reference outside the while loop, then past the reference to use inside the while loop without shift registers, then close the reference to the FPGA VI outside the while loop?

Let me know if these suggestions makes no difference.

-

Several loops of RT; A single FPGA reference

I have three loops using the same reference FPGA.

Loop 1 - reads most of the data in the FPGA for display on the HMI

Loop 2 - using the information made available to the loop 1 as well as some additional data that is read from the FPGA to perform the functions required by the HMI controls and writes for the FPGA.

Loop 3 - uses data from Loop1 as well as additional data read the FPGA to run commands fuctions and wrote security for the FPGA.

My questions are:

The FPGA Refence points to a single memory block where all three loops are looking at the same data?

I need on While loops shift registers to keep data updated correctly?

I need to run the three sons reference FPGA close While loops to close the reference correctly?

Yes. N ° N °

I assume you mean wire reference FPGA entering a node that reads the FPGA reference you speak or write in the Panel control or indicator that is part of the VI running on FPGA.

-

Good way to stop and run again a FPGA reference

Hi guys!

I have some problems when I try to stop, and then rerun an FPGA vi, I explain.

I have two DMA FIFO to send data to the FPGA of the CPU and the CPU for the FPGA. When it receives data, the FPGA treats them and sends them to the CPU, and according to the result of the CPU does something. For example, it can be turn on LEDs or to rotate a motor continuous.

But to do these actions, I have to use a "personality FPGA", i/o pins and LEDs appear to be managed by the FPGA core. So I have to close my reference vi FPGA in charge to receive data from the CPU, make my power on LED and then after raise again my FPGA VI once again, if I don't do LED blink or stay without effect rotation motor... But close and start again the FPGA VI creates problems when running, especially for the previous reading on the FIFO DMA awaiting... I tried to intercept errors on the FIFO to restart the FPGA VI with a good time but nothing... I am lost and I think Miss me something, concept, or something else.

I can't share my code because I work for a company, but I would like to know if you have VI with this type of structure: a FPGA reference that must be stopped to allow interaction of material with the FPGA default personality then run again, all with good timing...

I hope I'm clear, but if it is not the case, I can rephrase if necessary.

Thank you very much for the help!

Afghow.

I do not understand why you need to change the bit file is loaded in the FPGA. Why you cannot add code that handles the inputs/outputs to your FPGA processing? Why do you still need to send data to the host (CPU)? Just having the process FPGA data and change the output directly.

Maybe you are looking for

-

A week ago the screen began to play up At first there were the lines on the screen and then ghost images on all the objects on the screen After restarting several times the lines began to appear at startup from the bios, screen and they are still the

-

HP laptop HP Pavilion dv6-3007TU-XB823PA #ACJ

my friend brought Hp laptop HP Pavilion dv6-3007TU-XB823PA #ACJ yesterday. It comes with Free DOS. I tried to install WInXP on it, but I'm still looking for the driver. I don't even see the product described in the website of hp / is - this fake mode

-

Incompatible print cartridge error message

Below you can find a video on setting a cartridge print Incompatible error message in an Officejet J4680 printer. The steps it will show you how to do the following procedures. 1. Remove and inspect the cartridges 2. how to clean cartridges and what

-

BlackBerry Smartphones suddenly stopped to receive almost all the emails on 8830.

A lot of email this AM, then this afternoon, nothing. Messaging works. Phone works. I can even send a message from my computer to my BB, but nobody else can send messages. Cannot be re-sent service books because I don't remember my password. When

-

Help window popups in corelDRAW7

When I try to work on a CorelDRAW7 file, a popup Windows-Help ~ appears, which blocks my work. That the way it prevents actions, that I try to do in the time Evry program, it appears. It is frustrating that often. How can I STOP this @# $& the thi