LabVIEW timed loop

How can I set up a timed loop to run at the entry, rather than waiting for the first time in delta?

If my delta time is 10 seconds, I get my first run after 10 seconds. I would like to run the loop when he entered at the start (0 seconds) then wait every 10 seconds after that.

Thank you.

The first iteration of a loop, a loop's iteration 0. This will not change to the 1 iteration until the next iteration began. It is the expected behavior. Whatever it is inside the loop will run immediately but the iteration count increments until the next iteration begins.

Tags: NI Software

Similar Questions

-

What is error-1418 on a timed loop?

Someone at - he never had error - 1418 on the timed loop terminal error? It runs only once and I'm trying to run it on a cRIO-9004.

There is nothing in this range listed under the timed loop error codes.

http://zone.NI.com/reference/en-XX/help/371361F-01/lverror/timed_loop_error_codes/

As always, thank you

Jim

Hi Jim,.

I think that's what you're looking for:

Synchronization sources available for LabVIEW timed loop by platform

Kristen H.

-

Hello

I would like to create a FPGA loop that runs at a fixed rate. Whatever if I use a timed loop structure or a timer loop express VI into a regular while loop? Under what circumstances should I choose one over the other?

I understand that the timer loop approach can cause the code in the loop run twice before calendar is established (but this isn't a problem for me here). Are there other differences in the two approaches?

Thanks in advance.

JKSH wrote:

But my question was about the differences between the use of "multi-cycle" Timed loops and VI express loop timer.

In a targeted FPGA VI, all call loops are single cycle timed loops (SCTL). This means that all the code in a SCTL must run in a clock cycle, so there are a few types of nodes cannot be used in such a loop. In a used while loop with a timer, you can use a wider range of features, but the loop will generally run much more slowly.

These documents may be useful to learn how to use loops clocked on FPGA:

Using loops of Cycle time unique to optimize the FPGA VIs

Optimization of your screws of LabVIEW FPGA: running in parallel and Pipelining

-

Operating system: Windows XP

Hardware: PCI 6259

Terminals used: PFI0 and PFI2

Counters used: Ctr0 and Ctr1

IM developing an application for the acquisition of data where timed loop synchronization source comes from my PFI2 (using the string A of an encoder). IM basically trying to acquire data based on the number of ticks from my encoder. For the synchronization source, I use counter 1 to capture the rising edge and have the loop time-acquisition of data. At the same time, Im using the counter 0 to count the number of rising edges so I know exactly in what tick data was acquired. PFI0 and PFI2 are connect to channel A of the encoder.

Questions:

Timed loop acquires data at each tick, because when I discover the data (text) file is missing count of my encoder value. Is it because there is a limitation on the Windows operating system? I used a noculars to measure the frequency at the maximum rotation of the channel encoder and 6,757 kHz. All solutions?

Also, is there anyway I can route the source channel internally an encoder to generate synchronization source instead of using another counter? I have attached my VI.

Hello

All the samples that you acquire will be read by LabVIEW in a sequential manner. Figure 4-21 on the M-series on page 80 (4-34) shows that you will acquire all the samples you request all channels that you enjoy in sequentially.

-

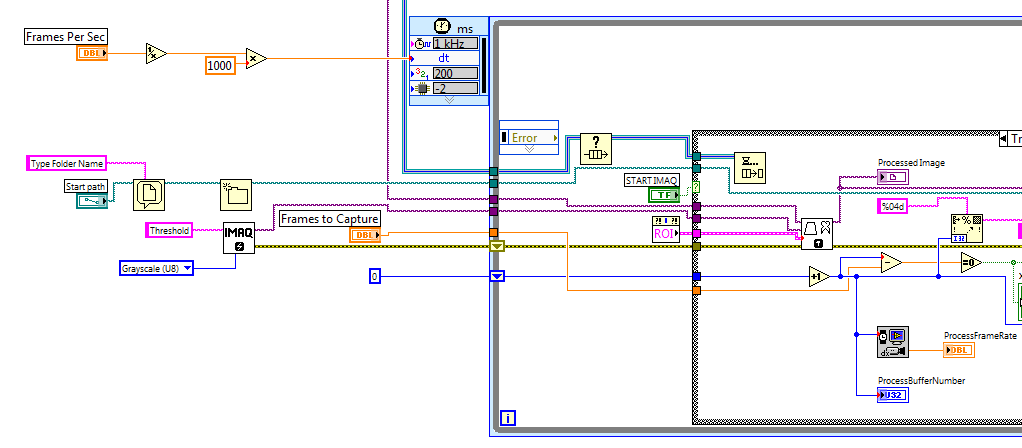

Timed loop in loop of producer/consumer

Hello!

I have a loop of producer/consumer LabVIEW program configuration to allow me to properly capture the images that are large enough (8MP) at about 14 frames per second (FPS). The program works very well when the consumer loop is a while 'loop' (recorded at 14fps without problem), but I wanted to do a loop timed, so that I can vary the FPS as requires it. A curiosity arises when I do that. Anywhere under 12 fps, the loop works very well and the data is saved correctly. However, when I bump it up to 13fps, the calculated consumer FPS goes haywire and starts to jump between 9 ~ and ~ 13fps (processing of data gets bogged down?). When I set the FPS at 14, the loop runs at a constant maximum 7 fps. Is there something I can do to remedy this situation?

I have attached my .VI

Thanks in advance!

Palanski,

Are you using LabVIEW Real-time? Loops clocked to a windows OS do really increase determinism more than a while loop with a wait until the next timer multiple. Before you change the loop of producer-consumer in order to include a while loop was programming works correctly? You can also vUtiliser the VI analyizer to see how long things take to run. I let the loop of consumer to the producer in the traditional game upward and change the FPS by controlling the timer to wait, after benchmarking your code, it should be done in the same way as you did for the timed loop

-

While why broken arrow will not appear for a timed loop

Hi all

I need a little clarification relative to normal while loop and timed looping in labview.

In labview, if I keep a while loop on a block diagram, broken arrow will appear in the upper left corner of the window indicating the error. It displays error because I have not wired conditional terminal of the while loop.

But same is not the case for a timed loop. Can someone tell me what is the reason behind this...

If I release the conditional terminal of the timed while loop, it runs in infinfite time like a normal while loop. Then y labview behaves differently for these two types of loops in the scenario above.

FYI... I'm using labview 2009.

Waiting for response.

Thank you

Herald

Ruben,

the reason is quite simple: call loops are mostly real-time and FPGA targets. Since most of the applications on these targets work continuously (at least this is more often the task), it is possible to create a loop that does not end. So the timed loop by default assumes that there is no need of a stop button.

The 'normal' while loop needs code for termination (conditional terminal) because normal applications on Windows/Linux/Mac are used to be fair...

hope this helps,

Norbert

-

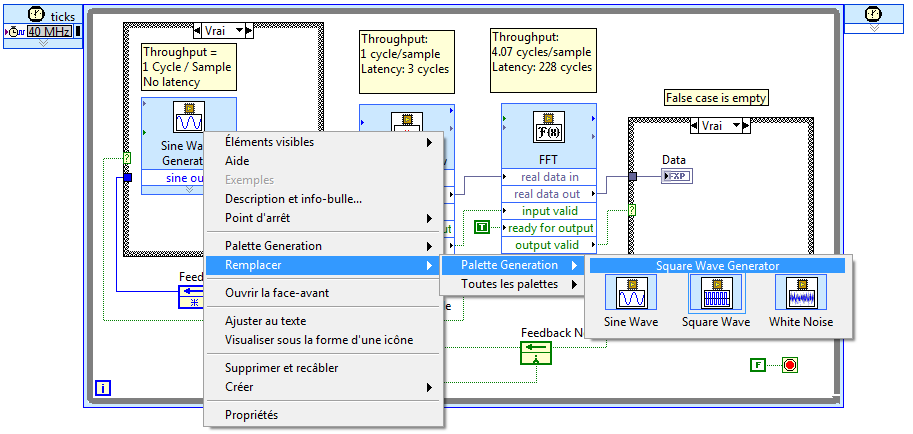

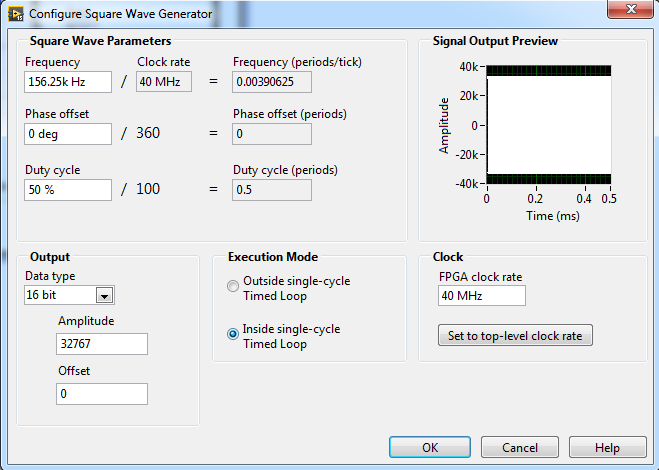

FPGA 2012 training: exercise fails '4-Wire Protocol' 7-2: not supported in single-cycle Timed loop

I work through the training courses OR 2012-FPGA with Labview 2014 SP1. I find the solution provided to exercise 7-2 called '4 son Protocol.lvproj' does not work. He is unable to run with the message "LabVIEW FPGA has reported the following error: item (s) not supported in single-cycle timed loop.»

Should it? I thought that the examples in the solutions folder were supposed to work such as provided. What needs to be fixed for this work? Thanks for any help.

Hello jbeale1,

It is a known problem. Here is the comment of NEITHER:

---------------

Exercise no. 7-2: 4 - Wire Protocol [Allen Hsu 2013.8.19]

- Description of the problem: exercise 7-2 uses a sine wave generator inside a SCTL VI. In 2012, LV, this VI is not supported in the SCTL, but LV 2012 will allow you to use mode 'simulation' (run on the dev machine). However, LabVIEW 2013 not even lets you use this VI in "simulation" mode If you run the VI with the sinusoidal generator inside a SCTL VI, LabVIEW 2013 gives you a "or objects not supported in single-cycle timed loop.

- Solution: If the students use LabVIEW 2013, you must tell the students to replace the sinusoidal generator inside the SCTL pre-built exercise VI VI with a Square Wave generator VI with the option "inside the SCTL" enabled in its configuration window, as shown below:

--------------

To replace the "sine wave generator" right-click on it and select the 'Square Wave Generator'. Then you have to double click on the "Square Wave Generator" and select "inside the only cycle timed Loop". You should then be able to run the example.

-

Most of the machine control software I design have the following structure:

1. There's a HAND that takes place inside a TIMED LOOP with synchronization of 50ms and priority of 100. His only job is to read / write data from / to DAQMx IO cards.

2. the MAJOR can call several SUBs based on the choice of the user, and once a submarine is called FP MAIN is closed and the FP SUB opens. All submarines have a States Queued Machine running within a TIMED LOOP with 50ms timing but with priority to 50.

3. data transfer between HAND / SUB is through function globals - there are many of them based on past data.

4. all woks fine so far. No need to any RTOS. and platform of WIN7 is alomost standard. I even ran with a timing of 20ms without anything crashing...

Problem: When there are a lot of file i/o operations in a SUB partciluar, then I have the chance to see several missed iterations. Perhaps the TIMED LOOP is hogging resources.

What I want to do: convert both TIMED in asnd SUB HAND loops simple while loops. But I am concerned by the priority - since the MAIN interacts with HW there priority. But with LOOP WHILE how can I ensure this?

Or is there any replacement / effective way of doing what I do now?

Rama wrote:

.... FGV should be thrown out the window...

Well used for a while, based on many articles in the KB. One of them is locked... and it does not represent the engine of the Action or of the FGV as a villain to avoid.

The driving force is one of the largest buildings in LabVIEW. The FGV who does nothing but Get and Set (or writing and reading) is useless and a waste of resources. Why? It does nothing to fix possible race conditions (does not protect critical sections) and it is much slower than just using a global variable. See this example I put in place to see what I mean: an overview of the race Conditions.

Rama wrote:

So in the sample that I had attached, what do you think would happen if I just replaced the two loops with the SAME timed in MAIN and SUB wait value ms. is there a work order then?

When things are at the same time, there is no such thing as the order of execution. But as I said, it seems that your loop is quite slow, so it's something I would not worry. Just make sure that you do not have a loop that uses all the CPU.

-

Why extend a timed loop always expands diagram in the same direction?

I just noticed a behavior of wiring diagram in LabVIEW 9 I love not really for. I have several parallel call loops on my diagram and want to do a little to add code in their breast. When I drag one of the other side to expand it, my whole wiring diagram expands to accommodate the drag. However, when I am developing one of the others in the newly created space, she AGAIN extend my digraph together in the same direction. Why do what there already is plenty of space to expand to created by the first operation "click and drag". This problem can be avoided? If so, how?

Bill

Ah, the forum of OR is a source of deep wisdom and knowledge

Please read this thread for a solution.

BTW. you don't need programming/reset this option each time if you want to only timed loops to have this disabled. You can set this option by the structure after a fall by using the context menu.

Norbert

-

Timed loop first iteration to fast

A timed loop is used to create a calendar suitable for data acquisition. The structure has been tested with a period of 1 000 ms and each loop takes 1 000 ms except the first flowing through the ms. a little my expectation was of course ms 1 000 the same for the first loop. I need the measures to be equally separated in time from the very first point. How to solve this? Is there information on the behavior of NEITHER?

Windows XP.

LabVIEW 2010.

Hasun,

try to use the shift / timing settings phase timed loop.with 1000ms.

-

passing the value and to timed loop

Hello everyone,

I'm working on a VI that consists of a timed loop which takes values in a file every 6 ms and writes it to an output file. Inside this timed loop, there is also a MATLAB block that calculates a parameter based on the value. based on this parameter, that a marker is set to 0 or 1 (planned) to operate as a Boolean marker.

The problem arises when the marker is set to 1. I need an additional structure any that waits five seconds (without stopping the timed loop iterations) and a 'stop' button is not pressed an additional string is placed in the output file. I wish for the marker to get back to 0 if you press the 'stop' button and not string to put in the file.

The main problem seems to be the use of a structure outside the timed loop. I can't have a while loop or any structure that waits 5 seconds inside the timed loop. And if I let him out he does not have the value of the marker second structure during execution of the timed loop.

+ Any ideas on what the structure to be used during the 5 seconds Timeout? (I tried a while loop)

+ Use a local or global variable for the marker? (I tried briefly, but as a local variable, I couldn't choose a variable defined in the MATLAB block, and I don't understand global variables in LabVIEW)I enclose a simplified version of the VI as well as a sample input file in case it can help visualize.

Thank you

DAVASo far, there are a few problems with your solution, but first of all, I will try to help answer your original question.

You are right that you can't have a structure inside the timed loop which waits five seconds without blocking execution of the timed for the same period. You are also right that you cannot simply communicate through cables to an external structure. If you exit a loop of wire in the other, which creates a dependency of data flow, which means that the data loop cannot run at all until another loop ends its execution entirely and send data.

You have two options:

- Don't actually use a wait function to determine if the 5 seconds elapsed. Use the Express VI of time elapsed (search the palette). He just guard track of how much time has passed since the last reset. It does not wait. If you are safe to use inside your loop timed in a case that is triggered when the marker value becomes 1. Also check the Boolean command in this case Structure to decide if you should output the data in the file.

- Use an outer loop as in the example you posted, but use screws of the range of synchronization to send data between the parallel loop. Consider a queue.

But overall, I don't think there is much chance of this work very well. No way, the Matlab Script node running fast enough to run at a time of 6ms. Also no way it works in a deterministic way at all. He needs to communicate with an external program, so its execution time is really unlimited.

-

Timed loop continues to turn after stop

Only, I have seen this time, but thought I should ask about it. After pressing the stop button, I was surprised that the diagnostic LED on the front panel of the main vi kept flashing. With the performance highlighting ONE values showed that the timed loop was still running. I checked the other 8 loops clocked subvis and they also ran. None of the methods Stop worked. Only stop LV and abandonment of the cRIO eliminated the problem.

Run LV2014 SP1 on cRIO-9067 with dual-core ARM processor. Windows 7 x 32.

BTW: The function of the check LED VI scale does not work on this device.

You must allow an order any to be able to stop your curls. A simple global variable would work well here.

-

In the attached VI, I put the loop timed to end once the delay 1 reaches zero. However the timed loop continues to run and stop only if I have OR both 1 and 2 delay delay. (Tried with different schedules for late 2 which are less lag 1, equal to 1 delay and more delay 1 - no chance unless it is also linked to stop)

What is the reason for this? (The VI is in LV2012)

And it is protected by word that prevents us from looking into it.

Is this your VI or did you also?

Subvi properties seem to show that it is not reentrant. Otherwise it can only run one instance at a time. And if happens to store data to leave once it is called to another in the uninitialized shift, running an instance registers is probably interfering with the execution of the other instance.

-

Structure of the event in timed loop

Quick question on the structures of timed loops\event

What is a good or a bad idea to use structures of event call loops - as opposed to while loops. ? I guess I like the idea of call loops - because you can prioritize them - so if there are some important things you need priority of 100% in the background - but for the user interface, you can configure it to run slower\or run to a different priority level.

I just wanted to check it is not a reason why I shouldn't do that - since all the examples don't do that.

JP

I don't think it's a good idea. Your timed loop can stop waiting for an event. There is no advantage of placing the structure of the event in a timed loop. It is possible to assign priorities to other objects outside of the call loops. For example, you can the priorities given to subVIs. I'm reasonably sure that the structure of the event can work at other priorities if you do not the activities of the user interface. Maybe someone of NOR can confirm this.

But the goal of a timed loop is to have a deterministic periodic job. The structure of the event must be used for asynchronous events. The two disagree with them if they are in the same spot.

-

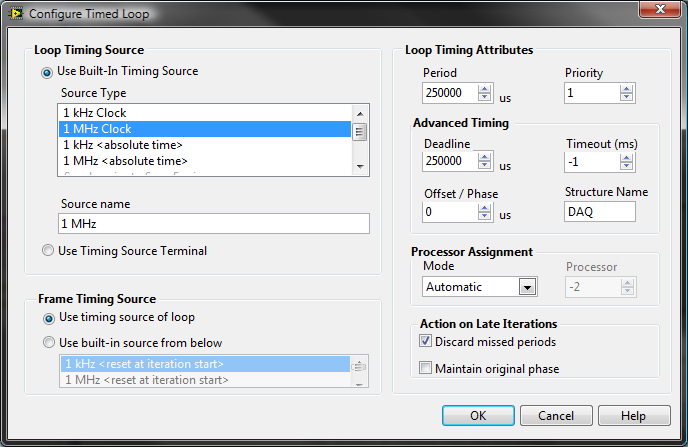

In the timed loop, the entry node was a... of entry... that called "Source name" and says that I can specify the name of the source of synchronization. What this means and how can I do? How is it when I put a constant with the same name as the name of the default Source (create > constant > "1 kHz") the loop runs only x times then stops on its own. Yet when I leave the value by default as is the loop runs until I hit the stop button?

Hi Clint,.

Yes, the moment Source.vi create will serve in the same vi. There is actually no difference between the vi and the options on the node of the loop. However the calendar source.vi creation will be used if you want to programmatically select the synchronization source.

You will find information on the configuration of the source of synchronization in the detailed help, a link to which lie at the bottom of the window context help:

"Double-click the node entry or with the right button of the structure and select Configure the timed loop to display the Configure the timed loop dialog box, where you can configure the timed loop. The values you enter in the dialog box Configure the timed loop appear next to the input on the entry node terminals. »

Thank you

Maybe you are looking for

-

Trails of the icon when switching between desktops in the Sierra

I noticed some display problems since the update for Sierra. I see some trails icon when switching between desktop computers as well as a line of 1px of random colors on the right side of the screen seems to be leftover pixels for the desktop switch

-

Equium P200D - Vista Internet Explorer problem

I am facing a problem with Internet Explore. When the search and access to a Web site I get a message box Windows telling me that there is a problem and Explorer closes down, There is a 'details' option that gives me the following information: -. Pro

-

Hello... I have a problem with windows 2003 to windows 2008 migration. I have try several round of flyway of google and youtube, but he is still fail. in the first,. I have HP Proliant server with windows server 2003. So I restore the backup to a dif

-

Now on windows 7, the games running slow - update video card driver error message and/or turn on hardware accelerator. Sony supporting not - how make to identift video card in my laptop?

-

Error 0 x 80244019 try reinstalling the updates for the 2007 version of XP

Puter crashed and I am trying to reinstall XP 2007 updates. It keeps giving me the error indicated in the title, without any explanation. I installed SP2, but impossible to find 3 for a SINGLE computer - is it? Gee, this should not be SO difficult.