Module FPGA unzip problem

I downloaded the FPGA module in a PXI controller, running XP. When I tried to unzip it, the unzip operation fails every time. What is the cause? Is there some sort of requirement for this unpack? Hard disk size requirement?

Thanks for help. I discovered what the problem was. I downloaded the FPGA module via the link below. When I tried to unzip it, I would use the default path. Apparently, the default path is a space at the end of his 2nd record, counting from the end of the path. It is a small bug in NOR, but it needs to be fixed. It is difficult to catch, because I don't expect something like that happening.

https://lumen.NI.com/nicif/us/evallvuser/content.XHTML

Tags: NI Software

Similar Questions

-

Impossible to find Pulse Width Modulation (FPGA, using SCTL)

Hi all

Can someone tell me where I can find Pulse Width Modulation (FPGA, using SCTL) .vi? I could not find in Finder example LabVIEW.

Thank you

Here it is...

-

LOCATION:

-I am developing a software plugin based on plug-ins based on LabVIEW classes that are instantiated in running. Plugin real classes come from the plug in generic classes that define interfaces to the VI instantiation and can provide basic functionality. This means that many of the methods of the class are dynamic distribution and even methods of child classes can call the parent method.

-Plugins top level (the ones directly accessible by the main VI) each have a run method that animates a plug-in specific state transitions.

-Transitions of the plug-in data acquisition (DAQ class) class calls a method of the DAQ class that reads data from an FPGA card OR and transmits to another component via a queue.

PROBLEM:

-Higher sampling rate, a FPGA-to-host FIFO overflow occurs after some time. When I "weigh" the system just by moving a window of Firefox browser on the screen, the overflow is triggered immediately. I did not have this kind of problem in older software, where I was also reading a FIFO of FPGA, but made no use of LabVIEW classes or diagrams.

SOLUTIONS I'VE TRIED (WITHOUT SUCCESS):

-J' put the transitions in a timed (instead of a simple while loop) loop that I assigned specifically to an own kernel (I have a quad-core processor), while I left all the other loops of my app (there many of them) in any simple loops. FIFO overflow still occurs, however.

QUESTION:

-Does anyone have a tip how I could fix this problem? What could be the cause: dynamic distribution methods, the acquisition of data of state transitions or just the fact that I have a large number of loops? However, I cannot change the fact that I have dynamic distribution methods because it is the essence of my architecture...

Tips are greatly appreciated!

I've now changed the execution priority of all the screws involved in reading of the FPGA FIFO '(highest) priority critical time '. This seems to be improving the situation much: so far I have not a FIFO overflow, even when I move around the windows on the screen. I hope it stays like that...

-

Chassis FPGA deployment problem

Hello!

I use cRIO 9024 with a voice coil actuator control modules.

The problem I have is that when I run the FPGA code, he said "the chassis is in programming mode Interface to Scan. In order to run the FPGA screws, you must go to the property page of the chassis, select the FPGA programming mode and deploy settings. »

So I checked the property, but it has been defined as "FPGA programming Mode. Also when I'm trying to deploy the chassis, I have error message "LabVIEW: (Hex 0x80DF0010) current deployment operation has a missing dependency."

Since I'm not the one who wrote the code, I have no idea what causes this problem. This code is used for the different game with the same model of cRIO but different modules. I've already replaced modules that I use with those that are necessary for this code.

Anyone know what is happening here, please?

Thanks in advance to 1 million.

Geehoon

-

cRIO-9024 + chassis 9113 NOR + NOR 9881 (CANopen) FPGA compile problem

Hello

I started to learn the Labview and I want to communicate with CANopen (9881) interface FPGA module, but there is a problem.

Normally (without NI 9881), I can compile and run a VI file with FPGA interface, BUT after adding 9881 (in the slot1) to the chassis (9113) I can not compile any VI (same same file VI) with worker compilation. Even if I delete the Mod1 (Slot1, NI 9881) of the project, I can compile the file VI.

I need compile bit files in order to use the library can open, but I could not find the problem.

Can someone help me? Thank you.

The error is below to:

...

Analysis of

entities.

Architectureanalysis of the entity.

ERROR: HDLCompiler:849 - "D:\NIFPGA\jobs\g8Q6537_ibm705i\CcMuxSLN.vhd" line 794: Unexpected EOF.

File VHDL D:\NIFPGA\jobs\g8Q6537_ibm705i\CcMuxSLN.vhd ignored errorsHi Matt,

I uninstalled everything about LabVIEW and reinstalled, I did update, now the problem is solved. It compiles the file bit.

Thank you.

-

ARM module + PWM LM3S8962 problem

Hello.

I'm experimenting with LV2009 + Embedded module for ARM (also the 2009 version).

(1) what actually works, a few screws, I did (no examples):

-loop infinite + led flashing + 200ms wait timer

-infinite loop + number of the current iteration on LCD + 200ms wait timer

(2) the demos provided in

/examples/lvemb/ARM/LM3S8962 sistematicaly (PWM, Blinky, DIO, OLED) fail. Ex: DIO relies, but throws an exception when it is downloaded on the dev. BOAD and executed; PWM does not build (not a filled.ctl or a update.ctl lack of file problem, I fixed) - something related to a PID Subvi. What I'm doing wrong here? Any help? (Note: I also changed the parameter debugger & programmer of the project uVision, the default ULINK2 fails of course). (3) PWM EIO problem: I got the first aforementioned VI (1) (LED light MagNet) and added a HIO PWM5, in the same loop.

-What is the wired to the PWM EIO node value mean? Duty cycle 0 to 100? Duty cycle 0 to 1? The number of ticks to the top state PWM? Sometimes it worked, sometimes the PWM was logical high all the time.

-If I add a property PWM5 EIO node and try to put anything, it breaks. From what I've seen in the uVision debugger, it gets stuck in the default interrupt handler section. I can't understand how he got there.

Please help me with an example of how fully configure a PWM EIO, exercising control over the frequency of having to test cycle, everything.

Thanks in advance for your time & help.

Paul.

Hi Paul,.

This looks like a problem where you (or rather the code generated LabVIEW) set up the device before you activate the device PWM. The target will fault in this case, but the Simulator will not. Because that the PWM EIO node initializes and allows the PWM peripheral, if the EIO property node is executed before the EIO node, the target reproach. Try using a sequence structure to make sure that the node of PWM EIO runs before the property node.

-

difference between the real time module and module fpga

Hi experts,

I was wondering if someone could tell me the difference between the FPGA and the module in real time (in short).

My understanding is that the FPGA module facilitates code LV that can then be designed for the specific advice of RIO, I have used this a bit in the past.

The real time module, I'm a little more unsure about, all I know is that it allows the creation of a 'real time' i.e. deterministic environment.

My request is this: I wish I had several control loops running on two tables of RIO, with the host PC mainly used for recording data and user interface. I see that I have no need of RT on the host (Win XP should be good).

Do I need the RT module?

You are right. In the scenario you describe, you won't need to LabVIEW RT. LabVIEW RT is used to create a deterministic execution on specific targets for intel such as the PXI-8106 and PXI-8108. You can still use strings and floating point on RT.

-

Using in a project (Module FPGA) LabVIEW FPGA targets

Hi, I'm currently adding a FPGA target in the Local development computer, according to http://zone.ni.com/reference/en-XX/help/371599H-01/lvfpgahelp/adding_an_fpga_target/

Here are the steps:

- Or create a new project , open an existing project.

- "Right-click my computer in the Project Explorer window, and then select New" targets and devices of the

But I can not find targets and devices in the menu new. I have only this window (see file attachment).

Is there something to do before? I installed the FPGA module.

Thanks for your reply.

OK, but it is not necessary, I found myself. Thank you.

-

Hello

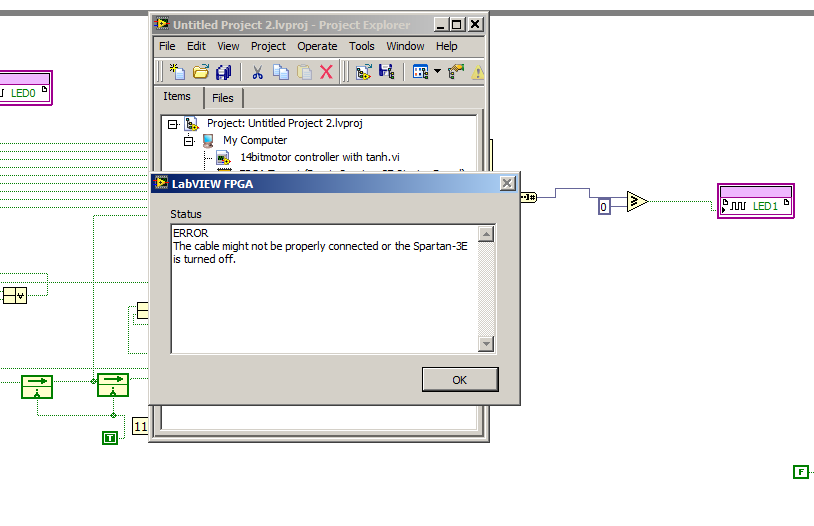

I'm trying to interface labview fpga to 2012 with Spartan E 500

I am facing two problem

a first in the figure below when I try to download Flash memory of Spartan E?

I run vi on Spartan works well but when I download it the error appear

also there is no "" "run when loading" "button which are available in a previous version of labview.

Please help

I don't have a LVFPGA version with the support of 3rd Spartan installed in front of me, so I'm working from memory here, but the option to run the VI on charge moved to the target property page (available on a right click on the target'Properties) of the standard build for the VI (as shown in your own message here)

-

Butterworth on Labview 8.6 FPGA filter problem

Hello

I was testing the filters of reconfigurable low-pass butterworth on FPGA found from the Finder of example (using Reconfigurable Butterworth filter - R - series.lvproj). This VI generates a sinusoidal signal and passes through a filter of Butterworth. When I put the filter low pass frequency to a low value (~ 2 Hz) and generate a sinusoidal signal of 0.5 Hz filttered out is not so much more (see figure). The filter is 2nd order, so this is a characteristic of the filter? And what do I do if I want a taste of high-frequency and use a low cutoff value?

v: * {behavior:url(#default#VML) ;}

O'Bryan: * {behavior:url(#default#VML) ;}

w\: * {behavior:url(#default#VML) ;}

. Shape {behavior:url(#default#VML) ;}Normal

0fake

fake

fakeMicrosoftInternetExplorer4

/ * Style definitions * /.

p.MsoNormal, li. MsoNormal, div. MsoNormal

{"mso-style-parent:" ";"}

margin: 0 cm;

margin-bottom: .0001pt;

MSO-pagination: widow-orphan;

font-size: 12.0pt;

do-family: "Times New Roman";

mso-fareast-font-family: 'Times New Roman' ;}

@page Section1

{size: 612.0pt 792.0pt;}

margin: 72.0pt 89.85pt 72.0pt 89.85pt.

MSO-header-margin: 35.45pt.

MSO-footer-margin: 35.45pt.

MSO-paper-source: 0 ;}

div. 1

{page: Section1 ;}}

--> I'm using Labview FPGA Module version 8.6 and PCI-7833R-map. LabVIEW 8.5, I remember that Butterworth filters, for above and below 2 kHz cutoff frequencies are actually different screws but on LV 8.6 they seem the same./ * Style definitions * /.

table. MsoNormalTable

{mso-style-name: "Table Normal";}

MSO-knew-rowband-size: 0;

MSO-knew-colband-size: 0;

MSO-style - noshow:yes;

"mso-style-parent:" ";" "

MSO-padding-alt: 0 cm 0 cm 5.4pt 5.4pt;

MSO-para-margin: 0 cm;

MSO-para-margin-bottom: .0001pt;

MSO-pagination: widow-orphan;

do-size: 10.0pt;

do-family: "Times New Roman";

MSO-ansi-language: #0400;

mso-fareast-language: #0400;

mso-bidi-language: #0400 ;}-Heikki

Hi Heikki,

The reconfigurable version (IE, with 'See the terminal configuration' checked) does not support the implementation of low-frequency modified. This is because we cannot change the filter architectures running. The nonreconfigurable version, however, must use the same implementation updated him you saw in LabVIEW 8.5 for the low cutoff frequencies, defined here as the frequencies less de.01 * sampling frequency.

Your example of 100 kech sampling rate. / s and 2 Hz cut-off is pretty extreme, even for the implementation changed. The usual technique for situations like this must be a smoothing downsampling at a rate that is better suited to the break you need. Rational resampling of the FPGA Math palette & analysis is designed for this purpose.

Kind regards

Jim

-

synchronization sequence FPGA structure problem

Hello

I use a sequence structure in a VI on the FPGA to a cRIO-9073. The time of each sequence is active is determined the number of times defined by the user. In theory, each sequence should take the same amount of time, but when I check it with an oscilloscope is not the case. The signals produced do not have the same cycle. When the number of ticks is equal to 1 in the VI on the FPGA, I receive a frequency of 400 Hz, approximately to the blockwaves outputs. I expect it is much higher since the FPGA runs at a frequency of 40 MHz clock. Why the frequency of the signals so low and why isn't the market factor the same for all signals?

Best regards

Beurms Jasper

Several of your synchronization on the FPGA screws are set in milliseconds, not ticks; in all cases but cases #2. I hope that this is the problem. Double-click the VI and change the setting. In fact, why have a timer to wait in any case? Just pull it outside the structure of the case and have 1 instance of the VI in the while loop. Also, whenever I see the files named * _

it probably means that you do not use the source code control. I would highly recommend. -

Assessment module FPGA and Xilinx tools?

I am currently using a trial version of 2013 LabVIEW FPGA module When I Isaiah to compile my FPGA target, I go as far as to select the compile server. Here, I am unable to use the local compilation server because "Xilinx 14.4 tools are not installed."

I had the impression that Xilinx tools came with the FPGA module. In the installation of FPGA module, I have yet to select install Xilinx... What happens here? Is happening because I'm only using a trial rather than a recorded version? Or have I missed something? Do I really need to get the Xilinx tools separately?

Thank you!

Sara

Hi Sara,.

It is indeed a separate installation program. Give this a go!

OR LabVIEW FPGA Module Xilinx tools 14.4 2013

http://www.NI.com/download/LabVIEW-FPGA-Module-2013/4248/en/

-

Streaks stained on the images in module development [was: problem]

Why do I have this image when open develop modules? ... never I have this problem...

Left the connections for specific program forum forum... MOD

Hi Karina,

Open Lightroom preferences, go to the performance tab and deselect the option "use graphics processor."

Adobe Lightroom GPU troubleshooting and FAQ

Mike

-

LR5 - no base in the develop module Panel [was: problem upgrade Lightroom 5?]

I updgraded to L3 to L5 (Win8 64bits) without no problem, except for the 'Basic' Panel in the develop module. I tried the upgrade to have the 'new' slides here - highlights, shadows... But I still have the old (recovery, light...) there. What has gone wrong? What will I do to get updated?

If you change a photo that has been already transformed into Lr3, then you are probably using Version 2010 process, which includes the sliders as recovery and fill light.

You can update the PV2012 image in the camera Calibration Panel in the develop Module.

-

First Appcrash with Kernelbase.dll in the defective module always the problem

Hello world

After the update drivers associated with (Matrox, NVidia) the problem and checking the material, the problem persists:

Signature of the problem:

Problem event name: APPCRASH

Name of the application: Adobe first Pro.exe

Application version: 5.0.3.0

Application timestamp: 4ce382d1

Fault Module name: KERNELBASE.dll

Fault Module Version: 6.1.7601.17651

Timestamp of Module error: 4e21213c

Exception code: c0000005

Exception offset: 000000000000cacd

OS version: 6.1.7601.2.1.0.256.48

Locale ID: 1043

Additional information 1: 30ea

More information 2: 30ea564650b9f04e24c8d0b10bbe1000

Additional information 3 c: 895

Additional information 4: 895c2477ff9dd3b158f6107ec9f936c4

What makes in any case kernelbase.dll? It seems to fail clips HD special Matrox, but only when I play their first. It happens when I click on the first source window and then the timeline and then beginning of jogging or rub in the timeline panel. It is switching between source and first program that triggers the appcrash for sure.

While first actually did when you switch from source the program monitor in the app itself? I noticed on my HDMI video monitor when switching as mentioned, the monitor loses the input signal and is to scan the image. So I guess that this passage is more complicated for the first as you might think.

Any ideas yet? Nothing I tried really makes a difference. I start to panic a bit now.

Specs: Windows 7 64-bit, THE Matrox MX02, NVidia Quadro 4000, 24GO RAM, 2.66 sixcore dual CPU, in sense reverse video and OS discs.

Using the codec HD standard Matrox for first.

Any help much appreciated.

I'm sorry, I didn't notice the Quadro card in your initial post. The version that I gave you was for Geforce cards and the Quadro have a tree of different version. The Quadro version equivalent to the driver I meant 275.89. However, they have a Quadro version that is not yet out on their downloads page standard which has the equivalent properties on the latest Geforce. Download and install after you have uninstalled all the software/driver Quadro you currently have.

http://www.nvidia.com/object/Quadro-Tesla-Win7-WinVista-64bit-285.58-WHQL-driver.html

Make sure that you choose the custom installation and remove the Nvidia update installation list if it is there. Try and see if that helps. If this isn't the driver to try the 275.89.

Eric

ADK

Maybe you are looking for

-

Why is the new tab icon a square dotted?

Hey when I used to press the button "Add a tab", it would open a tab, and the icon in the tab was a picture of a blank page. It has now been replaced by a dotted square. first of all it's ugly and secondly I was not clicked on something else to chang

-

How to clean the inside of the laptop

G6 1201 tx. [Sorry posted in Audio, by mistake...] Please give me the link to the video message where: (1) computer laptop opening (2) clean internally (3) application of thermal paste is shown Thank you! My laptop is 21 months old now, so its therma

-

Problem of Outlook Express Inbox.

When I send a message, it appears in my Inbox as well as in sent items. How can I stop happening, please?

-

I get the same exact error messages, they began yesterday and my laptop is close and restart on every 20 minutes with error message appearing before having disconnected. I've tried everything that microsoft offer and still the error message appears,

-

Current situation / background -. I use SCCM 2012 R2 with WinPE 6.39 I created a sequence of tasks that currently allows the TPM chip, appropriates it, puts a password on the BIOS and then begins encryption, deployment of a new machine. We have place