synchronization sequence FPGA structure problem

Hello

I use a sequence structure in a VI on the FPGA to a cRIO-9073. The time of each sequence is active is determined the number of times defined by the user. In theory, each sequence should take the same amount of time, but when I check it with an oscilloscope is not the case. The signals produced do not have the same cycle. When the number of ticks is equal to 1 in the VI on the FPGA, I receive a frequency of 400 Hz, approximately to the blockwaves outputs. I expect it is much higher since the FPGA runs at a frequency of 40 MHz clock. Why the frequency of the signals so low and why isn't the market factor the same for all signals?

Best regards

Beurms Jasper

Several of your synchronization on the FPGA screws are set in milliseconds, not ticks; in all cases but cases #2. I hope that this is the problem. Double-click the VI and change the setting. In fact, why have a timer to wait in any case? Just pull it outside the structure of the case and have 1 instance of the VI in the while loop. Also, whenever I see the files named * _

Tags: NI Software

Similar Questions

-

Problem of generation of Sync trigger in several synchronization USRP RIO 2943R problem

Generation problem shutter Sync in several synchronization USRP RIO 2943R problem.

Previous SR you may already know I'm stacked in USRP RIO multiple synchronization problem, especially in the mode based on the signal. Now I can cut down, the problem is mainly due to the outbreak of sync signals generation.

First of all, I read the article and the discussion in the following two links:

http://forums.NI.com/T5/USRP-software-radio/how-to-synchronize-multiple-USRP-Rio-294x-devices/TD-p/3...

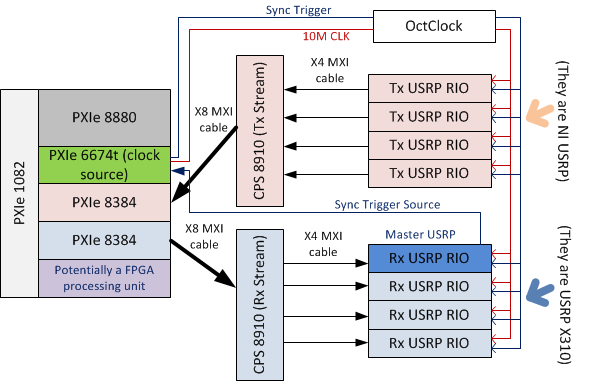

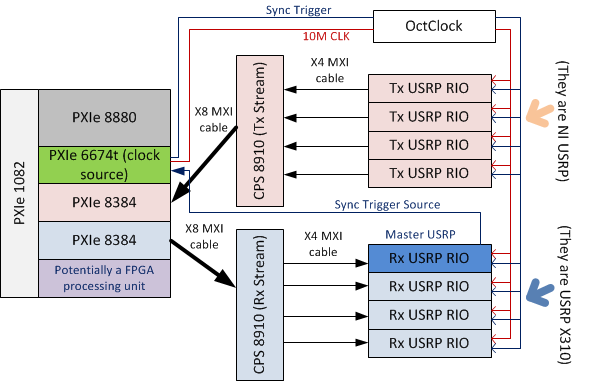

http://zone.NI.com/reference/en-XX/help/373380D-01/usrphelp/synchronization/and I did my connection of the material according to the suggestions in the second link. My system schematic is shown in the following image:

I checked OctColck and SMU 6674 T connections. They are all connected correctly and the cable are fine. I use the niUsrpRio200_XcvrSyncPps.lvbitx.

According to the description of documents and discussion forum, the USRP RIO 1st in the list of devices are considered to be the USRP Master. Then, the FPGA to master USRP RIO released "trigger of sync" signal through the 'PPS Trigger Out' SMA port in RIO USRP box.

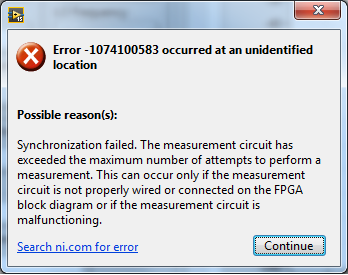

Based on the my analysis of the system, the first impression I have is the USRP Master does not export the 'sync trigger' correctly. The host VI reports the error like this:I was trying to measure the "synchronization trigger" using oscilloscope, but I found that it is impossible, because the host VI can not yet run, so there is that no signal can be seen from port 'PPS Trigger OUT.

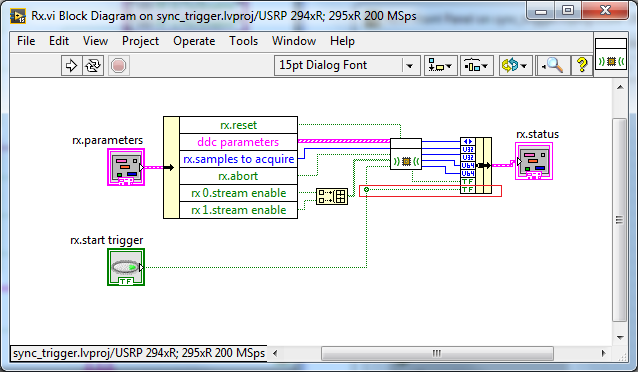

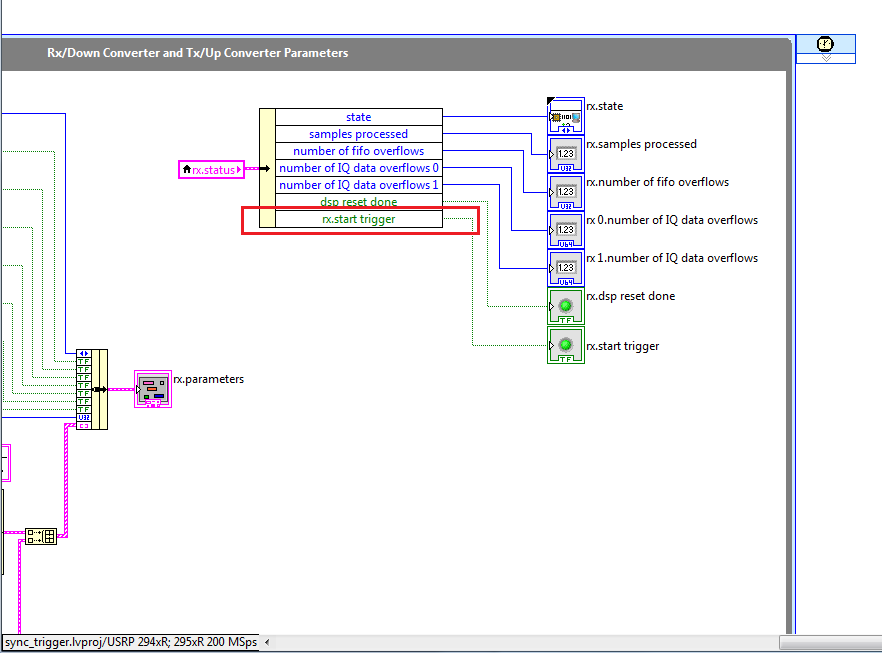

So I think that if I can watch this signal "sync trigger" in home VI by importing this signal from FPGA to host VI. I did some changes on the FPGA VI as shown in the following image to watch this signal of façade of the host VI. but not so successful. the rx.start tragger relaxation and tx.start do not appear on the host vi read/write control function.

-

Synchronize the FPGA clock for clock RT?

Hello

I use a sbRIO-9612. Data are acquired for several weeks, and the problem is that the clock of RT of derivatives. I found a technical document to synchronize the clock of RT with SNTP server:

http://digital.NI.com/public.nsf/allkb/F2B057C72B537EA2862572D100646D43?OpenDocument

But I do not find anything on the FPGA clock. My data are acquired by the FPGA, my question is: How can I synchronize my FPGA clock with my RT clock or the SNTP server? (this is probably a stupid question, but she clearly explains my problem) SbRIO is suitable for my needs? Should I waive any 'acquisition of FPGA based' and use a different hardware architecture to perform data acquisition synchronization?

Thanks in advance for any help.

Julien

Hi Julien,

Take a look at "RT masters FPGA synchronization Example.vi" on the FPGA Timekeeperpage. There's a Subvi, which uses a timed writing periodically present to the FPGA so that the FPGA can have a domain time synchronized with respect to RT if you have questions about this example, try to publish to category of Discussion of the project.

-Steve K

-

Synchronize the case structure with enum update

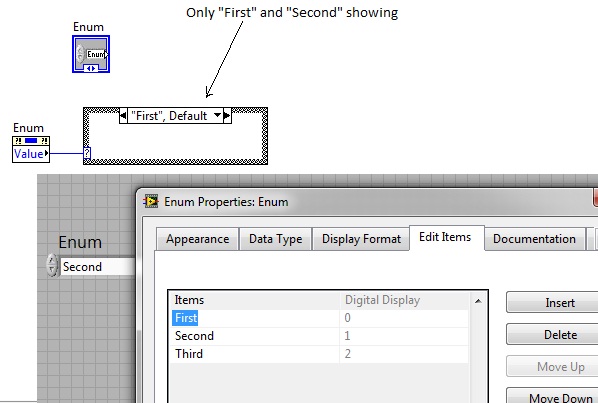

Hi, I created a control enum initially with the "First" and "Second" values. In the block diagram, I created a node of this enum control property and it is connected to a box structure. The structure of business allows me to manage the condition "First" or "Second" correctly.

I then modified the items in my enum so there is now a 'third party '. My problem is that structure business conditions still show as 'First' and 'second '; That is to say, I can't handle the "Third" condition My question is how to synchronize my case structure to show the updated enum values?

VI, attached, the sample created with LabVIEW 2009 version 9.0f3 (32-bit) running on Windows 7.

Thank you all for your help in advance.

Michael O'Shea

First tip: remove the value 'default' first case

If you have done your VI pauses when you change your enum, which is a good thing.

Now to synchronize, do a right-click on the border of the structure of the case and select 'add the case for all values', this is the option you are looking for.

Tone

-

Microsoft feeds synchronization has encountered a problem and needs to close

Original title: I get a window to appear several times, saying: RSS microsoft synchronization has encountered a problem and needs to close. How can I solve this problem and get rid of this problem?

I get a window popping up that says microsoft feeds syncronization has encountered a problem. How can I fix it?

Microsoft Feeds Synchronization popping up with maybe a message like this (try to get a real message):

If you mean that you see a message like this:

Microsoft Feeds Synchronization has encountered a problem and needs to close.

AppName: msfeedssync.exe AppVer: 8.0.6001.18702 ModName: user32.dll

ModVer: 5.1.2600.2622 Offset: 000095d 8Deactivation and activation of the synchronization stream again will usually straighten it...

Click Start, run and enter in the box:

cmd

Click OK to open a command prompt window, and then run the following commands one at a time from the command prompt:

msfeedssync disable

There will be no message about what happened

msfeedssync enableThere will be no message about what happened output

Farm window command prompt -

Message when it is "Microsoft feeds synchronization has encountered a problem and needs to close." He appears again and again. Despite the reboots, Defrag, etc. Is there a solution?

Read this thread and see if the links help you.

If not post back with more information:

make and model of the pc, current anti-virus, OS and ServicePack, current browser?

What is pop up only in IE or any time?

-

Multiple, overlapping nodes or canvas in a pane: the sequence of rendering problems

I have the following problem:

1 stream outside, inside the following items in the following order:

... (1) canvas (0,0,100,100)

... (2) button (0,0,100,30)

... (3) the canvas (90,90,100,100)

... (4) button (90,90,100,30)

So there is an overlapping area of 10 x 10 (between 1), (2) and (3), (4).

When moving with the mouse on the button 4 then 1-canvas is drawn on the 2 key - that is not correct.

It seems to me like a-sequence/dependency-rendering problem: moving the mouse makes again 4-button, triggering a new rendering of the Web 1 because of that overlap, but 2 buttons seems not to be re-rendering.

Is there a "thought/understanding" - problem on my side? -No suspicion is apprecaited...

Thank you!

This is the code to reproduce, when running: move the mouse on "(4) button.package ztest; import javafx.application.Application; import javafx.scene.Scene; import javafx.scene.SceneBuilder; import javafx.scene.canvas.Canvas; import javafx.scene.control.Button; import javafx.scene.layout.Pane; import javafx.scene.paint.Color; import javafx.stage.Stage; public class Test_40_Canvas extends Application { class MyPane extends Pane { Canvas m_canvas1; Button m_button2; Canvas m_canvas3; Button m_button4; public MyPane() { m_canvas1 = new Canvas(); m_button2 = new Button(); m_canvas3 = new Canvas(); m_button4 = new Button(); getChildren().add(m_canvas1); getChildren().add(m_button2); getChildren().add(m_canvas3); getChildren().add(m_button4); m_canvas1.setWidth(100); m_canvas1.setHeight(100); m_canvas1.getGraphicsContext2D().setFill(Color.GREEN); m_canvas1.getGraphicsContext2D().fillRect(8,8,92,92); m_button2.setText("(2) Button"); m_canvas3.setWidth(100); m_canvas3.setHeight(100); m_canvas3.getGraphicsContext2D().setFill(Color.BLUE); m_canvas3.getGraphicsContext2D().fillRect(8,8,92,92); m_button4.setText("(4) Button"); } protected void layoutChildren() { m_canvas1.resizeRelocate(0,0,100,100); m_button2.resizeRelocate(0,0,100,30); m_canvas3.resizeRelocate(90,90,100,100); m_button4.resizeRelocate(90,90,100,30); } } public static void main(String[] args) { launch(args); } MyPane m_pane; @Override public void start(Stage primaryStage) { primaryStage.setTitle("Hello World!"); final Scene scene = SceneBuilder.create() .root ( m_pane = new MyPane() ) .build(); primaryStage.setScene(scene); primaryStage.show(); } }I consider this behavior a bug. A quick and dirty solution would be the following, even if I do not want to do that in a real application:

package ztest; import javafx.application.Application; import javafx.scene.DepthTest; import javafx.scene.Scene; import javafx.scene.SceneBuilder; import javafx.scene.canvas.Canvas; import javafx.scene.control.Button; import javafx.scene.layout.Pane; import javafx.scene.paint.Color; import javafx.stage.Stage; public class Test_40_Canvas extends Application { class MyPane extends Pane { Canvas m_canvas1; Button m_button2; Canvas m_canvas3; Button m_button4; public MyPane() { setDepthTest(DepthTest.ENABLE); m_canvas1 = new Canvas(); m_button2 = new Button(); m_canvas3 = new Canvas(); m_button4 = new Button(); getChildren().add(m_canvas1); getChildren().add(m_button2); getChildren().add(m_canvas3); getChildren().add(m_button4); m_canvas1.setWidth(100); m_canvas1.setHeight(100); m_canvas1.getGraphicsContext2D().setFill(Color.GREEN); m_canvas1.getGraphicsContext2D().fillRect(8,8,92,92); m_button2.setText("(2) Button"); m_canvas3.setWidth(100); m_canvas3.setHeight(100); m_canvas3.getGraphicsContext2D().setFill(Color.BLUE); m_canvas3.getGraphicsContext2D().fillRect(8,8,92,92); m_button4.setText("(4) Button"); } protected void layoutChildren() { m_canvas1.resizeRelocate(0,0,100,100); m_canvas1.setTranslateZ(4); m_button2.resizeRelocate(0,0,100,30); m_button2.setTranslateZ(3); m_canvas3.resizeRelocate(90,90,100,100); m_canvas3.setTranslateZ(2); m_button4.resizeRelocate(90,90,100,30); m_button4.setTranslateZ(1); } } public static void main(String[] args) { launch(args); } MyPane m_pane; @Override public void start(Stage primaryStage) { primaryStage.setTitle("Hello World!"); final Scene scene = SceneBuilder.create() .root ( m_pane = new MyPane() ) .depthBuffer(true) .build(); primaryStage.setScene(scene); primaryStage.show(); } } -

Muliple USRP RIO 2943R, synchronization and phase-locking problem

I use 8 USRP RIO 2943Rs transmission of signal and receving (4 for Tx) and 4 for Rx I'm using the "signal-based" method for synchronization of all devices. And I did it. I tested the system the result is very interesting:

1. when I put the sampling rate of less than 40MS/s IQ, I can obversve very good phase locked Tx and Rx signals (I use a sine wave CW for tests), please refer to video joint (locked 40MSs)

2. BUT, when I put the IQ more than 60 MS/s sampling rate, I'll lose phase lock. Please refer to unlocked 60MSs. My goal is to run the system at 120MS/s

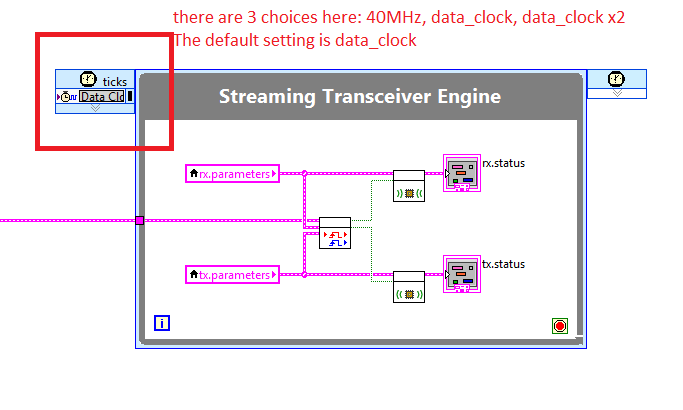

I have doubt as to if the problem comes from two sides:

a. the sync methed isn't fair

b. OR, should I increase the clock that operates the loop 'In Streaming radio engine' in the FPGA VI. as shown in the following image.I would like to ask experts in the forum to discuss the solution of this problem.

More information about my system setting:

-

C100 /. Import MTS in sequence, Audio only problem

Good evening!

I have encountered this problem several times, and have absolutely no idea how to solve this problem! I know what I did wrong and is to simply copy the video files and not the whole AVCHD file structure on my memory card.

Anyway, here's the question:

- I can import all. MTS in Premiere Pro files

- I can play together. The MTS in Premiere Pro files in the Source - Source poster audio & video monitor monitor correct

- I can create a new sequence with a video file by dragging the video file in the project window to the icon "create a new", next to the folder and the Recycle Bin icon in the project window. The new sequence shows the video clip with correct audio & video in the timeline.

- When I go to select another element of the project window and drag it to the same timeline, I get only the audio track in the timeline panel. There is no video track.

The only work around I have found was to create a new sequence, whenever I want to use a specific clip, then in the new chronology of the sequence, select the item, make a right click, select copy, and then go on my calendar of 'main' sequence and paste the clip in the timeline. It is very annoying and a lot of your time.

Any help is greatly appreciated.

Note: To add, I have recently switch from a drive to an SSD. Now, I have a 1 TB SSD in my PC and have had this problem on the two old my HDD and on my new install SSD.

Note: To clarify, the video IMPORT in first very well. When I put the videos on a timeline, only an audio track is going in the timeline. See the image below.

For those who have this problem, I found the solution. It's a completely stupid mistake, but all you have to do is click on the gray "V1", next to the left until now controls visibility on the first video track of the timeline. If you look at the screenshot in the original post, there are two blue icons of A1. There is only one blue icon of V1, and you have to make two of them blue simply by clicking on the gray.

-

try to set up synchronization, a lot of problems.

I just had to reset FF by default, and he forgot my synced data. No problem, I'll just be reintroduced in this one.

Of course, I went to tools-> Options-> synchronization. Then things are weird.

So I tried 'Set up Firefox sync', it opens another window. Fine, but then the button "I have an account" does nothing. Click, click, click, click, click, nothing happens, it's without the feature.

Then, pair a device, which is how I normally do, the link at the bottom of the window 'I don't have the camera with me' (which is poorly formulated in my opinion) is simply absent. He isn't here. Went. If you want, I can make you a screenshot.

So, I don't know what to do now. I want just sync.

You are welcome.

If it still happens once then you can check for problems with the sessionstore.js and sessionstore.bak files in the profile folder of Firefox that store session data.

Delete the sessionstore.js file possible sessionstore-# .js files with a number and sessionstore.bak in the Firefox profile folder.

You can use this button to go to the Firefox profile folder:

- Help > troubleshooting information > profile directory: see file (Linux: open the directory;) Mac: View in the Finder)

- http://KB.mozillazine.org/Profile_folder_-_Firefox

- http://KB.mozillazine.org/Multiple_profile_files_created

Note that delete sessionstore.js will cause App Tabs and groups of tabs open and closed tabs (back) to get lost and you will have to re-create them (take note or bookmarks if possible).

-

Chassis FPGA deployment problem

Hello!

I use cRIO 9024 with a voice coil actuator control modules.

The problem I have is that when I run the FPGA code, he said "the chassis is in programming mode Interface to Scan. In order to run the FPGA screws, you must go to the property page of the chassis, select the FPGA programming mode and deploy settings. »

So I checked the property, but it has been defined as "FPGA programming Mode. Also when I'm trying to deploy the chassis, I have error message "LabVIEW: (Hex 0x80DF0010) current deployment operation has a missing dependency."

Since I'm not the one who wrote the code, I have no idea what causes this problem. This code is used for the different game with the same model of cRIO but different modules. I've already replaced modules that I use with those that are necessary for this code.

Anyone know what is happening here, please?

Thanks in advance to 1 million.

Geehoon

-

TO RESET THE GRAPH AND TABLE SEQUENCE EVEN STRUCTURE IS NOT EXECUTED.

Hello everyone, I made this vi which runs automatically at the beginning and I can't use my power butoon to control this vi. Now, I want to clear the table and graph vi even when the structure of sequence is not executed as the start/stop button. And I want also when I run the program both the graph and the table should be cleared. I tried a lot of things, but as I'm new to labview I can't do. Thanks in advance.

-

cRIO-9024 + chassis 9113 NOR + NOR 9881 (CANopen) FPGA compile problem

Hello

I started to learn the Labview and I want to communicate with CANopen (9881) interface FPGA module, but there is a problem.

Normally (without NI 9881), I can compile and run a VI file with FPGA interface, BUT after adding 9881 (in the slot1) to the chassis (9113) I can not compile any VI (same same file VI) with worker compilation. Even if I delete the Mod1 (Slot1, NI 9881) of the project, I can compile the file VI.

I need compile bit files in order to use the library can open, but I could not find the problem.

Can someone help me? Thank you.

The error is below to:

...

Analysis of

entities.

Architectureanalysis of the entity.

ERROR: HDLCompiler:849 - "D:\NIFPGA\jobs\g8Q6537_ibm705i\CcMuxSLN.vhd" line 794: Unexpected EOF.

File VHDL D:\NIFPGA\jobs\g8Q6537_ibm705i\CcMuxSLN.vhd ignored errorsHi Matt,

I uninstalled everything about LabVIEW and reinstalled, I did update, now the problem is solved. It compiles the file bit.

Thank you.

-

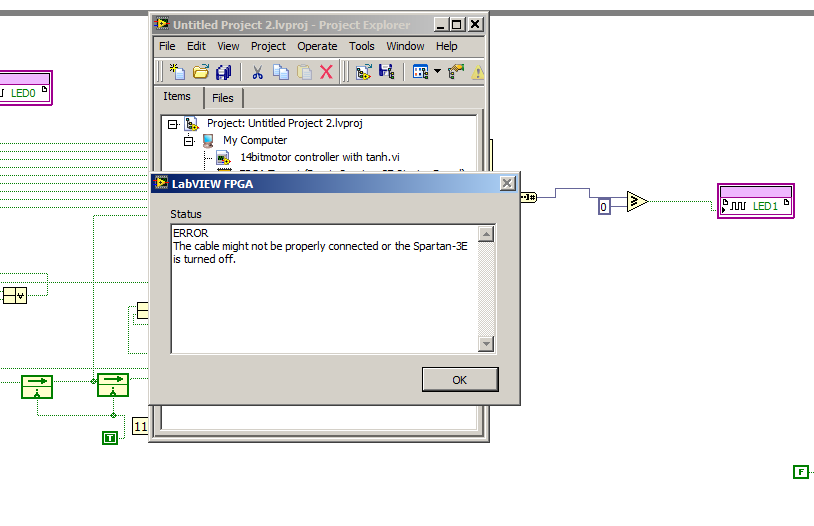

Hello

I'm trying to interface labview fpga to 2012 with Spartan E 500

I am facing two problem

a first in the figure below when I try to download Flash memory of Spartan E?

I run vi on Spartan works well but when I download it the error appear

also there is no "" "run when loading" "button which are available in a previous version of labview.

Please help

I don't have a LVFPGA version with the support of 3rd Spartan installed in front of me, so I'm working from memory here, but the option to run the VI on charge moved to the target property page (available on a right click on the target'Properties) of the standard build for the VI (as shown in your own message here)

-

I downloaded the FPGA module in a PXI controller, running XP. When I tried to unzip it, the unzip operation fails every time. What is the cause? Is there some sort of requirement for this unpack? Hard disk size requirement?

Thanks for help. I discovered what the problem was. I downloaded the FPGA module via the link below. When I tried to unzip it, I would use the default path. Apparently, the default path is a space at the end of his 2nd record, counting from the end of the path. It is a small bug in NOR, but it needs to be fixed. It is difficult to catch, because I don't expect something like that happening.

Maybe you are looking for

-

I'm using a 1st generation (A1143) AirPort Extreme, but the wireless signal covers any parts of my house (problems with the strength of the signal on the 2nd floor). An upgrade to the latest AirPort Extreme would improve the situation?

-

Windows 7 1 800700 update error code

It is with Windows 7 Home Premium 32 bit. When you try to update. I get this error code and it won't dl/install updates. I never had this problem before and she appeared just not the case. No idea how to solve this problem?

-

How to install windows xp in dell vostro laptop 1015

Hello... I have laptop Dell vostro 1015, and this is pre loaded with the ubuntu operating system. How can I replace it with windows XP. Please Thank you

-

I have a laptop dell latitude E5400. but my wireless is no more appear.

I had a bluetooth program and built in the wireless on this subject, but I was using this internet modom of verizon for a while until that recently collapsed I to pay for it. but now my laptop has a wireless network or anything close to it. I don't k

-

Smartphones blackBerry device software upgrade

Software upgrade system could be installed on my computer, but apparently something wrong with the Desktop Manager. He doesn't want to upgrade. Once earlier I was able to update via the Desktop Manager but lately it seems that something has gone wron