pipelining in FPGA Rio

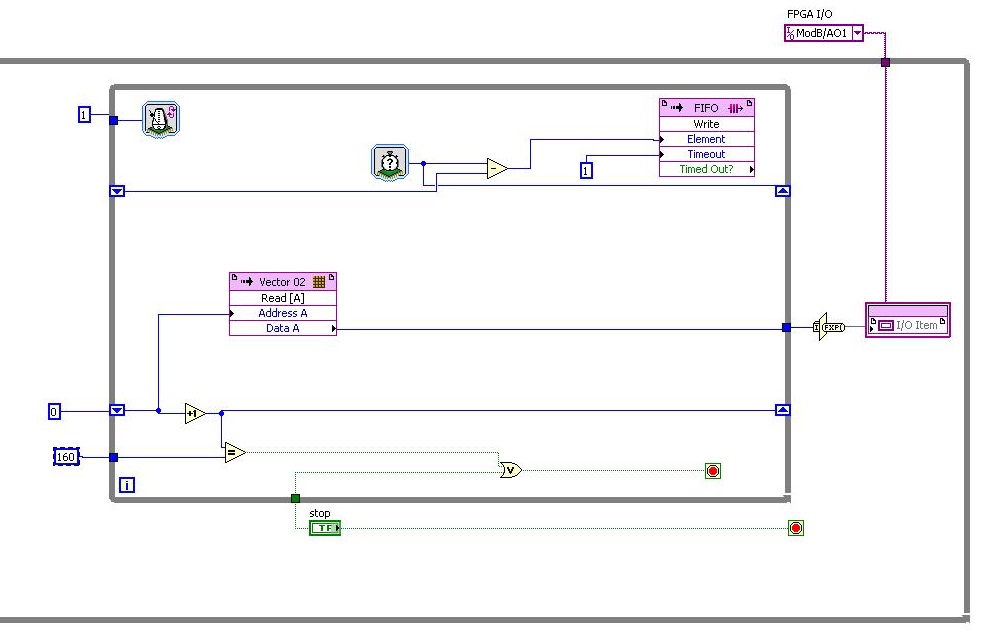

Just a simple question about the pipelining. I have a simple calculation. What will be called a scalar product of two vectors X 1 and W1 giving X X 1' where ' is transposed.

I have the joint programme. I could improve this program by introducing a time limit after the multiplier (IE a register shift)?

Is that all I could do? I am quite at this new, but just need a referral.

Thank you

Hi Tom,

We don't know what you're trying to get the code you posted. It looks like you multiply two numbers together and adding this product to the previous iteration? I'm not sure why are would like to add a delay as well.

If you re-post with a more detailed explanation of what is the problem, someone may be able to help much better.

Thank you!

Tags: NI Software

Similar Questions

-

FPGA device configuration, package and speed grade.

Hello.

Where can I find the news of grade package and the speed of the FPGA inside of the PXI-7842R? I ask because I want to build a project XPS in the Xilinx XPS and program needs this info.

I followed the example in the "how to use designs based on Xilinx Microblaze with NI LabVIEW FPGA 2009 and the R-series modules". There, he gives the info for the specific FPGA (PXI-7852R and PXI-7953R) they use. It's a Virtex5, ff676, xc5vlx50, level-1 speed, but the authors do not mention where one can find this info.

Thank you

Bill.

Nevermind, found the info in this way:

Instruments\LabVIEW national 2010\Targets\NI\FPGA\RIO\R Series\Pxi-7842r

Bill.

-

Target visible FPGA in MAX but not in LabVIEW

Hey!

I recently installed a RIO device. Before installing the equipment, I installed the module FPGA & RIO 3.0 as directed. Now, I can see the device in a position & automation explorer, but its not in list "Add target & devices. It says "No device found" in the existing devices tab. I don't understand the problem. :/

Add the target under 'my computer '.

Christian

-

I have a PXI FPGA RIO of 7133 card. He is seen by MAX but not available through 'my computer' in a project. The card may have been moved to a different location PXI after initial installation. Any suggestions?

The problem disappeared after uninstalling the drivers PXI-7833 and module FPGA and then put it back. All cards in the PXI chassis (which is full) are now recognized in MAX and the 7833R appears as a target (formerly it does not appear as a target).

-

VST-5646R IQ given by 7976R and the second VST-5646R pipes

I'm new to VSTs and a demonstration of the installation of a client. They want to use the side RX to a VST and IQ data through a pipeline 7976R FPGA then IQ data processed at the TX side a second pipeline VST. They want to compare the performance between the edge and the pipeline on FPGA processing.

One thing the customer told me, is that they have been warned against put the code in the FPGA VST because there was a chance that this could damage the edge of the map features. How valid a concern is it? Only panels soft download IP address required to the VST when they work?

Thank you

Drew

I don't think so. As long as you use the IDLs that are provided with the VST (those on the interface FPGA palette), you should be safe. Nothing you can do with those permanently ruin your VST configuration. All the corruption should be temporary. As you mentioned, if you start to have problems or strange errors when you work with custom bitfiles, opening and closing of the façade of the DAA/G should give you a reset on the configuration settings.

-

High-speed FPGA personality my Rio

Hello

I started on a Rio My 1900 I am programmer in C language so without by Ferryman Labview.

I wish I could sample a signal to a frequency higher than those possible with the standard personality FPGA provided. The doc of the RIO my dt requires high-speed FPGA personality it takes to download the site of NI I therefore downloaded but son installation requires labview 2014...

How can I do?

Thanks in advance for your help.

Françoise

Hello

To change the FPGA, USE of it requires LabVIEW and FPGA module. You can only use the default personality pour en C development.

Kind regards

-

Compilation of RIO Evaluation Kit FPGA

Hello

When runing, the status of compilation compilation shows 'Compilation error', but the Xilinx log is empty. Hane no idel what the problem is.

The area:

LabVIEW 2015 development professional sp1

LabVIEW FPGA compile worker 2015

LabVIEW RIO Eval Kit

Uninstalled/Reinstalled "LabVIEW 2015 development professional sp1 ',"LabVIEW FPGA mudle"and" LabVIEW FPGA compile worker 2015 ", but does not help."

Help, please!

Hi Thomas,

You might want to take a look at this post on the forum, where another user seems to have a similar problem as you: http://forums.ni.com/t5/Academic-Hardware-Products-ELVIS/fpga-compilation-error-LabVIEW-2015/td-p/32...

My guess is that this has to do with an error in download of Vivado Xilinx tools. Since you are using LabVIEW 2015, you need Vivado 2014.4. Based on your original screenshot, looks like you are using this version. Do you know if you have other versions installed on your computer? If you do, it is possible that your dll point to the incorrect reference to a different version.

I recommend to repair your installation of Vivado 2014.4. You can repair according to the installation found at the following link: http://www.ni.com/download/labview-fpga-module-2015/5492/en/

-

Hello!

I'm in the quest to replace some aging PCI-5640R. I am currently using as a portable-Journal data solution, mounted in a Magma Expresscard to PCI box with a laptop. As a reference of the time, I use a Symmetricom XLi.

The equipment is dependent on the sampling finished a set of samples once a trigger signal goes high and also receive antenna azimuth information using two lines PFI more. The signal is sampled at IF, 30 MHz, and the signal is less than 5 MHz bandwidth.

Now, I started watching the Ettus X 301 with a GPS OCXO and MXI-express interface which should be the same as the USRP-295xR NI. It is available as device NI RIO with three different front ends, unfortunately, none of them work at 30 MHz.

Q-1: Ettus has the front-end 'BasicRX', but it is only considered compatible with LabVIEW driver and not necessarily with the RIO. Is the front-end BasicRX usable with the USRP - 295XR RIO and MXI-interface with LabVIEW FPGA? Should I just avoid trying tune the nonexistent LO? As long as he gives me data, I can live with some error messages during the Setup...

It's the best solution for me, but if it is absolutely impossible, I have a few questions:

Q-2: information on the front end are really rare in the pages Web OR both Ettus, but the WBX is listed up to 50 MHz frequency, to have a filter of low pass of bandwidth of 40 MHz to I and Q. This should mean a total of 80 MHz of bandwidth with I and combined Q,-40 to 40 MHz. Why did the bandwidth to Web pages as OR listed being "40 MHz bandwidth in real time", if the low pass filter of the WBX is 40 MHz in I and Q? Not the band total bandwidth or 80 MHz?

Q-3: assuming a bandwidth-40 to 40 MHz: could I put the WBX LO at 50 MHz, be tuned to the frequencies from 30 MHz to 20 MHz signal,-20 MHz and use a bandpass filter to the FPGA to extract the new signals and remove all other signals?

Q 4: I tried to start a FPGA project in LabVIEW and add the x 301/294xR/295xR as a target. Data clock is locked to 120 MHz, which I guess means he will receive no data to 120MS/s IQ? The x 301 Ettus is listed as provide data of the ADC to the FPGA at a rate of 200 ms/s, could someone explain to me why, OR USRP RIO expects only database 120MS/s?

Hi Idar,

Yes, you should be able to put the basics on your X 310/USRP RIO and use LabVIEW FPGA to receive 120 MECH. / s of the DACs. The example I posted is in fact not for the precompiled file bit. The example I posted is for LabVIEW FPGA, which allows you to add the IP address for the FPGA. There is a sample project that comes with LabVIEW FPGA which is the recommended starting point to build your FPGA application. The sample project has all the configuration set up as well as broadcast continuously and pads/FIFOs in the FPGA and examples for synchronization. There are comments in the code example that show where he must add your own blocks of property intellectual as a filter and decimater you mentioned. The PDF I posted shows what changes you must make to this sample project using the Remora Basic/LF.

I would like to know if I'm not explaining this clearly, or if you have any questions, I'd be happy to help you!

-

FPGA - try to use the screw of the replication of RIO to replace going to reset the FPGA running

Running LabVIEW 12.1

We have an application that uses an FPGA that was compiled in Run to Reset (works on any reset or power on). Sometimes we need to update the image on the RT and FPGA and I downloaded the NI RIO replication screw.

The problem I have now is that when I got to download the bitfile on the Flash FPGA on the sbRIO9636, I get the following error:

Error-61141

Possible reasons:

LabVIEW FPGA: The operation could not be performed because the FPGA is busy. Stop all activity on the FPGA before asking this operation. If the target is in the Interface of Scan program mode, put in FPGA Interface programming mode.

My updater is stand alone EXE. He isn't able to get a link to the FPGA, because we are not sure what Bitfile currently is on a particular system. I tried using the open FPGA reference and load a VACUUM on the FPGA bitfile by setting the FPGA to RUN when he sound the FPGA VI of the Open reference - and it works for me to erase the bitfile. It does not allow me to immediately after run the bitfile VI of replication of RIO download - even if I close and reset the FPGA before trying to download the Bitfile for the RIO Flash.

I have to first delete the existing bitfile, then load a new?

Well, I found what I consider as a workaround - but maybe it's required to do things - but it doesn't seem like it should be, since the RIO device Setup.exe is able to flash or clear the bitfile regardless of the State of the FPGA.

What I've done is to define the FPGA to "do not load automatically on re" then call the RT Config screw system and order a restart of the system. The RT operating system restarts and then restarts the RIO system and this ensures that the FPGA is not busy. Then I'm able to erase them or write about a new bitfile for the RIO Flash and set the "Automatic loading on any Reset" Rio de JANEIRO and restart the system again.

Our current situation, it will work. Long time restarts do a bit of headache.

-

FPGA Interface C API, error-63105, OR-RIO: C/C++ identifier is already in use and cannot be created.

Hello

Installation program:

1 x the NI PCIe-7841R

When I am trying to automatically generate a C++ API for my top FPGA VI using the FPGA Interface C API 12.0 I get the following error.

Error-63105

NOR-RIO:

The "NiFpga_FPGATop_IndicatorBool_DMAFIFOtimeoutoccured" C/C++ identifier is already in use and cannot be created.

Anyone know what this means? Is there some kind of limitation on the appellation of front interface controls?

/Mola

Problem solved.

I had placed two flags with the same name on the front panel - by mistake. It builds the FPGA without errors, but the C API generator was not in favour of that.

/ Mola

-

Error FPGA - object internally in pipeline not connected to the sufficient number of nodes comments

Hi all

I'm currently implementing LMS on module FPGA of myRIO 1900. I couldn't fully understand the following error.

"Reading memory: internal pipeline object not connected to the sufficient number of nodes feedback"

Details:

"The selected object has a built-in shift register that makes the output on a particular loop iteration correspond to the entries in the previous iteration.

Connect the outputs of the object directly to a minimum number of nodes of Feedback or uninitialized shift registers. You cannot connect the outputs to another object. "

I just tried to access the values of two briefs and add them. The address for two memory values are the same, but the memories are different. I tried to implement this on SCTL, it doesn't but on normal everything in a loop, it works.

Help me understand the error.

Thank you.

Post an excerpt of your code would help us to be more confident, but I think that you run in the error described in the second note of this help documentation.

http://zone.NI.com/reference/en-XX/help/371599L-01/lvfpgaconcepts/fpga_memory_items/

Using the parameters of memory default point that you have to attach a feedback with a x 2 node latency on the release of reading to use within a single cycle timed loop.

-

How to count the pulses using RIO (FPGA)

Hello

I want to use RIO (FPGA) for counting the pulses produced by a sensor,

but I don't know how to program. can someone help me.

Thanks in advance

CAIX wrote:

Hello

I want to use RIO (FPGA) for counting the pulses produced by a sensor,

but I don't know how to program. can someone help me.

Thanks in advance

Search for example for 'Meter of RIO' finder. There are dozens of examples that should help you.

-

Resources on Rio fpga using the NI 9403 module

I use a CRIO and it works very well with my A/D and D.-a. When I add an e/s digital NI 9403 module, it eats all my resources even if I don't use all that in the circuit! Is there a way where I can use say only 2 or 3 pins e/s and not other use without him swallow all my resources.

I found the problem. When I added the module e/s I used the mode of discovery and he went. It seems it went past Scan mode for some reason any. When I moved the unit on Solution Explorer up next to two other files, I had made A/D D - A mode FPGA, he changed his mode of FPGA itself and then I could remove I/O pins as required. The icon, then changed when I pulled a PIN on my FPGA block diagram and everything was ok.

-

Hello I want to run a Stepper with 7851 FPGA R card with driver 9474 crio chasis, but I'm not able to understand how to proceed. Or may choose this option by using view lab CVI

Hi VHS.

first of all, I would recommend that you want to use materials. Basically, to control a stepper motor, you have a controller of axes and a player.

In fact I don't know why you want to use 7851 R card and cSeries 9474 module. In any case, you can connect the FPGA Board with an NI 9151 expansion chassis for

Plug the 9474.

In the following link, you will find basic concepts on control of engines with NO motion:

Motion Control fundamentals

http://www.NI.com/white-paper/3367/en

In addition, you need a software application. NEITHER offers LabVIEW - graphical programming and LabWindows CVI language - it is a system of development in C-ANSCI

for C programming.

Kind regards

RupiDo

-

FPGA output analog fastest? (RIO 9641)

Hello world!

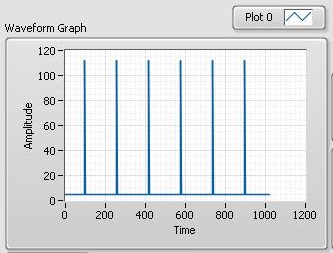

I read only analog output have about 38 tics. clock 40 MHz (RIO 9641)

My RIO gives me tics 107 = 112 - 5 analog outputs for the 1 iteration. If DAC cycle... The entire cycle takes (112 * 160 * 25th-9) for DAC 107 * 160 * 25th-9 = 428e-3 s always takes DAC, and I need more quickly.

How to set up outputs analog faster or rebuild program?I need the fastest analog output, is it possible?

Thanks for the help!

Hi togoto,.

Please let me know if I'm struggling to understand what you're trying to do, but the fastest, the analog output of the 9641 can update is 120 ticks by update. Which is based on the specification of the material on page 44 of the User Guide and the restriction that you touch. Therefore, I don't think you'll be able to get it down to 40 ticks.

Maybe you are looking for

-

Qosmio F60 - starting with Windows 7 and Dynadock U problems

I recently acquired a new Qosmio F60 and a new port replicator Dynadock U. problem, but it will not start upward unless I disconnect the Dynadock by unplugging the USB cable from the laptop. I downloaded the latest drivers for the F60 and the Dynadoc

-

Use of the HDMI on Satellite U400 (with XP)

I have not found any thread that could answer me on this subject:is it or is it not possible to use the HDMI with XP?Because I can't find the HDMI for the U400 drivers. At least not for XP. Just Vista. So is there any drivers for XP?

-

!! 0xc01a001d! 37423/101025 (\registry\machine\components\deriveddat..)

HelloWe receive the following error at startup of ideas? !! 0xc01a001d! 37423/101025 (\registry\machine\components\deriveddat..) Can not start in mode without fail & cant also roll at a time where there was no question, we rather would not have to ta

-

access to internet cx ASA cx application update / asa

ASA 5512-x, how to upgrade cx application without http proxy server? Add router between the network and management within the network, the same wlan ip router within the network?

-

Connection to the database to Oracle using Oracle Apex 5.0.1

Hi allIs it possible to connect to the Oracle (Oracle SQL Developer 4.1.1) database using Oracle Apex 5.0.1 instead of using the object browser. As he was more workspace after you have downloaded the data we have on CSV Excel.For example: regardless