Compilation of RIO Evaluation Kit FPGA

Hello

When runing, the status of compilation compilation shows 'Compilation error', but the Xilinx log is empty. Hane no idel what the problem is.

The area:

LabVIEW 2015 development professional sp1

LabVIEW FPGA compile worker 2015

LabVIEW RIO Eval Kit

Uninstalled/Reinstalled "LabVIEW 2015 development professional sp1 ',"LabVIEW FPGA mudle"and" LabVIEW FPGA compile worker 2015 ", but does not help."

Help, please!

Hi Thomas,

You might want to take a look at this post on the forum, where another user seems to have a similar problem as you: http://forums.ni.com/t5/Academic-Hardware-Products-ELVIS/fpga-compilation-error-LabVIEW-2015/td-p/32...

My guess is that this has to do with an error in download of Vivado Xilinx tools. Since you are using LabVIEW 2015, you need Vivado 2014.4. Based on your original screenshot, looks like you are using this version. Do you know if you have other versions installed on your computer? If you do, it is possible that your dll point to the incorrect reference to a different version.

I recommend to repair your installation of Vivado 2014.4. You can repair according to the installation found at the following link: http://www.ni.com/download/labview-fpga-module-2015/5492/en/

Tags: NI Hardware

Similar Questions

-

Gain setting NI LabVIEW RIO assessment Kit online.

Hello

I'm interested in using the evaluation package NI LabVIEW RIO for the implementation of a PID controller. I want to know if it is possible to adjust the gains PID controller implemented on this kit without putting an end to the operation in real time? If, for example, if the controller controls the speed of a motor continuous, can I adjust the LabView PID gains without having to stop the kit?

Umar.

Hi Omar,.

You ask about functionality to AutoFix or just tuning the PID manually? Whatever it is, you should be able to capture your PID non-stop kit.

-

Remote web panel Embedded Software Evaluation Kit LV8.6

Hello

I recently bought the evaluation of embedded software package that comes with the trial version of FPGA, RT LV8.6 90 days... and even though I have sucessfully worked through the tutorial, with the kit I came across a problem when you try to run a remote web site, Panel as it list loading 0% but never proceeded beyond this point.

After fishing trawl through many discussion forums, I came across a post that gave one of the reasons for this as being due to having a later version of LabVIEW run time engine installed on the PC - only by removing LabVIEW 2011 could I get the web to run Panel.

My question is how to manage several versions of LabVIEW if I wish (and) to install multiple versions of LabVIEW and still be able to run a command remotely through LV8.6?

See you soon,.

Helen

Hi Helen,

With LabVIEW development versions, you can disable (using the License Manager OR), but given that the engines of execution are not allowed you can not disable that.

You could try one of your LabVIEW versions running on a virtual machine, what separates them from the other.

I apologize for the problem you are having, I appreciate that it disadvantages you somewhat, but I assure you that your team of R & D to address the issue.

Kind regards

-

Hi all

I am currently facing a problem. I want to evaluate a 6 order polynom in the FPGA (in fact this function will be part of a larger VI). Here's what I put in place:Coef tab contains 7 following coefficients (from the RT):

2734.91

53.4378

-2.02666

0.0463295

-0.000588338

3.71736e - 06

-9.06681e - 09

When I sent this VI in the 2013 worker compile, I get the following error:

LabVIEW FPGA: Compilation failed due to the overmapping of the resource.

The FPGA VI does not fit on the FPGA target because the VI requires more resources

that are available.Suggestions to eliminate the problem:

Reduce the amount of logic in the VI

Reduce the number of multiplications, FIFO, or the amount of memory on the block diagram

Reduce the number of objects on the front panel

Change the settings of the arbitration

* Use Timed loops instead of other loops

* Use Timed loops for intensive resources sections of the block diagram that

do not require a loopI don't know how to solve this problem... Any idea?

Thank you very much!

TomWhat happens if you did it in a loop For? Two registers, one to accumulate the multiplications of the value of X, the other to accumulate the polynomial to offset additions.

-

LabVIEW FPGA: Compilation failed due to an error of xilinx

I'm getting a 'Compilation failed due to the error of Xilinx' you try to compile the code in LabVIEW 2013.The code has successfully compilated in labview2012. Any suggestions on what is causing this problem?

Details:

ERROR: HDLCompiler:432 - "C:\NIFPGA\jobs\THY4t7n_z6im2K7\NiFpgaAG_0000003a_SequenceFrame.vhd" line 29: Formalhas no real or default value.

INFO: HDLCompiler:1408 - "C:\NIFPGA\jobs\THY4t7n_z6im2K7\NiFpgaSetOutputDataEnable.vhd", line 37. cparametersignal is declared here

ERROR: HDLCompiler:854 - "C:\NIFPGA\jobs\THY4t7n_z6im2K7\NiFpgaAG_0000003a_SequenceFrame.vhd" line 21:Unit ignored due to previous errors.

File VHDL C:\NIFPGA\jobs\THY4t7n_z6im2K7\NiFpgaAG_0000003a_SequenceFrame.vhd ignored errors

-->Total memory use is 204688 kilobytes

Number of errors: 2 (filtered 0)

Number of warnings: 4 (filtered 0)

Number of news: 0 (0 filtered)"Synthesize - XST" process failed

Compile time

---------------------------

Introduction date: 2014/2/26 18:15

Date recovered results: 2014/2/26 18:17

Waiting time in the queue: 00:06

Compilation of time: 02:02

-PlanAhead: 01:16

-Generator kernel: 00:00

-Synthesis - Xst: 00:35Hi guys

I think I can give you a helping hand on this.

I have the same problem when I'm working on the Tutorial (2013) exercise 2 with Rio evaluation Kit.

You can try one of the following option.

Solution 1.

1. in the VI package manager.

Select 'Tools '->' Options'-> "General '->' package Installation"-> Unchecked 'mass Compile screws after Installation of the package.

Solution 2

1. in the VI package manager, uninstall the driver LCD

2. unchecked "Mass compile screws after Installation of the package" (see Solution 1)

3 reinstall the driver of the LCD screen.

Mine did after Solution 2 and the compiler works.

Hope it will be useful for you guys.

Thank you

-

Beste mensen

IK heb only tijd terug RIO evaluation kit aan een.

Die heb ik goed aan praat tariff.

IK wil nu echter some groepen student Jacques laten werken, DHS, ik heb een 2de exemplaar aan.

Het lukt me niet om setting daarmee echter you maken.

Niet met MAX, niet met LabVIEW RIO Evaluation Kit utility configuration.

Voert ik echter het eerste system weer aan, dan lukt het wel. Zelfde kabels, internet zelfde Zweifamilienhaus.

IK kan me herinneren dat ik said clean ook met het eerste exemplaar maar eerlijk om you zijn heb ik toen vanalles en nog wat geprobeerd in ik weet niet meer wat toen of Holland was.

Wel heb ik inmiddels in MAX data configuratie gereset, maar ook dat ook closer niet.

Help.

Schaffen you aan, IK overweeg tzt some myRIO, kan ik om said clean daarmee ook IK?

puts goede groet

COR van event

Hello

My problem is solved:

The evaluation of RIO package reacts different to the Windows Firewall when it is new, or when it is not new. GOLD: I guess it was the cause.

I used the RIO to my private computer system, I installed a software using MAX. This method works.

Now I am able to use it at the University as well.

Whit exactly the same hardware configuration, I used yesterday when it won't work.

COR van event

-

Hello world

I'm new to the part during a real-time/embedded Labview and I'm just starting to play with the RIO evaluation kit.

I stumbled upon a phenomenon that I do not understand... So maybe it's a stupid thing, so I apologize in advance.

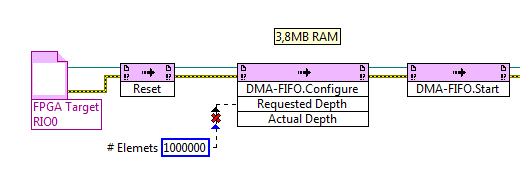

I have create a FIFO on the FPGA target (configured to Traget - to - Host DMA) and put the UINT16 5Million of a FPGA loop values, as soon as possible. Now, amazingly, I can read either with a VI on the chassis in real time, but also with an identical VI located on the PC host, even with similar performance.

In fact, I don't understand where the data are buffered and how the PC can access. I thoght the FIFO DMA memory needs to be on the RT target, right? So, how the data comes to the PC without a RT - VI? I guess that this method of data transfer (FPGA-to-PC) is not a use of FIFO, right?

In addition, when I check the property of "Possible elements" of FIFO in the PC - VI or RT - VI, I get numbers approximately 8000 to 10,000, while FIFO is configured with 1023 elements only.

How is that possible?

(Btw.: I realize that I'm losing a lot of data and the FIFO is small.) Yet, I want to first understand the points above).

The project is included in the ZIP.

Best regards and thanks for your efforts,

Joe

Hey Joe,

NEITHER offers a service called NI RIO Server. This service is installed with LabVIEW RealTime on your target in real time and allows you to connect to the FPGA of the cRIO/sbRIO from a computer.

I can't find a lot of information available on the internet, this page only:

How to make the devices to access RIO on a computer connected to the network? -National Instruments

http://digital.NI.com/public.nsf/allkb/43F81436B97AEE28862573D40069F440He is the Francis, why you are able to run the same program in real-time on the RIO and the development computer. It is also the reason why you must enter the IP address of the target in real time on the program running on the development PC. If you run the VI on the RealTime Taraget itself, it is not necessary to enter the IP address.

Some information on the size of the FIFO:

The FIFO is not only a buffer. A buffer of contains two FIFO.

A buffer is located in the FPGA itself. It is unbelievable small (1023 elements by default), but this buffer is super fast. The size of this buffer is configured as part of the LabVIEW project. You can increase the number of elements in the buffer zone, but you will never be able to achieve an elements > 20K buffer size due to the constrained resource of the FPGA.

The second buffer is located on the site in real time of the RIO. This buffer can be bigger than the buffer on the FPGA, usually 10 x or more. You can configure the size of the buffer of site in real time by your LabVIEW Code on the part in real time.

Best regards, Stephan

-

Open FPGA references change to no. target when compiled with executable in time real start

Hello again you useful forum fans! I have a problem that I hope someone can give me a hand with.

I have a project that has a Windows component and a component of the target in real time, that are running on a hypervisor type NI PXI-8110 system. Communication both sides between them using shared variables.

On the real-time side, I have four FPGA targets who are reading and writing various analog and discrete inputs and outputs. I several periods loops which opens a reference to one of the FPGA targets during the first call, then pass this reference in several subVIs that read and write to panels prior to the FPGA. The loops the FPGA reference thus made available and reuse it in the next iteration through the shift registers. Each FPGA target has only a single reference open to him. One of the loops is using the FPGA reference directly and does not pass it in any subVIs.

It all works very well in the development environment, I can read and control inputs and outputs FPGAS via the front panel of the application of the side Windows. It also works very well if I start the game real time in the development environment, and run the code of windows as a stand-alone executable file.

However, when I compile the code in real-time in an executable startup and deploy it to the target, it does not work. I enabled debugging on the executable, and when I connect to it via the operation-> debug executable in the menu, I see an arrow broken at execution. Further investigation shows that each of the four open screw reference FPGA is now empty, the text under them is "no target" and the thread for reference on their part to my first Subvi is broken. I need your help to understand how to operate as it does in the development environment.

I followed the instructions of these two knowledge base articles to compile and download the bitfiles FPGA on the FPGA target and execute on start or restart:

http://digital.NI.com/public.nsf/allkb/39795847AC67296D862575FB0046944F

http://digital.NI.com/public.nsf/allkb/BC513C2A0DC29C89862574BF0002B0B9?OpenDocument

Open FPGA reference screw are configured for the FPGA to build specifications that I created for each target in the LabVIEW FPGA project.

I called technical support, NO phone, and yet were able to determine this one out, so additional "brownie" points if you do!

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.Please let me know if you have any ideas regarding what is happening! I appreciate it.

Jon,

I'm always up for the challenge. Have you tryied recompile the FPGA VI that accesses the RT VI? I also suggest to try and open the bitfile instead of the FPGA VI. You run in dynamic mode (this is not a suggestion, it's just a question)? There is no difference if you try to open the FPGA VI reference outside the while loop, then past the reference to use inside the while loop without shift registers, then close the reference to the FPGA VI outside the while loop?

Let me know if these suggestions makes no difference.

-

Hello!

How can I compile a code to the FPGA without hardware. I just want to see something on my FPGA BRAMs. If I compile code to FPGA with actual hardware, it takes too much time.

Best regards

HITMANNN wrote:

If I compile code to FPGA with actual hardware, it takes too much time.

As long as you have defined your specific material in the LabVIEW project, you can compile your FPGA screw with or without connection, but in all cases, it will take the same time to compile. Compilation of FPGA can be a lengthy process.

-

VI FPGA is broken in example Robotics Starter Kit is copied.

I use LV 2010 and I play with the example of 'Roaming' Robotics Starter Kit. When I open the Starter Kit project directly from the Finder "example" and look at the FPGA code, everything is fine. However, when I do my own copy of the project (by performing a save under, select duplicate .lvproj and content), there is a problem with the FPGA code. If I open 'Starter Kit FPGA VI.vi' I get a broken arrow. Some FPGA IO references seem to not completely defined. Screenshot see attachment. I also note that the reference to the wick of FPGA (in Roaming.vi) always points to the original location of the bitfile in LabVIEW 2010/examples, rather than follow the new copy of the project. Can someone tell me why this is happening and how to fix it so that I can edit / rebuild the FPGA image. Note: I also installed LV2009, and I'm sure that I was able to do this in the past.

Problem solved... sort of.

Don't know why save it under did not work, but it seems that the 'Correct' to get a working copy of the Starter Kit "Mount" app is to use the new option 'Project Probotics' of the screen to start LV.

This is made most obvious from the portal "LabVIEW 2010 Robotics", but it is also available from the portal "LabVIEW 2010"standard if you dig into the choice of 'New project'.

PS: 'Portal' is probably not the right word, but I don't know what to call different 'flavors' of LabVIEW.

Phil.

-

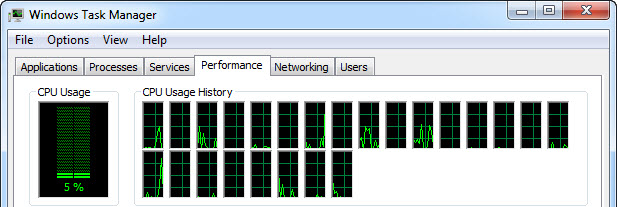

Force the worker compilation to work faster

The process of creating the FPGA bit files takes a long time even with a simple FPGA design. I followed the system resources, when the worker compile creates the file bit. Only a few percentage of the CPU is being used. Is there a way to force works Woker compile faster because there are available system resources?

My system is dual Xeon 6 physical cores with 16 GB of RAM, running the version of LabVIEW 2011 90 days come with the single-board Rio evaluation.

FPGA code compilation is performed not by the compiler to the LabVIEW but a compiler of Xilinx, specific to their FPGA chips.

The problem you see is the compiler of Xilinx is a single thread and so will not use the base and can also sometimes be seen ' hanging out '. There is nothing you can do to push the compiler to redouble our efforts by encouraging the use of other resources. If you carrots be 3.2 GHz each, then compile on your dual Xeon 6 will be no faster than on a single 3.2 GHz processor.

What you need to reduce your compile time is the fastest core, you can get!

-

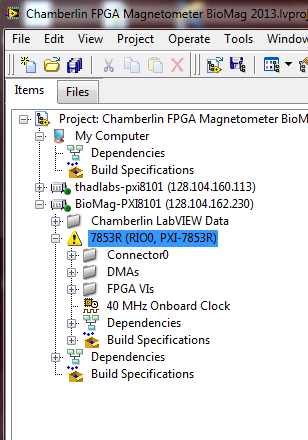

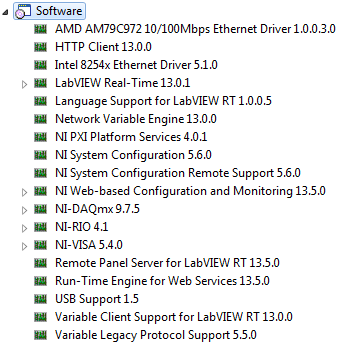

Software FPGA with LabVIEW 2013

I have a system with a rotating computer "development" under Windows 7 and an NI PXI-1036 chassis with a PXI-8101 controller as well as a card FPGA PXI-7853R. Recently, I upgraded to LabVIEW 2011-2013 of LabVIEW. I kept LabVIEW 2011 installed just to make sure everything is still working on the new LabVIEW.

Now, when I open my project in LabVIEW 2013 Project Explorer, my FPGA comes with a warning triangle yellow next to him (see attached photo). The warning says:

"Software support for this target FPGA is not installed on the computer. You can view and copy elements into the project, but you can not compile any screw under the FPGA target, until you install support for the target. Refer to the documentation of specific material for more information on the proper drivers and for more information about the installation and configuration of the target FPGA ".

Regarding the installed software, I have LabVIEW SP1 of 2013, 2013 of LabVIEW FPGA Module SP1, SP1 of Module 2013 LabVIEW Real-time, and Xilinx Compilation tools 14.4. On the chassis of the TARGET (with the PXI-8101 controller), I have attached a list of installed software.

Interestingly, when I open the project in LabView 2011, no errors or warnings are present with the FPGA card. It is only under LabVIEW 2013 I see the warning. Did anyone see a glaring omission of software that could be the cause of LabVIEW raise this error? Thank you for your help.

Best guess is that're missing you the driver for your FPGA device. Try to install the latest version of NOR-RIO (or at least the version supplied on your 2013 SP1 install disks). Have you installed device drivers at the time that you have installed SP1 2013 LabVIEW?

-

HELP - FPGA SPARTAN 3E-100 CP132 WORKS WITH LABVIEW FPGA?

HI EVERYONE, GET ON IM TRYING TO USE MY FPGA WITH LABVIEW, BUT I DO KNOW THAT IF ITS COMPATIBLE, I INSTALLED THE DRIVERS, MODULE FPGA AND LABVIEW 2012, IM USING WINDOWS 7 32 BIT, AND AFTER I COMPILED ITS SAYS:

LabVIEW FPGA called another software component, and the component returned the following error:

Error code:-310601

NOR-COBS: Impossible to detect the communication cable.

Check the communication cable is plugged into your computer and your target. Also, verify that the proper drivers are installed.Thank you.

=)

Hi dvaldez2.

LabVIEW FPGA offers no support for any material to third parties, other than the 3rd Spartan XUP Starter Kit. These are probably the drivers you downloaded.

http://digital.NI.com/express.nsf/bycode/Spartan3E?OpenDocument&lang=en&node=seminar_US

However, this driver supports only the Starter Kit Board itself (http://www.digilentinc.com/Products/Detail.cfm?NavPath=2, 400, 790 & Prod = S3EBOARD). You may not use the driver with any other Xilinx FPGAS.

I hope this helps.

-

Hi, just got my new cRIO-9067. I have converted my project over the cRIO-9067 since the cRIO 9074. Same layout module, same engine, same scan code custom fpga, (hybrid mode). I have no problem of compilation for the 9074, which is a lower performance FPGA architecting the 9067 FPGA.

The final timetable for windows compilation shows that the timing is respected for all clocks - 40, 80 and 120 MHz (I use a clock derived for some code sctl). During the end of compilation, during the phase of gen bitfile, I get the dreaded time violation. Investigation of the breach indicates that it is not the custom code, it is not schema components. One of them seems to be linked to the card series OR 9870 I in the chassis.

Why? Is there anything I can try with the compiler directives for this problem? You would think that it would be easier to compile for the highest performance FPGAS...

OK, don't ask me how I thought this output - to run I changed nothing else than this: feed the I/O node a reference FPGA of e/s instead of configure the node via the menu "link to. It makes no sense, but the compilation succeeded when I did this.

I know it is because I created a very simple test VI in my project and made sure it does not compile without it.

-

How to implement Canopen on FPGA to run the engine using NOR-9881?

Dear,

Your support will be highly appreciated,

There is only one available for NOR-9881 example.

Please note that the following materials were properly connected:

cRIO-9024, cRIO-9113, OR-9881 and motor Nanotec (SMCI36 against L2818L0604-T5X5), the following

sites Web shows the engine Nanotec in details:

http://us.Nanotec.com/products/660-L28-linear-actuators-with-trapezoid-spindle/

http://us.Nanotec.com/products/1041-SMCI36-stepper-motor-and-BLDC-motor-position ing-control /

The main problem is how to configure the inputs and outputs, where, in most examples, the entry and exit have been automatically

configured.

the following three examples and I wonder how to start:1 - example Nanotec: dependent VISA controls for data transfer

http://us.Nanotec.com/support/application-notes/LabVIEW-example/

2 - reference example CANopen for series C OR - 9853 Module CAN:

the NOR-9853 has default Can0 which was used in the codehttp://zone.NI.com/DevZone/CDA/EPD/p/ID/6093

3 - from finder labView example: search for 9881 then choose

NOR - CANopen_cRIO.lvproj, which depended on SDO orders for transfer orders

The attached picture shows that NEITHER-9881 can be seen, after compilation and

loading the bitfile FPGA.

Please, please advice me:

1. how to start?

2. how to create variables of entry for NI9881?

3. how to implement CANopen mode FPGA? where there is no CANopen palette.Thanks in advance and

Hello!

From my understanding, the 9881 can be treated from the FPGA, but only from the application of the RT. I think that the point 3 of your post examples of the use of the module fine.

Kind regards

Georg

Maybe you are looking for

-

Why is Mozilla trying to Mougeot Internet Explorer?

With each update to Mozilla Firefox you seem to do it more like the Internet Explorer which IS NOT of WORK TO START WITH and more time passing, you're now with Google Chrome, trying to IE Mougeot. Chrome has load a dangerous Script when it is on an h

-

When I activate the WEP security on my router (belkin F5D7630-4 (a) and on my laptop (satellite p20 801) I can no longer connect to the router. I tried 64 & 128 bit encryption, I've also updated the firm ware on the router, no luckusing an atheros AR

-

Upgrading memory Sodimm DDR3 in my PAvilion dv7 - 7023cl

Hello I want to upgrade the memory of my laptop Pavilion dv7 - 7023cl. Now I have two modules sodimm Micron; one of the 2 GB 1RX8 PC3L - 12800S - 11 - 11B 2. I would like to know if I can replace it with a 8 GB Super Talent Module that has the follow

-

I have an AMD Athlon 64 processor and have tried to install XP Service Pack 3 twice. After installation, my computer crashed and required a system restore. How can I install XP 3 without crashing?

-

My Aspire S7 stops responding for a few seconds from time to time, randomly

Aspire i53317 S7 256 G (2 * 128) When using, the system stop meet occasionally for a few seconds, sometimes more than 10 seconds, click of the mouse and keyboard does nothing, while it is happening, after it is passed, it works very well for a random