programmatically launch compilation FPGA

Hello!

I would like to launch FPGA compilationS during the night. I thought to build a tool based on the API project that would launch the process of compilation (like click - right-> compilation). With this API, I can find the VI but I have not any method to start the compilation. A solution would be to run the VI to start the process of compilation and then abandon exec when the VI is running (this means that the compilation is successful) (?), but it requires that the target is connected to the computer in order to deploy the bitfile.

Is there a throw by program compilation in the same way as the click - right-> compilation?

Normal 0 21 false false false FR X-NONE X-NONE MicrosoftInternetExplorer4 / * Style Definitions * / table. MsoNormalTable {mso-style-name : « Tableau Normal » ; mso-tstyle-rowband-taille : 0 ; mso-tstyle-colband-taille : 0 ; mso-style-noshow:yes ; mso-style-priorité : 99 ; mso-style-qformat:yes ; mso-style-parent : » « ;" mso-rembourrage-alt : 0 cm 5.4pt cm 0 5.4pt ; mso-para-marge-haut : 0 cm ; mso-para-marge-droit : 0 cm ; mso-para-marge-bas : 10.0pt ; mso-para-marge-gauche : 0 cm ; ligne-hauteur : 115 % ; mso-pagination : widow-orphelin ; police-taille : 11.0pt ; famille de police : « Calibri », « sans-serif » ; mso-ascii-font-family : Calibri ; mso-ascii-theme-font : minor-latin ; mso-fareast-font-family : « Times New Roman » ; mso-fareast-theme-font : minor-fareast ; mso-hansi-font-family : Calibri ; mso-hansi-theme-font : minor-latin ;}

Hello zyl7,

Thanks for posting on National Instruments.

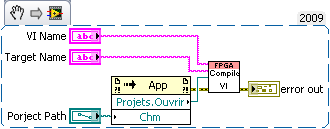

I have attached a VI do. I used the API for compiling screw FPGAS and especially the niFpgaCompileVI.vi of VI:

Tags: NI Software

Similar Questions

-

Hello

When compiling a fairly basic FPGA VI, I get the following error:

61332 error occurred in niFpgaCompileWorker_ProcessStatusPipe.vi:1<><>

Possible reasons:

LabVIEW FPGA: An unexpected error occurred with the build tools. You try to compile the FPGA VI again could solve the problem.

The length of a line in "NiFpgaAG_0000002e_WhileLoop.vhd" is too long for xilinx 10.1. Length: 32845 Max length: 4150

Departure time: 17:22:06

End time: 17:22:12

Total time: 00:00:06Apparently, the vhdl code generator OR forgot to add some CR + LF in the intermediate files. How to work around this bug?

Kind regards

Lukas

Hi Lukas.

When LabVIEW compiles a VI, the VI is converted into virtual hard disk to be compiled into a file bit by Xilinx. As you have already understood, this error indicates that a line of code vhd had a length of 32 845 characters, which exceeds the maximum length of 4150 characters for the Xilinx 10.1.

Although 32 845 characters is very long, it is possible that this is due to the codification of LabVIEW rather than a bug. Some common causes of this problem include large enums, a matrix, or clusters in the code. Please check in your code. If you have no luck, please attach a screenshot of the code. I hope this helps!

Kind regards

Dayna P.

Technical sales engineer

National Instruments

-

Hello

I create a desktop using the CreateDesktop() API, in this office, I launched a MFC dialog with text field box in this topic.

I want to get the keyboard touch screen when I touch on the text field of the dialog box.

I tried to use the following information

https://msdn.Microsoft.com/en-us/library/Windows/desktop/dd371581%28V=vs.85%29.aspx

but the key Board launched when I touch the dialogue instead of text field.

Please give me the solution?

Pramod Hello,

Thanks for posting your question on the Microsoft community.

This question fits better to the developers on MSDN forums.

I would recommend posting your question on the MSDN forums.

MSDN forum

https://social.msdn.Microsoft.com/forums/en-us/home?category=windowsdesktopdevThank you

-

programmatically launch a file with the default windows application

I thought it would be a trivial task, but I can't seem to be able to find something about it. I would like to be able to open any file in the native application - as if the user has double-clicked on it. Any suggestions?

Joined a VI I use that does what you want. If the given path is a folder, then it opens a file Explorer window in this folder. If the path is a file, then it opens the file, as if the user double clicked on it. She uses the mentioned command-line function previously.

-

How can I programmatically launch a VI on the RT tgarget host

Hello:

using an older version of labview (I guess that Lv 2009) I developed a proposed acquisition of cRIO and storage target data in windows pc. In main Vi running on target RT, I wrote a procedure to initiate a VI on pc to record data. Attacched the part of the code. I remember it worked normally, but trying to do the same on the new pc with controller Lv2015 and NI 9067, this does not work and I can not open VI.

Anyone have idea for this behavior?

Thank you

Antonio

I solved the problem in allowing access to the RT target on the Server Option-VI page

-

Programmatically launch the photos app?

I would like to invoke the photos app, but I don't quite know what to spend in Invoke. Is it possible to do?

Answered my own question and I wanted to share:

Invocation media = new Invocation(); media.setID(BlackBerryContentHandler.ID_MEDIA_CONTENT_HANDLER); media.setArgs(new String[]{BlackBerryContentHandler.MEDIA_ARGUMENT_VIEW_PICTURES}); Registry.getRegistry(getClass().getName()).invoke(media); -

Question of server FPGA compile

Hello

I want to implement a system of compilation farm. There is only a PC development (possibly 1 later) and compiles a worker. The question is, the compile Server (one which dishes to the worker of the compilation of the tasks) possible on the same PC used for development, and in the affirmative, he introduced the bottleneck important compared to using a dedicated machine?

Thank you

Hi ToeCutter,

The compile server can be on the same PC that is used for development without any problem

' ' ' ' Refer to the getting started with the FPGA document compile farm, available by selecting Start "all programs" National Instruments "FPGA" start-up of the farm to compile FPGA, for more information about configuring and using FPGA compile farm.

Use "localhost" as the host name of the server for your compilations to compile.

Compile farm server uses the same compiling installed tools (Xilinx) on your PC, but instead to directly obtain the LabVIEW project files

It compiles the files downloaded by the user, there is no difference in performance.

I hope that helps!

Kind regards

-

Hello

I can generate a C API interface for FPGA design in Labview Communications.

And how does it work?

Thank you

Sebastian

Hi Sebastian,.

If it is anywhere in the LabVIEW Communications, he'll be in tools Launcher. If it is not there then you can still generate a C API for your FPGA using the FPGA Interface C API generator. I received this the generating a C API for a help Application LabVIEW FPGA Document.

Generating a C API in the Windows Start Menu

Follow these steps to generate a C API for a bitfile compiled in the Windows Start menu.

- "" "" Select Start "all programs" National Instruments "FPGA Interface C API" FPGA Interface C API generator.

- On the Generator of API C FPGA Interface dialog box that appears, navigate to the compiled FPGA bitfile or type an absolute path for her.

- Select a directory for output to the C API. If you do not select an output directory, the files in the C API will be created in the directory that contains the bitfile. You can navigate to a directory or type an absolute path for her.

- Optionally, you can change the prefix for the generated files and constants in the generated .h file.

- If you are using LabWindows/CVI to develop your C application, check next to exclude NiFpga.h/NiFpga.cas FPGA Interface C API installs the header and library files with the support of LabWindows/CVI.

Make sure you have installed FPGA C Interface API .

Introduction to the API of C Interface of FPGA

See you soon

-

Launch by development OI program

Is it possible to programmatically launch the development of a standard IO (as if I double click the icon of TestStand)? I could of course do this with a system running call, but I'm curious to know if it is feasible for a real TS API call.

It is not an API call for it. Your best bet is to call from the command line as you suggest.

Kind regards

-

Broken the FPGA VI but the empty error list

Hello!

I'm trying to run a vi which includes a 'Open FPGA VI Référence' function. However, an error and it says that "not compiled FPGA VI. When I try to compile the FPGA VI a message saying "The VI is broken". I try to run the FPGA and when appears in the error list, there is no error or warning in the list, although the name on the fpga includes the Red 'X' ('show warnings' is checked). Any help?

I'm using Labview 2013.

Pablo

Hi Pablo.

Sorry for my delay in responding, you managed to get the respected FPGA.vi yet?

To answer your questions, if the project is ok with an empty FPGA.vi, then in theory, your hardware is configured ok. However, due to the vi being blank, you haven't tried to use one of the modules on your system, so it can introduce errors. The most common mistake is differentiation of mode Scan Mode/FPGA by installing the project in the first place. Also be aware that not all FPGA targets supports everything, for example some dislike for the rows that have an index to calculate the number of iterations, rather than a constant wired at the entrance to "n".

Out of curiosity, why you place every measure in the DMA separately and also specify address? Is there a reason you don't just place all the measures in a table and put everything in the DMA, then divide the table on the other side?

Generally speaking I don't think that incorrect programming should never cause LabVIEW crashing and you should always report the problem to the OR in order to take a look and see if they can fix it.

Hope that you managed to get your problem sorted and again sorry for the late reply.

Darren.

-

FPGA project daily Software development management

I noticed that every day when I finished the work on the project and take a copy of this project and rename it to serve the next day and open FPGA vi in the new project file, Xilinx begins once again compiling FPGA VI. Is there a method that I could manage my daily work so the next day, I opened the FPGA VI of new folder, it will not ask for another compilation?

Kind regards

Austin

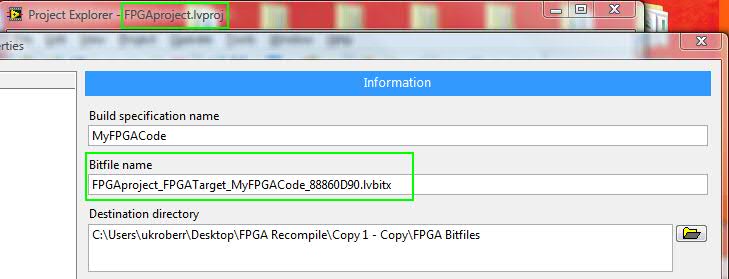

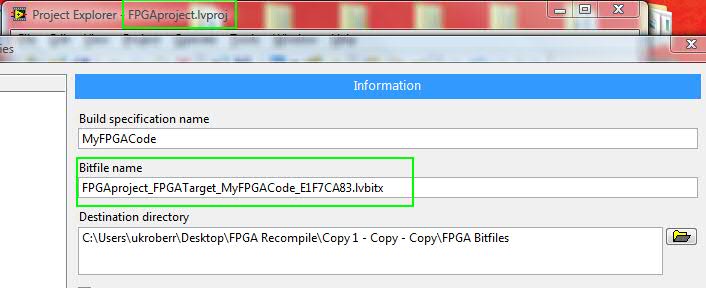

Hi Austin,.

I reproduced the problem as follows.

(1) create a folder and save a new project inside

(2) create a FPGA target in the project(3) create a simple FPGA VI under the target

(4) create a specification to build for the FPGA and compile it.

(Note that the automatically generated name to the bitfile)5 *) copy the folder with everything (folder project, FPGA VI, bitfile, alias, etc.) to another folder

6 *) try to run the VI freshly copied directly under the target FPGA (it will start to compile)Reason: The name of the bitfile you specify (in the build specification) has changed to a new name that didn't exist not before, so try LabVIEW compiles again.

Here's my spec to build the original project...

Here are the specifications of the copied project...

If you replace steps 5 & 6 with 2 steps, it seems to prevent the recompilation.

5 *) copy the original file with everything in it

6 *) this time, change the name of the bitfile in build specification copied the same as the original name of bitfile (see step 4)

Run the FPGA VI and you will notice that you will not need to recompile this time.Thanks for your time,

-

When I look at my compilation report for my code FPGA on a PXI-7833R. I see the settings below. They are all listed separately. However, I thougth a slice consists of the register and LUT, isn't it? Records of slice and Slice LUTs explain just more Total slices? If so, I don't see how the calculation works in my attached compilation report.

Total slices

Records of slice

Slice LUTs

Block RAMs

jyang72211 wrote:

The total range is therefore to what I'm looking for in terms of capacity, right? Let's say I

Total installment: 100%

Slice the registry: 60%

Slice LUTs: 60%

I must conclude that my FPGA is full, even if a few slices are not entirely uttialized. There is no way to make the FPGA using these partial slices, right?

No, still not quite right. The compiler FPGA constantly optimize once all adapts and responds to the timing (or it determines that there is no possible way so that everything fit). If you add more logic to your design, the compiler may be able to do all this in shape, although the compilation will take more time.

Even more confusion, if you're just on the edge of what you can adapt, sometimes the compilation will succeed and other times, it will fail for exactly the same code, because the compiler (really the place-and-route step) uses a random starting point to place the logic.

For a very simplified analogy, let's say you have a collection of triangles (registers) and squares (LUT) that you want to stay inside a piece of paper. If you have only a small number of triangles and squares, you can put them anywhere. The numbers are rising, you must arrange to pack them more closely, and when it starts to get very tight, you may have to try several times to make it all be adapted. That's what makes the FPGA compiler, with additional restrictions on where the logic can be placed due to delays.

-

Flex skins - compile time or not?

Hi, I'm sorry if this seems to be too simple a question, but I have searched and I don't even know if I'm looking for the right words to ask the question with. Put as simply as possible, if I develop a skin for an application that will give us our customers that they will have to recompile the application to change the skin or will they be able to put a new skin in the app, after that it was compiled and published? The skin embedded in the app or he is detained separately? Is there a difference between using chart vs skins programmatically at compile time? Thanks for any help you can give me, and Happy New Year!

The application can use a compiled CSS file and load at runtime, but the app must be set to use it before it is compiled. Then you can swap the swf with a new one and it will work as long as all the style names and assignments of style are the same as the old. You cannot add a SWF with skins to an existing application without setting up the first and the application is compiled.

-

How to debug the program Labview that runs in the target of the RT of a Compact RIO

I use CRIO-9073 for the acquisition of data from sensors. Program Labview is written in RT target and target FPGA. It is posssible to make step wise execution for the program written in the target RT and FPGA target the way purpose us for the debugging of the program in general OS.

MJM,

The only way to use the debugging on a VI wrote to FPGA tools is to simulate running on the host computer. You can then deploy the compiled FPGA code on the target and run your VI RT in debug mode if you use the communication of the façade with the host PC.

-

"App: unplug the slave" method

I tried to use the ' App

slave isconnect "method on a project with a goal of RIO (MyRIO) currently connected and the method completes without error, but it does not cut the target in my project. I tried to play, selecting items in the project window and making even the project window above and active before you make the call without success.

slave isconnect "method on a project with a goal of RIO (MyRIO) currently connected and the method completes without error, but it does not cut the target in my project. I tried to play, selecting items in the project window and making even the project window above and active before you make the call without success.How this method is intended to be used? What happens if I multipl target in my project?

OK - this issue initially came from a position of LAVA and I'll copy paste the answer I posted here even IF not all relevant here in case someone else needs!

I played a bit more with the feature today and it really seemed that the invoke node called "App: unplug the slave" had to be called in the aim of RT himself to work, as that proposed on the forum of NOR. Then, I tried other tests to see if it is possible to run a VI directly on an RT target (which is located in your project). At first, I thought that it was not possible and that he could not understand until I found this link: http://forums.ni.com/t5/LabVIEW/Loading-and-Running-a-VI-on-a-cRIO-from-a-PC/td-p/796657 . I think that gives you actually your solution by explaining that each target has its own instance of the application (also the search to 'Work with Instances of application', as a 'Concept' in the help file for LV [2014 in my case]). Is the way to acquire (or at least my way because I couldn't directly give the IP address of the RIO) was:

-App-> Project.ActiveProject->-> [appropriate Index] targets-> Application-> "disconnect from the slave.

Notes:

-"Project.ActiveProject" seems to be a scripting (bottom of bue) VI

-The property node 'Application' is located near the end of the list

Silently, it disconnects the cRIO and may be able to delete your popup if done shortly after asking the RT to restart. With the same reference App, you can also programmatically launch a VI to the target host (even by pressing the arrow to run with cRIO selected target.) It could certainly be useful for you too if you need delay the restart to stop the pop up. I want to say, deploy your application for CompactRIO with the "Run As Startup" active, then get the reference of the App, and run a simple VI that resets the CompactRIO after a few seconds late. During this time, call the node to invoke 'Disconnect the slave' and your pop up should be gone...

Let me know if it works for you!

Maybe you are looking for

-

Need driver for Satellite 2515CDS

Hello I'm not that computer savy and have this old laptop with the music I want to transfer to a USB key.There is a USB Port but no driver installed.You can direct me to the correct driver? Then, I need to use the dialing until can you believe to ent

-

We use the NI 4551 map, which is obsolete. This card is interfaced with NI 6023 E. We would like to replace the 4551 with the last card of NEITHER. Can you suggest the replacement of 4551 which works with 6023? Is it recommended to change the 6023 E

-

I am running XP with SP2 and downloaded IE8 yesterday. I searched the support pages and found the following information in my system. Under "Internet settings" files named "iecont.dll' and 'iecontlc.dll' are reported missing in the part of 'Version

-

Microsoft office home and Student 2007 installs whenever an attachment is open

I am running Vista Home Premium SP2 on a new Dell computer. I have installed Office 2007 Home and Student after I got the computer without obvious problem, but now whenever I try to open an attachment or use Windows Explorer to open a document file,

-

Suspended email to blackBerry Smartphones

Hi, I hope someone can help me. I own a Torch 9800. Recently the curve of my little brother began to act up. I didn't know if it was his camera or its sim card, which had some problems, so I put her sim card in my torch for a while know. When I put t