Question of server FPGA compile

Hello

I want to implement a system of compilation farm. There is only a PC development (possibly 1 later) and compiles a worker. The question is, the compile Server (one which dishes to the worker of the compilation of the tasks) possible on the same PC used for development, and in the affirmative, he introduced the bottleneck important compared to using a dedicated machine?

Thank you

Hi ToeCutter,

The compile server can be on the same PC that is used for development without any problem

' ' ' ' Refer to the getting started with the FPGA document compile farm, available by selecting Start "all programs" National Instruments "FPGA" start-up of the farm to compile FPGA, for more information about configuring and using FPGA compile farm.

Use "localhost" as the host name of the server for your compilations to compile.

Compile farm server uses the same compiling installed tools (Xilinx) on your PC, but instead to directly obtain the LabVIEW project files

It compiles the files downloaded by the user, there is no difference in performance.

I hope that helps!

Kind regards

Tags: NI Software

Similar Questions

-

FPGA compile Server Corruption

Background:

I have an installation of Windows 7 64 bit running on an i7-930. In Oct. I installed LabVIEW FPGA 2009 SP1 build server from a copy of the .iso image of NEITHER.

In addition, I have VMWare Player installed with the full development suite installed, targeting the server hosts compile.

We book this system into 'production' for the 3 months preceding the feast of the new year...

Question:

When I returned from vacation, not a single machine in the factory can hit the compile server on Win7 host, including installed VMWare LV tools running on the same PC. It seems that the clock carried over from 2010 to 2011, and the compile server went poof! Initially, the compile Server complained that Xilinx tools license had expired. Once I reinstalled the server compilation, nothing can connect to it, not the server errors, delays network comes from the development tool.

Troubleshooting:

Obvious things:

' 1) ' reboot ' on the VMWare image and host; no change,.

(2) double check anti-virus is disabled; no change,.

(3) check the Windows Firewall is disabled; no change,.

VMware, other servers in fine compilation on the work of the other PC on the network (for VMWare isn't the issue, but played with bridged vs NAT anyway; without change).

VMware, the 'local host' compiles Server works very well (remember, it's that of virtualization, it doesn't have the VM host on Win7 version).

Reinstall the server compilation; no change.

But here's where things get funky. The IVR folder with the compile server has only a handful of files it contains with no record. On the other compiling work servers, IVR file is loaded with support files files. It's as if the installer does not install all the files right...

Copy IVR system folder of work on top of the half installed folder; no change. Bluff installation and start fresh with another to continue troubleshooting (this has been done a lot)...

Do the various Registry hacks to take away the remains of uninstall process and align with the work of compiling server machines registers; no change.

Walked through the Knowledge Base of NI.com and Forums. Several issues that either I solved with relocations, left unanswered, or have been resolved without getting clarification on exactly what happened or how to fix it.

A run the TList hack manually (difficulty TList.vi does not unless you have the run-time installed LabVIEW and my Win7 OS host does not work). no change.

Hunting the Perflib fix rabbit in this hole; no change.

Next steps:

Will try to install it from another copy of the DVD LVFPGA in case my .iso image have fried or 'cleaned' by McAfee.

Any ideas? I would like to avoid reimage your computer for a number of practical reasons, including not seen the Win7 install DVD without invoking the wrath of it, tape / associated explanations invoking it or the huge amount of time lost in this process (and the square itself)...

I saw a funny similar behavior when you use a server remote compilation when VMware gets thrown into the mix.

My specific case was:

Windows XP (32 bit) Welcome + to compile the server

Reviews of Windows XP (32 bit) + LV development system (bridged network operation)

Under certain conditions (I couldn't understand what was the trigger), LV development system could not connect to the server for compilation. Boost LV and even the virtual machine it ran into would not solve the issue. Moving the server to another physical machine compilation does not resolve the issue.

All firewalls was extinguished without a change in behavior.

I ended up resorting to statically assigning the port that the server remote compilation using this KB works on:

http://digital.NI.com/public.nsf/allkb/BE02DC97330CD1D8862576A500015AB8

Once set, all my LV development environments have been configured to use static port. I have not seen the problem since. I think there may be some problems with Service Locator of NEITHER when dealing with VMware.

It doesn't sound like you are experiencing exactly the same problem, but this can give you more options to try.

-

Why is the FPGA Compiler server so slow?

FPGA Cloud compiler is faster because NO servers are performing, right?

Well, my Windows 7 PC is powerful, but no luck there!Total CPU utilization is never more than 25% and the total memory (including other applications) usage is less than 16%.

Why, the compile Server uses all available resources? has been restricted?

How can I leverage more power from my PC?If servers OR compile faster code, there must be a plausible explanation / reason?

Please indicate, how to make the compile server running faster in place?I don't know what machines compilation cloud service works, but I do not.

It seems that the compilation is much faster on a Linux machine on a Windows machine (I think I've heard up to 30% faster). The Linux FPGA compile server is available for LV2012. Set up a Linux machine with a clock high enough CPU and RAM speed and you will get on the fastest possible compilation with current tools.

-

Question of FPGA compile farm 2012

I was under the impression that my FPGA LV code can be compiled by several workers when I bought and installed the FPGA compile farm Toolkit. What I have, however, is that each work of compilation can only be compiled by a worker. I expect that a single compilation work can be divided by the number of workers.

So I see that a worker of computers will compile two computers of worker work. It's just that a worker will be compiled at the same time.

I just misunderstand the features to compile farm Toolkit or is it an installation problem?

Thank you

No, a unique compilation cannot be shared between workers. Nature of the beast-FPGA "compilation" is not something that lends itself to parallelism. You have the advantage that the build tools run much faster under linux, however.

-

tables of fixed size in FPGA compilation error - how to implement a waveform control in an FPGA?

Hello

After being stuck for two days, please let me briefly describe my project and the problem:

I want to use the cRIO FPGA for iterative control of waveforms. I want to capture a full period of the waveform, subtracting a reference waveform period and apply control algorithms on this. Subsequently the new period of correction must be sent again for the output module OR. If it does not work, the captured waveform will look like the one reference after several iterations.

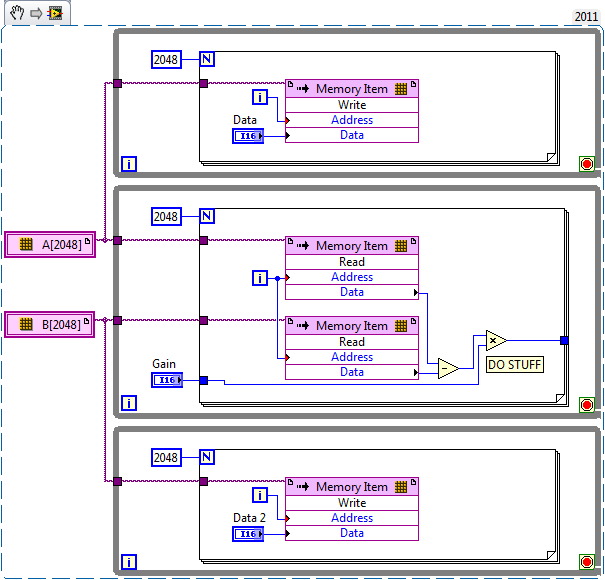

I am planing to create an array of size fixed for the capture and the reference waveform (each around 2,000 items for a given period). I use so 2 paintings of each elements of 2000. I use the function 'replace the subset of table' to update each element captured in the loop sampling and a feedback for each table node to keep in memory (I also tried shift registers, but then the berries do not have a fixed size any more and I can't start the compilation process).

If I try to compile the FPGA vi, I get the following error:

Details:

ERROR ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

"Synthesize - XST" process failedBefore I added berries to my code I could compile the FPGA without problems. So, it seems that the tables are too big for the FPGA. :-(

Therefore, I would like to ask if there is perhaps a better method to implement my problem in LabVIEW FPGA? How could avoid the tables to save my waveforms on a period?

Thanks a lot for your help in advance.

Best regards

Andreas

Unfortunately, the LabVIEW FPGA compiler cannot deduct stores shipped from berries (yet). When you create these two large paintings, you are creating essentially several registers very, very large. Just by looking at your picture, I guess that there are at least 4 copies of each of the tables.

You want to use LabVIEW FPGA memories instead. You can create memories outside the loop and then read/write them where you are currently referencing the berries. The only change that you really need to do is to break down your treatment in scalar operations. I have attached a simplified version of your plan, I hope it helps. Let us know if you have any other questions.

-

FPGA Compilation fails because of the mistake of Xilinx

My FPGA compiles and I cannot understand why. There is nothing crazy in my FPGA VI of really, it seems strange to have this type of problem. I can't reach the code because its owner, but it's pretty simple because it reads all channels from a single module and records them in a data FIFO. I have compiled successfully any FPGA code on this computer, so I should definitely have everything needed to compile.

My system consists of one NOR cRIO 9030 with a single module 9220. Below is the Compilation of summaries.

---

LabVIEW FPGA: Compilation failed due to an error of Xilinx.

Details:

ERROR: [Synth 8-1031] knidmahighspeedsinkbase is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:295]

ERROR: [Synth 8-1031] knidmahighspeedsinksize is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:296]

ERROR: [Synth 8-1031] knidmahighspeedsinkbase is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:301]

ERROR: [Synth 8-1031] knidmahighspeedsinkbase is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:302]

INFO: [Synth 8-2810] pkgshimswitchedlinkdmaportifc unit ignored due to previous errors [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:68]

---------------------------------------------------------------------------------

Development of finished RTL: time (s): UC = 00:00:07. delay = 00:00:31. Memory (MB): peak = 798.605; gain = 204.203

---------------------------------------------------------------------------------

ERROR: [Common 17-39] 'source' is not due to previous errors.

INFO: [Common 17-83] release license: synthesis

3 info, 0 Warnings, 0 critical warnings and 4 errors.

synth_design failed

: ERROR: [Common 17-39] 'source' is not due to previous errors.When running

«source - notrace.» /. Xil/Vivado-6035-ip-10-60-203-176/realtime/toplevel_gen.tcl ".

called inside

«synth_design-top "toplevel_gen" - part "xc7k70tfbg676-1"-"full" flatten_hierarchy "»»

(file "/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/synthesize.tcl" line 21)

called inside

"source" / opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/synthesize.tcl "" "

exit #.

INFO: [Common 17-206] exit Vivado at Tue Mar 24 23:58:54 2015...Compile time

---------------------------

Introduction date: 24/03/2015-16:46

Date recovered results: 24/03/2015-17:00

Waiting time in the queue: 00:24

Compilation of time: 13:22

-Generate a Xilinx IP: 00:00

-Summarize - Vivado: 01:27Compilation has restarted on

24/03/2015-16:57---

Any help would be much appreciated!

Thank you

James.Morris wrote:

Okay, so it seems that I get the error with a project from scratch and an FPGA with a single command and an indicator.

I download the latest FPGA 2014 SP1 installation and I hope that will solve my problem.

Well I'll mend, which fixed the problem! Somewhere along the line, my install FPGA must be corrupted.

Thanks for the help, guys.

-

Question about server failure and data migration store

Hi guys,.

I just KVM/QEMU on Ubuntu Server and CentOS using Ovirt area of expertise VMWare ESXi is an easy to fall into the domain but I have a question for Server (Host) / relationships of data store. At the moment I have 6 ESXi running on a Dell server and use the local storage in the data store. I am limited in storage in this way so I thought I'd do a NAS or SAN, cost dependant, to expand my storage levels but I'm not sure of some things, but this one being the most important. If I use the server as a host of stand-alone and everything stored on NAS or SAN, storage in case the server fails and needs to be replaced can I use a new server and in the case of new installation of ESXi and use the existing database as nothing has happened or is it possible?

Thank you

Yes, it will work. By default the virtual machines consist of a bunch of files stored in a folder, and as long as you use the same (or a newer version) version ESXi - i.e. a data store format supported - you will be able to access these files.

André

-

HY all!

I have a few questions using Xilinx compiler tools.

The reason why I want to use FPGA is to get the analog measurements of two modules NI 9205 and also filter these measures. Modules are configured to run in terminal diff mode, while the other parameters of this module are set to default values (+/-10 V etc.).

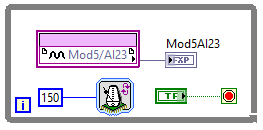

2.1 when I try to compile the program easier - read one analog measurement every 150 US, see the figure below - just compilation takes too much time, namely fear for a few hours, specifically, compiling stucks on mapping. I followed my PC performance, processor is about 20% 3.84 GHz, while the memory is on 10% 31.9 GB. Q1: is it possible to configure the compiler to use as many resources as possible PC?

I'll post probably questions once I managed to get this simpler program to work

Thank you in advance!

Best regards

Marko.

Hello

What operating system do you use? I read somewhere on this forum that windows 8 and possibly windows 10 are not taken in charge by xilinx compilator.

I have simular problem faceing with the compilation of the code. On Windows 8 compilation take over 50 minutes and not finished yet. Then tried to compile the same code on Windows 7 it only take 10 minutes. -

Results of FPGA compilation and size required FPGA

Hi all

I currently use an intelligent data acquisition card (7853R) to generate the AO modulated on five channels to five different densities. The modulated signal can be either: a sinusoidal signal, a square wave, or a wave form defined by the user using a single READ (40 k, points 16-bit). The card I am currently using is ready by OR, and I am now faced with buying my own. Initially, I had proposed using the7841R, as it does not appear that we would be using one of the largest FPGAS to their full potential. And for the most part, we are not. We use about 6% of the slice of registers and 6% of the LUTs. However, we use 100% of the IOBs LOCed (who previous knowledge base said that I would not be concerned with) and 96% of the RAM36_EXPs. Unfortunately, I have no documentation on these and can't know if my code fits on most small (wx30) FPGA in the 7841R. If I had to guess, I would say I use 96% of the RAM on the current FPGA block and my code would have hard on the smaller FPGA, as is the block of RAM available< half="" of="" that="" on="" the="" larger. ="" but,="" i="" don't="" think="" it="" is="" that="" simple. ="" does="" anyone="" have="" any="" thoughts="" on="">

Thanks, Matt

I know not what it is either, but you can always choose the destination in LabVIEW and compile the application. you don't need hardware for it. Try it and then you should be able to make a purchase decision. Of course, someone of OR should be able to get back to you on the definition of the attribute. or I'll just say: ask him when you call to buy the product. If you have any questions, please after return.

-

LabVIEW FPGA compile Cloud Computing Service stuck on the production of carrots

Hello

Since I was on windows 8 I do use cloud server compile compile my screws

However, lately he has been slain a lot during production of carrots.

Is that what I can do to get rid of this problem? Sometimes it just doenst seem to compile at all but sometimes it compiles. It's embarrassing because I rely on this service.

Any advice?

How long compiling stuck there? If your application requires a number of hearts, it can take a long time to generate all the necessary support files. For some large FPGA, this party may take several hours the first time you hit a new compilation/instance machine. Fortunately, the carrots are cached, so maybe why it is sometimes faster, depends on which machines your compilation is striking.

-

LabVIEW fpga compile: translation error then again translate

Hello everyone,

I have a question about the process of compiling LV FPGA.

The context:

I am compiling a binary FPGA for the NOR-5644R (viterx6 inisde). the process is quite long (up to 7 hours depending on how is our CLIP). I am canvassing any idea of attaching the compilation process.

The fact:

By analyzing the log file of the previous compilation, I noticed that the stage translate is made twice, probably because one is a failure. the excerpt from log files are copy/paste below.

Further, it seems the errors (at least some of them) translate the first are induced by the commented lines of NOR provided file UCF (RfRioFpga.ucf)

The question:

Why to translate step to do it twice (the first being failed)? would it not quicker to make only the second succefull one? in other words, it is really necessary for the first fails to translate step for the FPGA binay?

Any ideas?

Thanks in advance!

See you soon,.

Patrice

----

log file extract 1:

"...

NGDBUILD Design summary of results:

Error number: 387

Number of warnings: 1443Total in time REAL until the end of the NGDBUILD: 2 h 16 min 45 s

Time CPU until total NGDBUILD: 2 h 11 min 21 secOne or more errors were found during the NGDBUILD. No file NGD will be written.

Writing the file of log NGDBUILD 'RfRioFpga.bld '...

'Translate' process failed

..."

log file excerpt 2:

"...

NGDBUILD Design summary of results:

Number of errors: 0

Number of warnings: 818Writing the file 'RfRioFpga.ngd '... NGD

Total in time REAL until the end of the NGDBUILD: 29 min 17sec

Time CPU until total NGDBUILD: 27 min 33secWriting the file of log NGDBUILD 'RfRioFpga.bld '...

NGDBUILD done.

'Translate' process completed successfully

..."

Hi Patrice,

It seems strange that it performs this step two times (and was worried when I saw the first time), but there is good reason for that, certainly. LabVIEW inserts constraints for components, he adds, but sometimes the components get optimized out by the compiler. When the compiler encounters stressed that points to the now non-existent component, it error. LabVIEW circumvents this by running the process to translate two times. The first time, it may fail. LabVIEW will remove the constraints that fail, then run again translate it. Unfortunately there is no way around this problem.

-

ERROR: TclTasksC:process_077: in the FPGA Compilation

Hi all

I use for my application in which I am facing following error when compiling my fpga code compact rio 9072:

Compilation failed due to an error of Xilinx.

Details:

ERROR: TclTasksC rocess_077: did not finish. Please, look in the newspaper and report files.false

rocess_077: did not finish. Please, look in the newspaper and report files.false

When running

"process run"card.

(file "C:\NIFPGA\jobs\XI64xG6_My449tj\map.tcl" line 6)ERROR

ack:2310 - type compositions "SLICEL" too found to adapt to this device.

ack:2310 - type compositions "SLICEL" too found to adapt to this device.

ERROR ack:18 - the design is too large for the device and package.

ack:18 - the design is too large for the device and package.

Please see the Design summary section to see the cost estimates for

your design exceeds the resources available in the device.

NOTE: A file NCD will be always generated to allow you to examine the mapped

Design. This file is intended for assessment use only and will not be processed

successfully through NOMINAL.

This NCD mapped file can be used to assess how the logic of the design has been

mapped in FPGA logic resources. It can also be used to analyze

preliminary to the level logic (route pre) calendar with one of the static electricity of Xilinx

analysis of synchronization (PRHT or Timing Analyzer) tools.

Summary of the design:

Error number: 2

Number of warnings: 69

Use of logic:

Number of slice Flip Flops: 7 886 on 15 360 51%

Number of 4-input lut: 16 104 on 15 360 104% (OVERMAPPED)

Distribution of logic:

Number of slots occupied: 8 744 7 680 113% (OVERMAPPED)

Number of slices only related logical container: 8 744 100% 8 744

Number of slices that contains no logical relationship: 0 to 8 744 0%

* See NOTES below for an explanation of the effects of unrelated logic.

Total number of 4 input lut: 17 400 on 15 360 113% (OVERMAPPED)

Number used as logic: 15 998

Number used as a middle way: 1 296

Number used as Rams 16 x 1: 82

Used number recorded the shift: 24

The logical Distribution report slice is not significant if the design is

too mapped to a resource not slices or if Placement fails.

Number of IOBs servile: 183 on 333 54%

BIO flip flops: 74

Number of RAMB16s: 1 24 4%

Number of MULT18X18s: 2 on 24 8%

Number of BUFGMUXs: 4 to 8 50%

Number of DCMs: 1 on 4 25%

Fanout of the Non-horloge nets on average: 3.38

Peak Memory use: 361 MB

Total in time REAL in the completion of the card: 1 dry 12 mins

Time CPU until the end of the total map: 1 dry 12 mins

NOTES:

Related logic is defined as logical that share connectivity - for example two

Lut are "related" if they share common inputs. During Assembly of the slices.

Card gives priority to combine the logic that is related. Generates so

best performance of synchronization.

Without logical report does share no connectivity. Card will start only packing

logic not related in a slice once that 99% of the slices are held through

logical packaging partners.

Note that once the logical distribution reaches the level of 99% by related

logical packaging, this does not mean the device is completely used.

No logical report package will begin, continuing until all usable LUTs

and FFs are busy. According to your timing budget, an increase in the concentrations of

logical packaging unrelated can adversely affect the performance of timing set

your design.

Mapping performed.

See the report of map file "toplevel_gen_map.mrp" for more details.

Problem encountered during the packaging phase.

Failure of the process 'Map '.Start time: 18:29:23

End time: 18:44:42

Total time: 00:15:19Can someone tell me why this error came?

Thank you best regards &,.

Vipin Ahuja

Vipin Hello,

It seems that your code requires more resources that are available on the FPGA. Optimizing your code can help to solve your problem:

You may have noticed some "Overmapping", mentioned in the newspaper:

Number of 4-input lut: 16 104 on 15 360 104% (OVERMAPPED)

Distribution of logic:

Number of slots occupied: 8 744 7 680 113% (OVERMAPPED)Take a look at this article:

http://digital.NI.com/public.nsf/allkb/060BA89FE3A0119E48256E850048FFFE?OpenDocument

And this:

http://digital.NI.com/public.nsf/WebSearch/311C18E2D635FA338625714700664816?OpenDocument

Kind regards

Navjodh

National Instruments

-

stuck FPGA compilation, no errors

Hello

I wrote a LabVIEW FPGA 8.6.1 program (I have written several, this is my most recent). When I run it on the development computer it seems to work fine without any errors. When I try to compile, however, it still stalls on this part:

'Analysis of generic entity

library ( Architecture). This isn't feeze (the compiler is always updated time and you can see it working). It just doesn't progress no further than this point. By chance, does anyone know what could cause this? I know that maybe it's a little vague, sorry. Thank you!

Nevermind, I figured it. I had a knot of analog input within a For loop. This wire entry (i.e. given out the analog input node) was connected to a tunnel auto-index on the loop For I have just disabled automatic indexing on this tunnel and everything seems to compile fine now.

-

I'm converting a piece of code from 8.5 to 2011. When I tried to compile the fpga vi to a bit file, I get the error attached. Why is this? Thank you!

The thing is that the only solution that I found about this error is to install a patch or repair/reinstall Xilinx or LabVIEW FPGA tools.

Christian

-

FPGA compile incorrectly configured worker

Hello

I've recently updated my software using the CD that spring 2014. I have NI LabVIEW 2013 Professional sake system. Now all the screws project, I used to compile successfully are communication error. It is said that compile worker is configured incorrectly. How can I configure it correctly? I am a new user of LabVIEW FPGA. I am attaching screenshots of a project that I do as an exercise. Someone can you please tell me what I'm doing wrong and how can I fix this problem. I will be grateful.

Thank you and best regards,

Kamal

I installed the hotfix published by OR for the compilation tools from Xilinx 14.4 and after installing this patch, I have no difficulties in the compilation of the screws. I am grateful to all those who have offered their help to solve this problem. Thank you very much.

Kind regards

Kathar

Maybe you are looking for

-

my iphone 6 starts to turn itself automatically more and more. restart the phone did not help; change the password did not help; l ' turn off works for only a few seconds, then it turns itself back on. any suggestion would be appreciated. Thank you

-

OfficeJet 7612: Custom paper selection OfficeJet 7612 size?

I implemented a custom size (11.5 x 10.0) in Windows 7. Suite insttruction of this site on the definition of this size, I am responsible to go in displays preferences-paper/quality-advanced and set the size here in a drop size. However, the 7612 pref

-

NB200 - upgrade the RAM and install Windows 7?

Hello to you guys. I'm back and received the news for you. I got my new Toshiba NB200-10Z. I would like to ask you: What are your comments on the upgrade of RAM? The difference is notable? It worth the cost?What RAM memory slot I'm supposed to get? A

-

My laptop don't stream video live, I can watch videos online, but when the videos are being broadcast live, he plays for about 4 seconds, and stops.i really need help, what I do...? Name of product: notebook PC HP Pavilion g6 Thank you...

-

Pen Tablet WP8060 works like a MOUSE instead of a pen...

I have a USB «WP8060» TabletI've always used on my XP PC, but it will NOT properly work on my new Windows 7 PC. I think the stupid windows 7 generic compressed software comes in. I went into the SERVICE. MSC and disabled the makings of the tablet. Do