run inside once timed loop

I have a timed loop that monitors the equipment. Whenever there is an error I send a notification by e-mail. My problem is how to stop send e-mail whenever the time loop is executed. I tried placing email it inside a loop, but quickly realized that the whole of the loop itself is reiterted. Any help is much appreiciated.

You can also consider using the first call? under the range of synchronization primitive.

Tags: NI Software

Similar Questions

-

While loop inside a timed loop

Hello world!

I use:

-LV 7.1 + real-time;

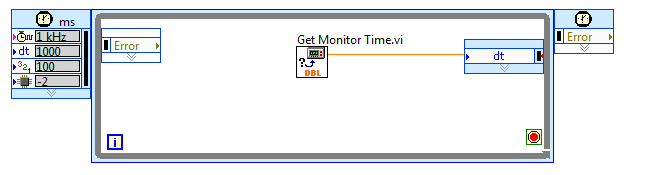

-compactFieldpoint;When I put some time, I noticed a strange behavior, loop inside a timed loop. Let's fix loop timed with these settings:

-Clock 1 kHz

-1 ms period (Yes, I know it's short...)

-offset 0 ms

-Stage 0

-Take the period of absence (ON) and maintain initial Phase (ON);

-Timeout:-1.So, inside the loo, I put a traditional while loop, waiting (for example) an event will occur, and if this event doesn't happen, my cFP-2020 crashes! I mean, it becomes inaccessible for the debugger, and also, if I run a ping at his address, after a few cycles it becomes inaccessible as ping!

Obviously, that statement of code lock the fieldPoint, because if I remove the inside while loop all work.

I know that with 1ms duration, timed loop always the finishing of the delay, but I put the scrapping period missed and timeout-1.

It seems to me that sometimes timed loop add overload heavi programs, I all so that the loop according to the tasks, even if my application has be in real-time!Tips welcome! Good day!

Graziano

Thank you very much for your answer!

I'll test the entire application and then look for the best practice... but I still think I'll replace it timed with while loops loops...Good day!

Graziano

-

Sequence structure flat inside the timed loop and execution order

I have some problems trying to implement a flat sequence structure when you use a loop timed on a target of cRio VI

I tried with or without the while loop around the structure of sequence flat, and I also tried to replace the 'Non-deterministic loop' with a timed loop

The problem is that the program seems to run only once, then get stuck somewhere

I am writing a program that performs the following operations as soon as possible:

1. read the Pos_MC of entry on the FPGA

2 send the value of Pos_MC to the VI target (on cRio CPU)

3. calculate a value of output based on Pos_MC with a PID block ("exit PID')

4. send 'PID output' to the FPGA

5 write "PID output" analog output "MOOG".In addition, I want the program to return the measured value "Pos_MC" to a host VI for the recording of data

So that the output of PID is calculated and sent to the FPGA as quickly as possible, I placed a flat sequence structure to ensure that it happens before you send the output to the nondeterministic loop for recording data

Also, I want the digital input 'Stop' to be able to stop the loop deterministic (the timed loop)

I read much more entries than that and the help of several PID and exit, but I rewrote the code for a single entry and exit to make it easier to illustrate

Screenshot of the code is shown in 'target code.png' and 'fpga code.png.

The VI themselves are attached in the next post (cannot attach files of more than 3)

Question 1:

Any advice on how to get this race? Thank you!Question 2:

Is also my correct understanding in that, using this structure, each 0.9ms (fpga loop time) comes the following:

1. the input ("Pos_MOOG") is read on the fpga

2. the production of PID is calculated on the cRio with some delay to computation (for example 0.1ms)

3. the output of PID is then written for analog output "MOOG" in all about 0, 1 - 0.2ms

4. the FPGA program then waits until 0.9ms spent and repeat the processAs opposed to the next pass whenever performing a loop is started on the FPGA:

1. the FPGA reads the input and written on the output (the output of the execution of the previous loop PID)

2. then the entry is sent the cRio, PID output is calculated and sent to the FPGA

3. the new release of PID is maintained until the next time through the loop

Thank you!

PHG wrote:

Thanks for the input guys, any advice as to how I could get the feature in scenario 1?

I still say that the best route is just putting all the logic of the control in the FPGA.

Other alternatives include 1) the use of DMA FIFO sedn data back or 2) use interruptions so that the FPGA code can not read the output level until the RT.

DMA FIFOs are usually very limited, and I would not use them in this situation since I belive said it this code to do for the many outputs.

-

Schedule iteration five FOR lines inside a timed loop...

Take a look at the attached code simply run five different but identical TO the lines inside a single loop timed.

It is interesting to note the timings of each loop iteration FOR: 1,1,2,3,0 milliseconds. The most curious is the moment of the last loop, which for the most part indicates 0! Not only this, if you remove the fifth loop, the fourth a bed 0.

I can't understand this behavior? Also if LV deals in parallel different loops why should there be a gradual increase in the synchronisation of successive loops?

Thanks for any help.

First, 0.2 ms is not statistically significant, you must increase the number of iterations by another factor of 10, at least.

A quick loop uneducated wait FOR will grab the CPU for much more than one iteration, so regardless of the loop is first online will repel the other loops and run until LabVIEW decides to switch to another loop. The number of cores CPU do you have?

You can force a release after each iteration by placing a 0ms wait inside each loop FOR. While all time will be significantly longer because of the overhead of increased switching, all loops will be now around the same time.

You can also read this for more information.

I don't know that anyone else can provide more details in the jargon of right. I don't know the correct terms for all this.

-

Most of the machine control software I design have the following structure:

1. There's a HAND that takes place inside a TIMED LOOP with synchronization of 50ms and priority of 100. His only job is to read / write data from / to DAQMx IO cards.

2. the MAJOR can call several SUBs based on the choice of the user, and once a submarine is called FP MAIN is closed and the FP SUB opens. All submarines have a States Queued Machine running within a TIMED LOOP with 50ms timing but with priority to 50.

3. data transfer between HAND / SUB is through function globals - there are many of them based on past data.

4. all woks fine so far. No need to any RTOS. and platform of WIN7 is alomost standard. I even ran with a timing of 20ms without anything crashing...

Problem: When there are a lot of file i/o operations in a SUB partciluar, then I have the chance to see several missed iterations. Perhaps the TIMED LOOP is hogging resources.

What I want to do: convert both TIMED in asnd SUB HAND loops simple while loops. But I am concerned by the priority - since the MAIN interacts with HW there priority. But with LOOP WHILE how can I ensure this?

Or is there any replacement / effective way of doing what I do now?

Rama wrote:

.... FGV should be thrown out the window...

Well used for a while, based on many articles in the KB. One of them is locked... and it does not represent the engine of the Action or of the FGV as a villain to avoid.

The driving force is one of the largest buildings in LabVIEW. The FGV who does nothing but Get and Set (or writing and reading) is useless and a waste of resources. Why? It does nothing to fix possible race conditions (does not protect critical sections) and it is much slower than just using a global variable. See this example I put in place to see what I mean: an overview of the race Conditions.

Rama wrote:

So in the sample that I had attached, what do you think would happen if I just replaced the two loops with the SAME timed in MAIN and SUB wait value ms. is there a work order then?

When things are at the same time, there is no such thing as the order of execution. But as I said, it seems that your loop is quite slow, so it's something I would not worry. Just make sure that you do not have a loop that uses all the CPU.

-

How to force a new period of a timed loop?

Hello.

Here my question:

I need to modify programmatically the period of a timed loop. This isn't a problem but:

I have to wait until the next loop to present new period value. For example if my previous period was 20 minutes, now I have to wait 20 minutes in order to submit a new period.

This beacause the code to change the period should be inside the timed loop itself. You can see what I mean in the picture as an attachment.

The Subvi Gets the new period of a console operator. It will run until the end of the period previously configured.

My question is: is it possible to force the timed loop to get the new value without waiting for the execution of the previous period?

Thank you

FPIA

Hi fpia.

Sometimes, it would be more useful to 1200 seconds instead of 20 minutes

It was suggested many times before: rather than wait for a long time with just a single call to a wait function you should divide this amount of time into smaller pieces!

-Why do not use you a period of time for example 5 and only count the iterations to know when 20 minutes are more?

-Why don't you use the function "Time" to know when to exceed the 20 minutes?

-

Impossible to click on the buttons for the timed loop.

Hello!

I have a loop that is timed with a pace set by the user. And when the loop is running, I can't push any button of my GUI to stop it...

I have to wait until a mistake or I stop the race.

I can't put the diagram is too big and I think I don't have the right, but you have ideas?

Ask me for more details.

Thank you

bejard wrote: timed loop is just in a structure of the event and I put 10 ms or 100ms.

The program runs correctly (with this loop delay of 10ms/100 ms) like in the beginning, but I can't push any button or even change the tabs during the loop.

You shouldn't have long extensions inside the event. Which is supposed to stop your timed loop?

I think that you have the option "Lock the front until the end of the occurrence" lit. It will not press anything, until the end of everything for this case (including the timed loop).

According to my experience, using a loop timed in a Windows system is a complete waste and often adds more overhead and questions. Instead, I really think you need to use a State Machine. When the button is pressed, you tell your state machine to move to the State the code inside your timed loop tracks. You can use the State with the structure of the event to time your loop. If you can go behind your state of event to your processing loop structure. Just set the timeout on the structure of the event at any rate of loop you really want to.

-

passing the value and to timed loop

Hello everyone,

I'm working on a VI that consists of a timed loop which takes values in a file every 6 ms and writes it to an output file. Inside this timed loop, there is also a MATLAB block that calculates a parameter based on the value. based on this parameter, that a marker is set to 0 or 1 (planned) to operate as a Boolean marker.

The problem arises when the marker is set to 1. I need an additional structure any that waits five seconds (without stopping the timed loop iterations) and a 'stop' button is not pressed an additional string is placed in the output file. I wish for the marker to get back to 0 if you press the 'stop' button and not string to put in the file.

The main problem seems to be the use of a structure outside the timed loop. I can't have a while loop or any structure that waits 5 seconds inside the timed loop. And if I let him out he does not have the value of the marker second structure during execution of the timed loop.

+ Any ideas on what the structure to be used during the 5 seconds Timeout? (I tried a while loop)

+ Use a local or global variable for the marker? (I tried briefly, but as a local variable, I couldn't choose a variable defined in the MATLAB block, and I don't understand global variables in LabVIEW)I enclose a simplified version of the VI as well as a sample input file in case it can help visualize.

Thank you

DAVASo far, there are a few problems with your solution, but first of all, I will try to help answer your original question.

You are right that you can't have a structure inside the timed loop which waits five seconds without blocking execution of the timed for the same period. You are also right that you cannot simply communicate through cables to an external structure. If you exit a loop of wire in the other, which creates a dependency of data flow, which means that the data loop cannot run at all until another loop ends its execution entirely and send data.

You have two options:

- Don't actually use a wait function to determine if the 5 seconds elapsed. Use the Express VI of time elapsed (search the palette). He just guard track of how much time has passed since the last reset. It does not wait. If you are safe to use inside your loop timed in a case that is triggered when the marker value becomes 1. Also check the Boolean command in this case Structure to decide if you should output the data in the file.

- Use an outer loop as in the example you posted, but use screws of the range of synchronization to send data between the parallel loop. Consider a queue.

But overall, I don't think there is much chance of this work very well. No way, the Matlab Script node running fast enough to run at a time of 6ms. Also no way it works in a deterministic way at all. He needs to communicate with an external program, so its execution time is really unlimited.

-

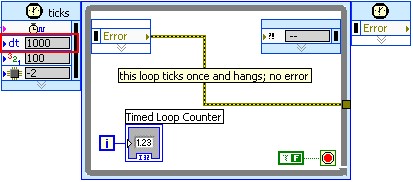

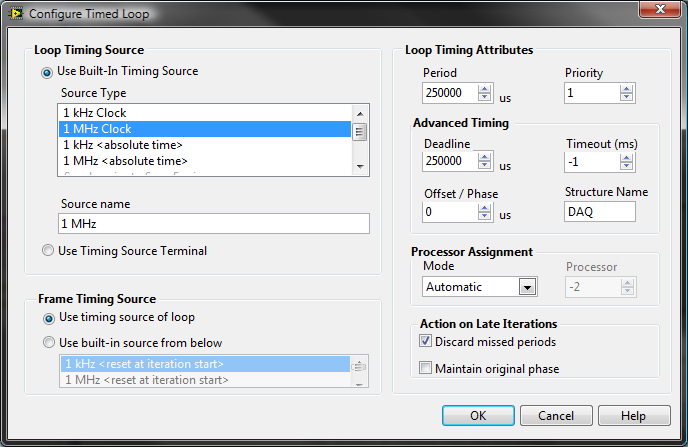

Timed loop runs only once with pulse train?

It is a VI that attempts to drive a loop timed with a train of pulses 6608 OR map attached. My timed loop never appears to run more than one cycle. No error is reported. I suspect it's because I'm not set up correctly with NOR-DAQ. Any help would be most appreciated.

WB

Hi Wb,

Take a look near the timed loop, I can see that the value of dt period is set to 1000. This period is used to scale based on synchronization source units. In this case, the clock contains 0.5 second pulses. Change the dt to a value of 2 has allowed me to see the timed structure to go as planned. See the image below for more details:

I hope this helps. Let me know if this behaves that way even on your system.

See you soon!

-

While the loop within a box Structure runs only once a target FPGA

I have a card OR cRIO-9012 RIO for the HIL system. I have a target FPGA file when I use a While loop within a while loop I use the box Structure to check a real condition inside I have the function of activation of the ports and selecting the analog and digital ports. But for my code the code runs only once on repeted times that we have in the LabVIEW environment.

I also need help to optimize the code. I've seen people using While loop timed in the FPGA target I don't use in both cases.

I've attached my FPGA with the Version of LV2012 file.

Waiting for your comments.

Thank you and best regards,

Ganesha Moorthy

You have while loops inside the structure to deal with a constant of false cable to the stop condition. These loops will obviously never stop so browse your outside while loop (containing the case structure) can never.

This has nothing to do with the FPGA target, the same thing will happen in the development environment.

-

In the attached VI, I put the loop timed to end once the delay 1 reaches zero. However the timed loop continues to run and stop only if I have OR both 1 and 2 delay delay. (Tried with different schedules for late 2 which are less lag 1, equal to 1 delay and more delay 1 - no chance unless it is also linked to stop)

What is the reason for this? (The VI is in LV2012)

And it is protected by word that prevents us from looking into it.

Is this your VI or did you also?

Subvi properties seem to show that it is not reentrant. Otherwise it can only run one instance at a time. And if happens to store data to leave once it is called to another in the uninitialized shift, running an instance registers is probably interfering with the execution of the other instance.

-

What is error-1418 on a timed loop?

Someone at - he never had error - 1418 on the timed loop terminal error? It runs only once and I'm trying to run it on a cRIO-9004.

There is nothing in this range listed under the timed loop error codes.

http://zone.NI.com/reference/en-XX/help/371361F-01/lverror/timed_loop_error_codes/

As always, thank you

Jim

Hi Jim,.

I think that's what you're looking for:

Synchronization sources available for LabVIEW timed loop by platform

Kristen H.

-

Module speed FPGA, speed controller and timed loop speed

Hello.

I'm developing an application to acquire an analog signal at 800kS/s. Budget does not seem to be enough buy material excess spec. So I have to be very very accurate on all components. I had a look on the site and selected the following materials.

9221 8 module capable analog channel on 800kS/s sampling. I don't know if this sampling rate indicated in the specification of the module means that it can acquire up to 800kS/s or is the device samples ADC sampling rate to which the machine don't maybe not to the criteria of Nyquist and the module can perform sampling to 1.6MS / s is necessary which I think is not available?

9012-400 MHZ controller controller. If I put a while loop inside a VI under the RT target, it runs at 400 MHZ by default provided there is no code inside? Is so I could definitely use loop time express vi for sampling at the required level.

What of the timed loop? I just developed a project of RT and added vi under the RT target. The timed loop default clock frequency is 1 kHz and I can't select more than 1 MHz?

9112 chassis. Default clock 40 MHz. same rate issue which concerns the 9012 above controller.

Kind regards

Hi AustinCann

If you need to acquire 800 kech. / s, then the module module-9221 will be able to do this, if you are using only 1 channel, that is. The module using a global sample, therefore the maximum rate will be distributed on channels that you use.

If, however, you have to detect the frequency of > 400 then you would need a higher sampling rate to detect these, as you mentioned.

The controller processor runs at 400 MHz, even though the loops in your code will not run at this pace. On the target in real time, you can use a timed sources of clock - usually 1 kHz to 1 MHz - and set the period in terms of the chosen clock. If you need faster line rates, you can still code directly on the FPGA. The CompactRIO Developers Guide is a comprensive document and deals with most of the concepts of RT and FPGA.

The best course of action would be to contact your local office, because they have all the resources necessary for the specification of your system.

-

Having a strange action case structure on a timed loop.

A resolved question yesterday, lead to a new problem. In this VI, I have a timer that triggers an external meter. The counter "counts" from 1 to 24, each with an action at a given time. However, once I got the timer and counter work, I found that the Boolean trigger remained on the hour enitre, and my action was repeated several times instead of only one. So, I changed the counter count 0.1 each interval, rather than 1.0, thinking that it would only allow my State business to operate for a shorter window. However, when I run the VI, the case of the State are active in the meantime, not at the interval. For example, cases of stae 2 is active between 1.5-2.5 iteration and iteration throguh 2.5 3.5 State case 3 is active. Can anyone suggest how to get either 1) better display resolution on the evidence of the State of th or 2) another way to get the Boolean value for just a few seconds?

Thank you, Lynn. Yep, I tried that (at least the half of it.) I opened it in my first version, which is being 8.5.1. I don't think to check in the dialog changes not saved, however. I feel kind of sheepish having never tried that before.

Well, here is my interpretation of what was asked for... I had to make a few assumptions, namely that the 'timed loop' refers to the while loop that runs at a defined interval, and that "triggers" are just the Boolean flags.

I hope that this at least partially answered questions?

Jim

-

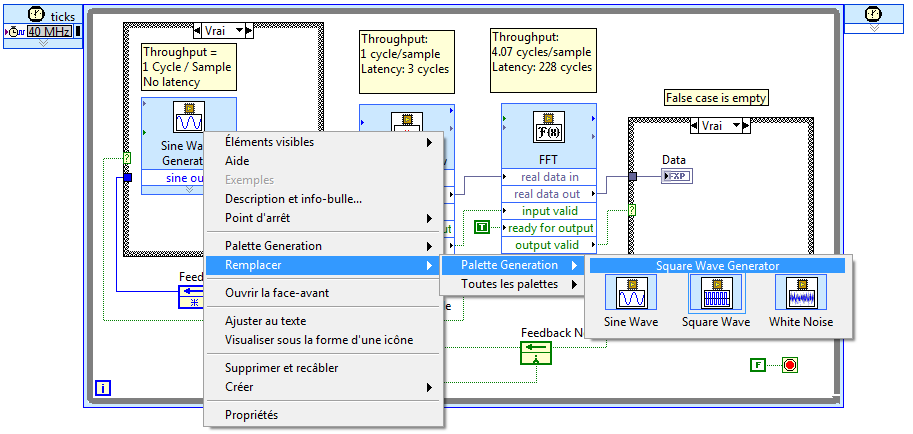

FPGA 2012 training: exercise fails '4-Wire Protocol' 7-2: not supported in single-cycle Timed loop

I work through the training courses OR 2012-FPGA with Labview 2014 SP1. I find the solution provided to exercise 7-2 called '4 son Protocol.lvproj' does not work. He is unable to run with the message "LabVIEW FPGA has reported the following error: item (s) not supported in single-cycle timed loop.»

Should it? I thought that the examples in the solutions folder were supposed to work such as provided. What needs to be fixed for this work? Thanks for any help.

Hello jbeale1,

It is a known problem. Here is the comment of NEITHER:

---------------

Exercise no. 7-2: 4 - Wire Protocol [Allen Hsu 2013.8.19]

- Description of the problem: exercise 7-2 uses a sine wave generator inside a SCTL VI. In 2012, LV, this VI is not supported in the SCTL, but LV 2012 will allow you to use mode 'simulation' (run on the dev machine). However, LabVIEW 2013 not even lets you use this VI in "simulation" mode If you run the VI with the sinusoidal generator inside a SCTL VI, LabVIEW 2013 gives you a "or objects not supported in single-cycle timed loop.

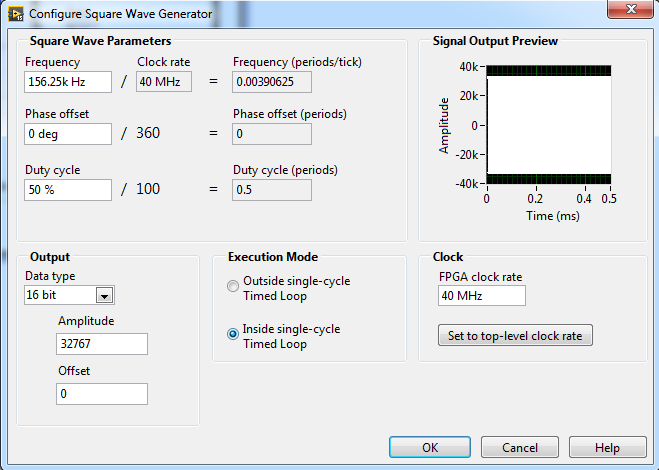

- Solution: If the students use LabVIEW 2013, you must tell the students to replace the sinusoidal generator inside the SCTL pre-built exercise VI VI with a Square Wave generator VI with the option "inside the SCTL" enabled in its configuration window, as shown below:

--------------

To replace the "sine wave generator" right-click on it and select the 'Square Wave Generator'. Then you have to double click on the "Square Wave Generator" and select "inside the only cycle timed Loop". You should then be able to run the example.

Maybe you are looking for

-

problems with CPU

-

History of clear waveform using the reference

Hello I would like to clean up the history of the wave I have in my hand Vi. I'm passing his reference to a sub - VI. I'm not able to find ownership of historical data among the other properties of the property node. Behold that I have: Thank you. -H

-

What is - this I can improve in a hp pavilion p6 2310

It's the pc link http://h20565.www2.hp.com/portal/site/hpsc/template.PAGE/public/kb/docDisplay/?sp4ts.oid=5295969&spf... Just a question about it because it's a good pc

-

Cisco TMS version "No error HTTP 401 response code" TMS 14.2.2 VCS &. 7.2.1

In a separate post, I have something related to this, but I would like an answer by the morning when I wake up so I just made a new post. So, I have synced up my TMS with my VCS and I can now click the Configuration tab and I was informed by a Cisco

-

Dreamweaver CS5.5 and GoDaddy FTP issues

Problem: Dreamweaver displays a good connection when the connection test, the FTP log shows a connection, but when I look in the directory of the file to the remote server, it only shows the folder for one of my subdomains with .bash files listed. Al