Simulated FPGA i/o error-61399 Recive

Hello

I'm trying to simulate a cRIO-9073 on my development computer. I want to use the simulation I / 0 features. If I use the random data, I have no problem to run my simulated VI. If I use the option 'Use Custom VI for FPGA of IO', I always get the error 61399.

I already had a look at this link but and use a model of VI, but that doesn't change anything. I also had a glance on the tutorial explaining how to do it but without success...

Any idea?

Thank you!

Hi vgravel,

Did you also know that the "Custom VI has been set for each element of I/O that you use in your FPGA code?

FLash

Tags: NI Hardware

Similar Questions

-

Compilation of FPGA - real formal error on the cost of the port cannot be an expression

Details:

ERROR: HDLCompiler:192 - "C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd" line 1408: real formal on the cost of the port cannot be an expression

ERROR: HDLCompiler:854 - "C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd" line 69:Unit ignored due to previous errors.

File VHDL C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd ignored errors

-->The compilation happens to step "using the unit felt" but then stops soon after with a compilation error.

The line in question (1408) refers to the output of a "Reinterpretation FXP" node with the text

Cost => (others-online '0'),

in the part of port of the code card. This is the output of the FXP reinterpret node is directly connected to an indicator in a VI sub whose output is then entered directly at a crossing high multiply node. The code is part of a cosine sine LUT I programmed. She used to compile without a problem, but I think I know where is the problem. In one case, I have used only the sine of output of the algorithm and theory, Xilinx can optimize away from the part of cosine. I have two instances of this VI in my code and looking at those generating any errors, the output is associated with a cosine indicator.

Cost-online s_Cosine_2434,

It seems that the track is essentially optimized away, but the compiler, Xilinx has a problem with the flag being present on the sub - VI but the idnicator is not used anywhere. As a result, the cost gets set to an invalid value. I guess close to reinterpret it FXP at the exit of the Subvi is an important aspect of this problem.

I think I know enough now to fix this (remove the path manually by duplicating the sub - vi), but it may be useful for future bug fixes feedback in the FPGA module. It is not the first time that this kind of removal of incorrect code me has given problems, but this is the first time I could clearly identify the problem.

Shane

Hey Shane,

Looks like someone filed a bug report on it a month or two ago. It's the CAR # 475397 if you want to check for it in the list bug fixed for 2014 SP1.

-

stuck FPGA compilation, no errors

Hello

I wrote a LabVIEW FPGA 8.6.1 program (I have written several, this is my most recent). When I run it on the development computer it seems to work fine without any errors. When I try to compile, however, it still stalls on this part:

'Analysis of generic entity

library ( Architecture). This isn't feeze (the compiler is always updated time and you can see it working). It just doesn't progress no further than this point. By chance, does anyone know what could cause this? I know that maybe it's a little vague, sorry. Thank you!

Nevermind, I figured it. I had a knot of analog input within a For loop. This wire entry (i.e. given out the analog input node) was connected to a tunnel auto-index on the loop For I have just disabled automatic indexing on this tunnel and everything seems to compile fine now.

-

for the FPGA fifo compilation error

Hello

I downloaded the example RS232 FPGA program and tried to make a small change to it. The original is like that; See attached file "beforeModification.PNG".

I wanted to reread the amount of data still in the FIFO where I had read everything so I changed it to that. See attached file "withModification.PNG".

The target is using the compiler 13.4 Xilinx 7841R. I'm not in the section summary with the following error message;

Details:

ERROR: HDLCompiler:1566 - "C:\NIFPGA\jobs\K7I4YEj_RQC5mWo\NiFpgaAG_FPGA_Main.vhd" line 869: Expression has 11 elements; official ocountfullcount wait 10I'm currently running;

LabView 2012 SP1 f3

12.1, the R Series multifunction RIO of NOR

I'm doing something wrong?

Thank you

Andy

The problem disappeared when I copied the source files in a different folder

-

Number of cycles Express VI outputs '0' on target with simulated FPGA of e/s

When I set my target to "Run VI on it development with simulated i/o", the number of cycles to screw all the outputs ' 0 whenever they perform. How can I do a count up (in the case of "ticks") or a timestamp that is appropriate (in the case of "ms") the output?

In fact it does not work as expected. I apologize. When in mode [ms] he ran if slowly as my test that bolt looked like they were defective and I did not notice the value incrmenting when I probed it. I changed the test to use the [ms] instance when running on the FPGA and the [ticks] instance during execution with simulated IO. This looks like it gives 1 tick every "" millisecond"simulated" when simulating and now operate my well tests.

Thank you very much for the help. Sorry again for the false report.

-

Broken thread - FPGA Interface Node error

Hello

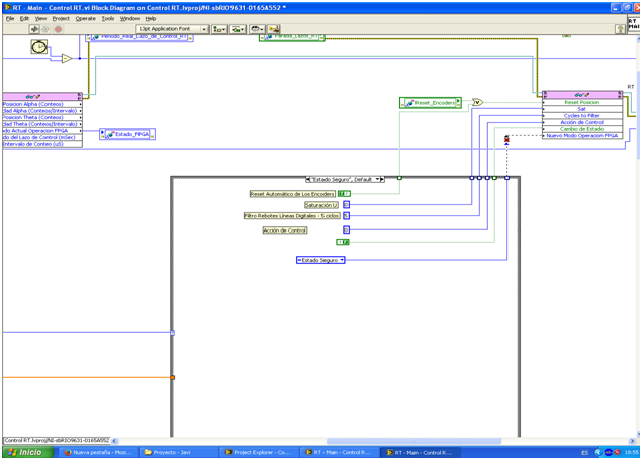

I am programming my application of RT and I get this weird error:

As you can see, I'm trying to set the value of a FPGA control (which is a typedef enum) and I get this strange cut wire

for me, error.

I was looking for a solution in the forums but I luckily able to get a... Could someone help me?

Thank you!!

PS: The error message was "the type of sink is zero" that is false, as already defined in the FPGA vi.

Solved.

To the right, it was like if I've changed some of typedefs and who did not have in mind. Recompiling solved the problem.

-

FPGA IO Module error, recognizes NEITHER 5751 in LabVIEW

Here is my configuration:

- Windows 7 sp1, 64-bit

- LabVIEW 2013 sp1, FPGA, real-time

Which is connected via an Ethernet cable to:

- Chassis SMU-1078

- SMU-8135 embedded controller

- SMU-7961R FPGA x 2

- Module e/s NI 5751 x 2

- LabVIEW time real 13.0.1

- NOR-DAQmx 15.1.1

- NOR-RIO 15.5

- OR PXI Platform Services 14.1.0

NOR, Max the FPGA and 5751 adaptation Modules appear as a gift. But in my LabVIEW project, IO Modules always show an error. I chose the good 'NI 5751' option, but the State still shows this:

I tried to restart the chassis and the computer. I tried selecting another Module of e/s and then back by flipping. I am also unable to compile the code example on the FPGA (Xilinx errors).

Any ideas?

The status shows you which adapter module expects the bitfile who is currently on the fpga module. The reason why it says no is probably because you have not deployed anything the fpga target since he powered and there just the default image loaded on it. Try deploying a bitfile to which has been compiled to work with a 5751 and you'll be fine.

I do not know why you can not compile the 5751 get started example however. I'd make sure you have all the build tools installed correctly. What are the mistakes do you receive when you try to compile? Such problems are sometimes easier to solve by phone if you want to open a support on ni.com/support ticket.

-

flight simulator deluxe edition blocks error codes: Ox20e86983 & Ox84e2f48

Is someone can you please tell me the following error codes say that I get them at halfway in the Simulator deluxe Infant cescodessont Ox20e86983 & Ox84e2f48

Hello

1. have there been recent changes to the computer before the show?

I suggest you to contact the Flight Simulator with the help of the links provided and check if it helps.

http://www.Microsoft.com/products/games/FSInsider/tips/pages/default.aspx

Hope this information is useful.

-

LabVIEW fpga compile: translation error then again translate

Hello everyone,

I have a question about the process of compiling LV FPGA.

The context:

I am compiling a binary FPGA for the NOR-5644R (viterx6 inisde). the process is quite long (up to 7 hours depending on how is our CLIP). I am canvassing any idea of attaching the compilation process.

The fact:

By analyzing the log file of the previous compilation, I noticed that the stage translate is made twice, probably because one is a failure. the excerpt from log files are copy/paste below.

Further, it seems the errors (at least some of them) translate the first are induced by the commented lines of NOR provided file UCF (RfRioFpga.ucf)

The question:

Why to translate step to do it twice (the first being failed)? would it not quicker to make only the second succefull one? in other words, it is really necessary for the first fails to translate step for the FPGA binay?

Any ideas?

Thanks in advance!

See you soon,.

Patrice

----

log file extract 1:

"...

NGDBUILD Design summary of results:

Error number: 387

Number of warnings: 1443Total in time REAL until the end of the NGDBUILD: 2 h 16 min 45 s

Time CPU until total NGDBUILD: 2 h 11 min 21 secOne or more errors were found during the NGDBUILD. No file NGD will be written.

Writing the file of log NGDBUILD 'RfRioFpga.bld '...

'Translate' process failed

..."

log file excerpt 2:

"...

NGDBUILD Design summary of results:

Number of errors: 0

Number of warnings: 818Writing the file 'RfRioFpga.ngd '... NGD

Total in time REAL until the end of the NGDBUILD: 29 min 17sec

Time CPU until total NGDBUILD: 27 min 33secWriting the file of log NGDBUILD 'RfRioFpga.bld '...

NGDBUILD done.

'Translate' process completed successfully

..."

Hi Patrice,

It seems strange that it performs this step two times (and was worried when I saw the first time), but there is good reason for that, certainly. LabVIEW inserts constraints for components, he adds, but sometimes the components get optimized out by the compiler. When the compiler encounters stressed that points to the now non-existent component, it error. LabVIEW circumvents this by running the process to translate two times. The first time, it may fail. LabVIEW will remove the constraints that fail, then run again translate it. Unfortunately there is no way around this problem.

-

Hello

I'm under LV 2010 SP1, I don't know what version of the FPGA module I have, but I think it has been upgraded during the SP1 update. The error is less. It refers to two of the four globals, I use communicate a FPGA timed to a non-timed loop loop.

My code has compiled since the upgrade, but not since the addition of the globals...

I'll appreciate any help on this.

Roger

An internal software error occurred. Please contact National Instruments technical support on ni.com/support with the following information: nirviUIDToObject.vi

reference object get error for UID. All the analyzed text:

-61103 1 NI. Munge.S3 Global.vi_FPGACompileCopy00000001.vi 2 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 4624 Global Variable: ' NEITHER. Munge.S3 Global.vi_FPGACompileCopy00000001.vi' 3 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11890 Global Variable: ' NEITHER. Munge.S3 Global.vi_FPGACompileCopy00000001.vi'

-61103 1 NI. Munge.S2 Global.vi_FPGACompileCopy00000001.vi 2 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11881 Global Variable: ' NEITHER. Munge.S2 Global.vi_FPGACompileCopy00000001.vi' 3 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11878 Global Variable: ' NEITHER. Munge.S2 Global.vi_FPGACompileCopy00000001.vi'

-61103 1 NI. Changed Munge.AO Global.vi_FPGACompileCopy00000001.vi 2 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11906 Global Variable: ' NEITHER. Changed Global.vi_FPGACompileCopy00000001.vi Munge.AO' 3 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 4622 Global Variable: ' NEITHER. Changed Global.vi_FPGACompileCopy00000001.vi Munge.AO' 4 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11905 Global Variable: ' NEITHER. Changed Global.vi_FPGACompileCopy00000001.vi Munge.AO'

-61103 1 NI. Munge.S3 Global.vi_FPGACompileCopy00000001.vi 2 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 4624 Global Variable: ' NEITHER. Munge.S3 Global.vi_FPGACompileCopy00000001.vi' 3 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11890 Global Variable: ' NEITHER. Munge.S3 Global.vi_FPGACompileCopy00000001.vi'

-61103 1 NI. Munge.S2 Global.vi_FPGACompileCopy00000001.vi 2 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11881 Global Variable: ' NEITHER. Munge.S2 Global.vi_FPGACompileCopy00000001.vi' 3 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11878 Global Variable: ' NEITHER. Munge.S2 Global.vi_FPGACompileCopy00000001.vi'

-61103 1 NI. Changed Munge.AO Global.vi_FPGACompileCopy00000001.vi 2 1 Snip...

Unfortunately, even if you can guarantee that the written word never happen at the same time if you write only once per carton, LabVIEW FPGA currently only has not the ability to position the system globals arbitratio for multiple entries on the diagram can cause this error. What I would say is that you write the overall each iteration of the loop outside the structure of the case and that he wire simply the value on a tunnel on the structure of the case. This will allow you always change the value each time through and will eliminate the error of code generation.

If you want to send your comments about this particular use case of LabVIEW FPGA R & D, I would recommend that you post your idea in the Exchange of ideas of LabVIEW FPGA.

-

Former title: Microsoft Flight Simulator will not install on Windows 7

I have Windows 7 Home Premium 64-bit. I try to install MFS 2004. The first 3 discs work fine, but when I insert disk 4 to complete the installation, I get the following error message:

"The version of this file is not compatible with the version of Windows you are using. Check your computer's system information to see if yo need a x 86 (32 bit) or x 64 (64-bit) version of the program and then contact the software publisher. »

I have a Dell Studio 1558

Intel i5 - 520 M

ATI Mobility Radeon HD 5470 graphics card

8 GB RAM DDR3

What can I do?

Hello

1. which edition of Windows are you using? Is - this edition is 32-bit or 64-bit?Given that the game is compatible with Windows 7, I suspect that the conflict can be 32-bit or 64-bit architecture.The link below shows the compatibility of this game with Windows 7.Method 1.We must ensure that the edition of the game must correspond with the operating system.

If you use 64-bit in this game, you need the 64-bit Windows to install it.Method 2.

If the above information matching I you recommend to start the computer in clean condition and then try to install the game.

See the article below for instructions on how to start your computer in a clean boot state.

How to troubleshoot a problem by performing a clean boot in Windows Vista or in Windows 7

http://support.Microsoft.com/kb/929135

Note: When the diagnosis is complete, don't forget to reset your computer to normal startup. Follow step 7 in the above article.I hope this helps.Thank you, and in what concerns:

Shekhar S - Microsoft technical support.Visit our Microsoft answers feedback Forum and let us know what you think.

If this post can help solve your problem, please click the 'Mark as answer' or 'Useful' at the top of this message. Marking a post as answer, or relatively useful, you help others find the answer more quickly. -

LabVIEW RT running on the cRIO-9068, LabVIEW FPGA programming mode. Citing the FPGA VI open (from the RT program) returns the error-61017 code. Everything seems to work OK, but unexplained errors keep me awake at night. I looked everywhere but could not find an explanation for this error. Did anyone here know what makes?

I'm glad to hear that you understood.

I know the error codes are out there somewhere on the internet, but I usually do it is go to the Help Menu in LabVIEW, select error explain and enter the error Code I'm interested.

Sebastian

-

I have microsoft flight simulator X deluxe edition on my laptop for 8 years and more (windows xp). It has completely stopped working so uninstalled the software. When I tried to reinstall with the original disks, I received the following message: "cannot install on your version of windows, please contact software manufacturer.

Help, please

Hi Laurei,

Thanks for posting in the Microsoft community! You have reached the right forum for your question.

I suggest you try the steps from the following link:

Microsoft games: InstallShield Error Messages

http://support.Microsoft.com/kb/910816See also: http://www.Microsoft.com/games/flightsimulatorx/default.htm

Hope this information is helpful and let us know if you need more assistance. We will be happy to help.

-

Storm Simulator has Java runtime error

When I try to use the Simulator for Storm 9500 and 9550 I get a java error message. "Error Eror - BlackBerry Smartphone Simulator, inside the JVM application: 0x00000008 access violation reading."

This occurs when the JDE tries to connect to the Simulator. This is before you get to the main screen or my application start.

Does anyone know what causes this or how to fix it?

Thank you

Gerry

I see it occasionally.

First try this: stop the JDE, reboot, then the "clean" and "build together", restarting the Simulator.

If this does not work:

Stop the JDE

go to the directory of Simulator

Run clean.bat

Restart the JDE

Select file / delete file Simulator / Erase file system

Now clean & rebuild and everything should be back to normal.

-

Activation of Flight Simulator Acceleration 1-80004005 error

I reinstalled the expansion pack X Accelerator microsoft Flight Simulator, but it won't let me enter the product key. I open the game, but it gives an error message 80004005-1 on activation. It worked fine on my old computer with XP but now my new computer has Windows 7. There is no support for this phone. Can you help me?

Hello

You did changes to the computer before the show?

Method 1:

You can try the steps in the link and check.

"Solving the problems of activation for Microsoft games and mapping programs.

http://support.Microsoft.com/kb/960480Method 2:

Solve problems with activation for Microsoft games problems and mapping programs http://support.Microsoft.com/kb/960480Note: this section, method, or task contains steps that tell you how to modify the registry. However, serious problems can occur if you modify the registry incorrectly. Therefore, make sure that you proceed with caution. For added protection, back up the registry before you edit it. Then you can restore the registry if a problem occurs. For more information about how to back up and restore the registry, click on the number below to view the article in the Microsoft Knowledge Base.

How to back up and restore the registry in Windows:

http://Windows.Microsoft.com/en-us/Windows7/back-up-the-registryReference links:

"Activate your Microsoft games and mapping programs.

http://support.Microsoft.com/kb/927007/daFrequently asked questions on how to enable Microsoft Games for Windows, streets and trips and Mappoint

http://support.Microsoft.com/kb/927007

You receive an activation message after you play Flight Simulator X for 30 minutes http://support.Microsoft.com/kb/925723/

If the problem persists, then I suggest you to report the problem to Microsoft Flight Simulator Games Forum for assistance.

Maybe you are looking for

-

As I installed the latest OS 10.0.1 on my iPhone, the Pandora app does not work.

As I installed the latest OS 10.0.1 on my iPhone, the Pandora app does not work.

-

My ID apple has been disabled and I can't restore it because I forgot my security question, please help I can't update my iphone because it will need for my apple for activation ID. Please help me.

-

No one knows how to delete a column, or changing the values in this column and leave the rest in a csv file? Example: CSV file has 70 rows and 40 columns. To remove a column or change its values. Thanks in advance.

-

How to transfer photos from Samsung sch-u360 to the computer

Original title: phone samsung sch-u360 How can I download pictures to my computer from my samsung sch-u360 phone?

-

HP g62-361tx: using 65W adapter instead of 90W adpater will raise problems

I use a laptop Hp G62-361TX. Can I use 65W adapter for my laptop instead of 90W Adapter for charing? Problems will arise with 65W adapter? Please tell me