FPGA IO Module error, recognizes NEITHER 5751 in LabVIEW

Here is my configuration:

- Windows 7 sp1, 64-bit

- LabVIEW 2013 sp1, FPGA, real-time

Which is connected via an Ethernet cable to:

- Chassis SMU-1078

- SMU-8135 embedded controller

- SMU-7961R FPGA x 2

- Module e/s NI 5751 x 2

- LabVIEW time real 13.0.1

- NOR-DAQmx 15.1.1

- NOR-RIO 15.5

- OR PXI Platform Services 14.1.0

NOR, Max the FPGA and 5751 adaptation Modules appear as a gift. But in my LabVIEW project, IO Modules always show an error. I chose the good 'NI 5751' option, but the State still shows this:

I tried to restart the chassis and the computer. I tried selecting another Module of e/s and then back by flipping. I am also unable to compile the code example on the FPGA (Xilinx errors).

Any ideas?

The status shows you which adapter module expects the bitfile who is currently on the fpga module. The reason why it says no is probably because you have not deployed anything the fpga target since he powered and there just the default image loaded on it. Try deploying a bitfile to which has been compiled to work with a 5751 and you'll be fine.

I do not know why you can not compile the 5751 get started example however. I'd make sure you have all the build tools installed correctly. What are the mistakes do you receive when you try to compile? Such problems are sometimes easier to solve by phone if you want to open a support on ni.com/support ticket.

Tags: NI Software

Similar Questions

-

RTF model error: compilation in the hidden module error.

I use MS Word 2007 to change my rtf models.

After installing the patch PS2 for MS Office I can't edit the rtf models more.

When I try to edit any field in the model I get a message box with the 'Microsoft Visual Basic' header and the message "compilation in the hidden module error: Module_editFF.

I noticed that the BI Publisher tab is no longer visible in the toolbar. I uninstalled the add-on and reinstalled again, the question remains.

Any help will be appreciated.

Thank you.If you do not see the BI Publisher tab, then go to MS Word-> Word Options-> Add - ins-> manage-> select Add-ins Word and make so that the "Templatebuilder.dot", TBCrosstab.dot etc. are checked.

Thank you

Bipuser -

Hello

I'm under LV 2010 SP1, I don't know what version of the FPGA module I have, but I think it has been upgraded during the SP1 update. The error is less. It refers to two of the four globals, I use communicate a FPGA timed to a non-timed loop loop.

My code has compiled since the upgrade, but not since the addition of the globals...

I'll appreciate any help on this.

Roger

An internal software error occurred. Please contact National Instruments technical support on ni.com/support with the following information: nirviUIDToObject.vi

reference object get error for UID. All the analyzed text:

-61103 1 NI. Munge.S3 Global.vi_FPGACompileCopy00000001.vi 2 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 4624 Global Variable: ' NEITHER. Munge.S3 Global.vi_FPGACompileCopy00000001.vi' 3 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11890 Global Variable: ' NEITHER. Munge.S3 Global.vi_FPGACompileCopy00000001.vi'

-61103 1 NI. Munge.S2 Global.vi_FPGACompileCopy00000001.vi 2 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11881 Global Variable: ' NEITHER. Munge.S2 Global.vi_FPGACompileCopy00000001.vi' 3 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11878 Global Variable: ' NEITHER. Munge.S2 Global.vi_FPGACompileCopy00000001.vi'

-61103 1 NI. Changed Munge.AO Global.vi_FPGACompileCopy00000001.vi 2 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11906 Global Variable: ' NEITHER. Changed Global.vi_FPGACompileCopy00000001.vi Munge.AO' 3 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 4622 Global Variable: ' NEITHER. Changed Global.vi_FPGACompileCopy00000001.vi Munge.AO' 4 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11905 Global Variable: ' NEITHER. Changed Global.vi_FPGACompileCopy00000001.vi Munge.AO'

-61103 1 NI. Munge.S3 Global.vi_FPGACompileCopy00000001.vi 2 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 4624 Global Variable: ' NEITHER. Munge.S3 Global.vi_FPGACompileCopy00000001.vi' 3 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11890 Global Variable: ' NEITHER. Munge.S3 Global.vi_FPGACompileCopy00000001.vi'

-61103 1 NI. Munge.S2 Global.vi_FPGACompileCopy00000001.vi 2 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11881 Global Variable: ' NEITHER. Munge.S2 Global.vi_FPGACompileCopy00000001.vi' 3 1 C:\NIFPGA\compilation\CardiaLen2_FPGATarget_CardiaLen2IO(FPG_86098CD2\MungedForFPGA\NI. Munge.CardiaLen2 IO (FPGA).vi_FPGACompileCopy00000001.vi 11878 Global Variable: ' NEITHER. Munge.S2 Global.vi_FPGACompileCopy00000001.vi'

-61103 1 NI. Changed Munge.AO Global.vi_FPGACompileCopy00000001.vi 2 1 Snip...

Unfortunately, even if you can guarantee that the written word never happen at the same time if you write only once per carton, LabVIEW FPGA currently only has not the ability to position the system globals arbitratio for multiple entries on the diagram can cause this error. What I would say is that you write the overall each iteration of the loop outside the structure of the case and that he wire simply the value on a tunnel on the structure of the case. This will allow you always change the value each time through and will eliminate the error of code generation.

If you want to send your comments about this particular use case of LabVIEW FPGA R & D, I would recommend that you post your idea in the Exchange of ideas of LabVIEW FPGA.

-

Compilation of FPGA - real formal error on the cost of the port cannot be an expression

Details:

ERROR: HDLCompiler:192 - "C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd" line 1408: real formal on the cost of the port cannot be an expression

ERROR: HDLCompiler:854 - "C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd" line 69:Unit ignored due to previous errors.

File VHDL C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd ignored errors

-->The compilation happens to step "using the unit felt" but then stops soon after with a compilation error.

The line in question (1408) refers to the output of a "Reinterpretation FXP" node with the text

Cost => (others-online '0'),

in the part of port of the code card. This is the output of the FXP reinterpret node is directly connected to an indicator in a VI sub whose output is then entered directly at a crossing high multiply node. The code is part of a cosine sine LUT I programmed. She used to compile without a problem, but I think I know where is the problem. In one case, I have used only the sine of output of the algorithm and theory, Xilinx can optimize away from the part of cosine. I have two instances of this VI in my code and looking at those generating any errors, the output is associated with a cosine indicator.

Cost-online s_Cosine_2434,

It seems that the track is essentially optimized away, but the compiler, Xilinx has a problem with the flag being present on the sub - VI but the idnicator is not used anywhere. As a result, the cost gets set to an invalid value. I guess close to reinterpret it FXP at the exit of the Subvi is an important aspect of this problem.

I think I know enough now to fix this (remove the path manually by duplicating the sub - vi), but it may be useful for future bug fixes feedback in the FPGA module. It is not the first time that this kind of removal of incorrect code me has given problems, but this is the first time I could clearly identify the problem.

Shane

Hey Shane,

Looks like someone filed a bug report on it a month or two ago. It's the CAR # 475397 if you want to check for it in the list bug fixed for 2014 SP1.

-

NEITHER 9512 with Labview FPGA Interface

Is it possible to use the NI 9512 stepper with Labview FPGA interface drive unit or is it only possible to use it with the interface of scanning? When I try to add the module to a FPGA target, I get an error telling me that Labview FPGA does not support this module with the latest version of NOR-RIO, but I have the latest version of OR-installed RIO.

Hi Checkit,

You're right - the 9512 cannot currently be used in FPGA. There is an error in the documentation. The 9514 and 9516 can, however.

-

Equium A100: Cannot open 'Accessibility' - complete common Module error

Toshiba assist on my Toshiba Satellite A100 laptop, I press the accessibility of the icon. He then came with the error 'Common Module complete'.

Help would be appricitaed.

Hello

The common modules is a Toshiba application that is necessary if you want to use and install another Toshiba programs such as controls for example.

You simply remove the modules common and after restarting the laptop new install program.

If you won't find the common modules in the area add & remove the list of programs and you will not be able to remove it then just reinstall.

It helps to... -

Satellite A100: I am not able to use the keys FN - common module error

HY,

I have a toshiba satellite A100 series and I have a problem:

I'm not able to use the fn functions (for example fn + f9 to turn off the touchpad or fn + f3 to the eve and so on...) and I got an error concerning "common module.A dialog box told me that the common module is closed...

Someone knows this problem?I'm sorry for English...

Thank you

Hello

I put t know why this error message and why the common modules stopped working, but to my knowledge, the common modules are needed to run and use the FN keys for example.

So here is my advice;

Go to Toshiba's European diver page, choose the common law modules, download, unzip, and reinstall it again!After restarting again the FN keys should work again.

Best regards and good luck

-

cFP-AO-200 analog output module (error-33180)!

Hello everyone

I use the CFP 1808 Bank as well as other such modules that HAVE 111 and enter I-110, I recently bought a Module AO-200 out of the currents of the order of 4-20 mA, I connected the module to the Bank and updated the device of the MAX Software, then I opened the Getting Started/Analog Output.vi leave examples in Labview to test 2011 map the VI returns an error with the code 33180 for me, I don't know what the problem is, but I tested the card with the MAX and wrote the values to it successfully.

Can someone tell me what is the problem with my VI

Thank you

I was able to reproduce your error. You must select 'All' in the Point IO Point field for this vi.

-

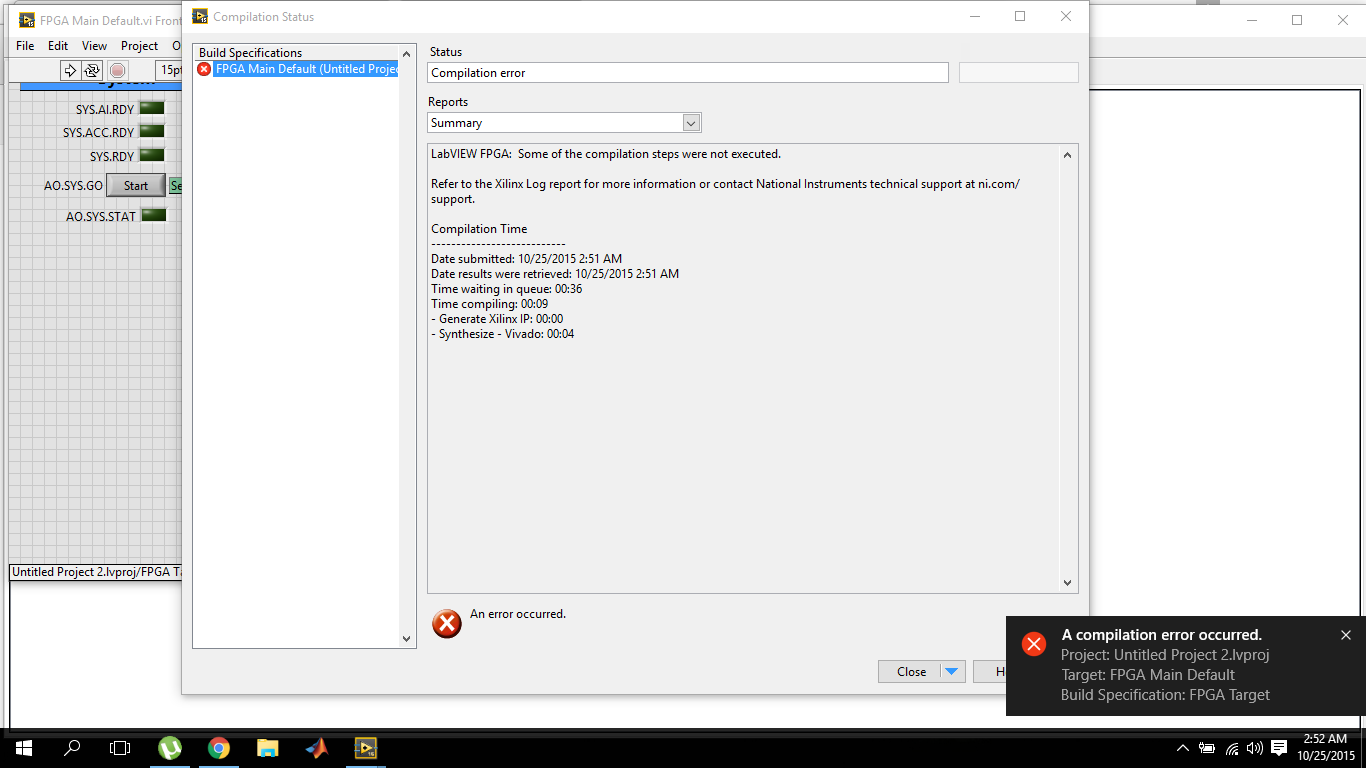

LabVIEW FPGA, 2015 compilation error

I've recently switched to LabVIEW 2015 and I'm working on OR myRIO. So also installed myRIO 2015 bundled software. The problem I have is that the compilation of fpga fails within 10 seconds.

and the target Xilinx journal report is empty

The first time when I tried to compile on 2015 version, it failed and the message box that failed came alongwith the avast antivirus warning for malicious activity. I reported it as wrong and now I tried several times with avast shield disabled control, but the results are the same. While the version of labVIEW 2014 works very well.

Now, I'm sure that there is something wrong with the installation of Vivado because this dll is part of it. The dll must be default in the2014_4\lib\win32.o directory C:\NIFPGA\programs\Vivado if you are using an operating system for 32-bit AND also in C:\NIFPGA\programs\Vivado2014_4\lib\win64.o If you use a 64-bit operating system. If the dll is not here, it is probably that the anti virus (I've never seen what happens to Xilinx but I have for other stuff).

I'm emphasizing the 2014_4 because LabVIEW 2015 uses Vivado 2014_4 while 2014 LabVIEW uses Vivado 2013_4. Since you have also installed LabVIEW 2014, you must have 2013_4 as well and if it works, you will find the dll I just wanted you make sure you check the correct directory for the Vivado 2014_4.

Download and install (reinstall or repair if already installed) 2015 LabVIEW FPGA Module Xilinx tools Vivado 2014.4. You can also use the DVD Setup if you have. It would be a good idea to do the installation with the disabled and even anti-virus try the first compilation the same. Try and let me know if the problem persists.

Kind regards

-

Hello

I'm pretty new to Labview FPGA programming. In my project, I would like to synchronize the ADC of the NI5751 to an external frequency normal provided by the "10 Mhz REF in" SMU-1075 chassis. Is it possible that the sampling frequency of 50 MHz of the NI5751 is driven through the 10 MHz? And in addition, the "PXI Clk10 MHz" that can be included in the base of the FPGA project clock is derived from the "10 Mhz REF in"?

Thank you.

Kind regards

Thomas

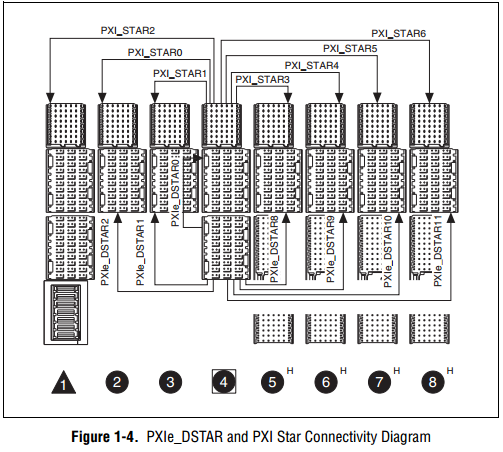

Hi Thomas,

Yes you´re good it s 3, 3V to the CLKIN to the 5751. Anyway, use the DSTARA approach.

In the manual of your chassis SMU-10xx, you will find a section called 'timing Slot System.

in the chapter of the implementation on the road gives you the delivery of the DSTARA into the slots on the frame.

For example, SMU-1082:

see you soon

Marco

-

stuck FPGA compilation, no errors

Hello

I wrote a LabVIEW FPGA 8.6.1 program (I have written several, this is my most recent). When I run it on the development computer it seems to work fine without any errors. When I try to compile, however, it still stalls on this part:

'Analysis of generic entity

library ( Architecture). This isn't feeze (the compiler is always updated time and you can see it working). It just doesn't progress no further than this point. By chance, does anyone know what could cause this? I know that maybe it's a little vague, sorry. Thank you!

Nevermind, I figured it. I had a knot of analog input within a For loop. This wire entry (i.e. given out the analog input node) was connected to a tunnel auto-index on the loop For I have just disabled automatic indexing on this tunnel and everything seems to compile fine now.

-

for the FPGA fifo compilation error

Hello

I downloaded the example RS232 FPGA program and tried to make a small change to it. The original is like that; See attached file "beforeModification.PNG".

I wanted to reread the amount of data still in the FIFO where I had read everything so I changed it to that. See attached file "withModification.PNG".

The target is using the compiler 13.4 Xilinx 7841R. I'm not in the section summary with the following error message;

Details:

ERROR: HDLCompiler:1566 - "C:\NIFPGA\jobs\K7I4YEj_RQC5mWo\NiFpgaAG_FPGA_Main.vhd" line 869: Expression has 11 elements; official ocountfullcount wait 10I'm currently running;

LabView 2012 SP1 f3

12.1, the R Series multifunction RIO of NOR

I'm doing something wrong?

Thank you

Andy

The problem disappeared when I copied the source files in a different folder

-

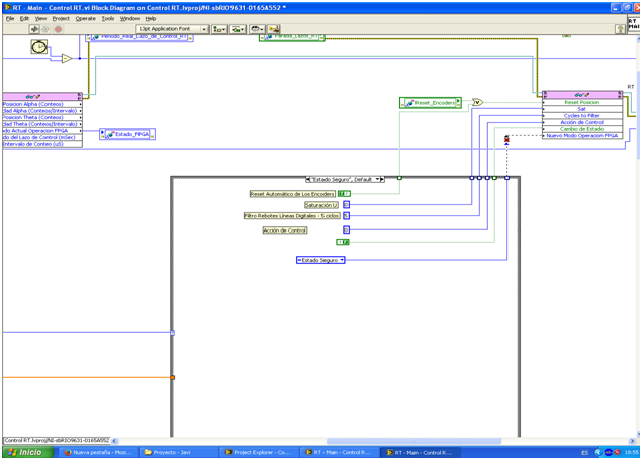

Broken thread - FPGA Interface Node error

Hello

I am programming my application of RT and I get this weird error:

As you can see, I'm trying to set the value of a FPGA control (which is a typedef enum) and I get this strange cut wire

for me, error.

I was looking for a solution in the forums but I luckily able to get a... Could someone help me?

Thank you!!

PS: The error message was "the type of sink is zero" that is false, as already defined in the FPGA vi.

Solved.

To the right, it was like if I've changed some of typedefs and who did not have in mind. Recompiling solved the problem.

-

Simulated FPGA i/o error-61399 Recive

Hello

I'm trying to simulate a cRIO-9073 on my development computer. I want to use the simulation I / 0 features. If I use the random data, I have no problem to run my simulated VI. If I use the option 'Use Custom VI for FPGA of IO', I always get the error 61399.

I already had a look at this link but and use a model of VI, but that doesn't change anything. I also had a glance on the tutorial explaining how to do it but without success...

Any idea?

Thank you!

Hi vgravel,

Did you also know that the "Custom VI has been set for each element of I/O that you use in your FPGA code?

FLash

-

The export of clock FPGA embedded modules e/s

Hello

Is it possible to export the clock embedded FPGA, or derivatives, all Modules e/s?

Greeting

Matthias

I assume that this refers to one NOR 9225, 9227, module x 9229 or 923 in a CompactRIO chassis. You cannot export the clock aboard 40 MHz to these modules. One of the modules must be a master, and then you can sync the time base for all modules by setting the Source of the master time base in the Module C Series Properties dialog box.

Export the 40 MHz clock would not allows you to acquire data much faster still. Depending on the frequency of the time base, you can calculate using NI 9225 manual Instructions and specificationsdata rates. However, you are still limited to sampling frequencies in the specified data range. For a base from time to time as 12.8 MHz, maximum possible sampling frequency is approximately 51.2 kech. / s instead of the available 50 kech. / s with the time of 12.8 MHz base.

Maybe you are looking for

-

The latest version of Firefox just downloaded 17.0 prevents Norton Identity safe to fill my usernames and passwords. Identity Safe still appears in the menu bar and will continue as an add-on, but it does not fill in the usernames and passwords. How

-

In a Satellite A100-599 Express card slot

Hello.. I own a laptop Satellite A100-599. Many sites on the internet, I see my laptop with a PCMCIA type II port AND a slot for card together Express. But on the toshiba site there is no explanation like that.What is the law? Anyone using an Express

-

telstra icon appears not central in the menu of the Office start icon

the shell of telstra appears not central in the menu of the start desktop icon.

-

Driver Bluetooth for HP Pavilion 15-e010sp running on windows 8.1

Hello I upgraded my windows to 8.1 and I donot have bluetooth now. Grateful if you can help me. I have a hp pavilion e010sp 15. Thank you

-

Replacement of Smartphones blackBerry storm

my replacement storm came today. They said to keep all my VAC like battery, media card, sim card. now the replacement storm came with an installed sim card, should I leave this one in the storm or replace it with one of my old storm? Thanks in advanc