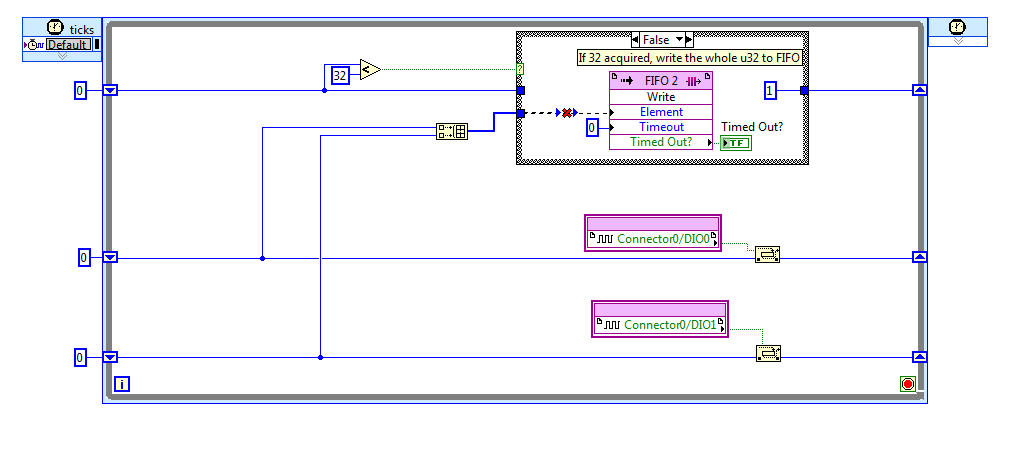

U64 with DMA FIFO of the target to the host

I have to I have 2 signals in what I want to join the numbers to come. When I do the number to boolean and vice versa, the results are U32. Combine the two numbers, you get U64. However, the DMA transfer may only take U32. If I change the results to a U16, then I don't see the negative values of the signal. Is there a way to do this? I know I could use a make a table, then put it in the loop for, but it seems to take up space and I'm running out on the side of FPGA.

Thank you

Guilio

You have assumed correct. I expected 8.5 8.6. I'll wait until then.

Thank you

Guilio

Tags: NI Software

Similar Questions

-

How to choose the maximum number of items for DMA FIFO to the R series FPGA

Greetings!

I'm working on a project with card PCIe-7842R-R series FPGA of NOR. I use to achieve the fast data transfer target-to-host DMA FIFO. And to minimize overhead costs, I would make the size of the FIFO as large as possible. According to the manual, 7842R a 1728 KB (216KO) integrated block of RAM, 108 000 I16 FIFOs items available in theory (1 728 000 / 16). However the FPGA had compilation error when I asked this amount of items. I checked the manual and searched online but could not find the reason. Can someone please explain? And in general, what is the maximum size of the FIFO given the size of the block of RAM?

Thank you!

Hey iron_curtain,

You are right that the movement of large blocks of data can lead to a more efficient use of the bus, but it certainly isn't the most important factor here. Assuming of course that the FIFO on the FPGA is large enough to avoid overflowing, I expect the dominant factor to the size of reading on the host. In general, larger and reads as follows on the host drive to improve throughput, up to the speed of the bus. This is because as FIFO. Read is a relatively expensive operation software, so it is advantageous to fewer calls for the same amount of data.

Note that your call to the FIFO. Read the largest host buffer should be. Depending on your application, you may be several times larger than the size of reading. You can set the size of the buffer with the FIFO. Configure the node.

http://zone.NI.com/reference/en-XX/help/371599H-01/lvfpgaconcepts/fpga_dma_how_it_works/ explains the different buffers involved. It is important to note that the DMA engine moves data asynchronously read/write on the host nodes and FPGAs.

Let me know if you have any questions about all of this.

Sebastian

-

6 fusion works with El Capitan in the host operating system?

I saw the thread on the Fusion 7 and El Capitan, but I wonder about the Fusion 6 and El Capitan. I know that El Capitan works as a guest OS with Yosemite as the host and the latest version of Fusion 6 (I'm under the commercial version of El Capitan in a virtual machine on my Yosemite iMac running), but I have not really improved none of my systems to El Capitan again.

Thank you.

I use 6 merger with AE Capitan. It seems.

-

Update ESXi with VCenter VM on the host?

I am trying to upgrade my host ESXi 4.1 4.1 Update 1, but the VCenter VM lies on this matter. I have to do to make sure that the DB VCenter is not corrupt, or can I just stop, put the host in maintenance mode and using esxupdate?

With shared storage, you can:

- Make sure that you have not activated the mode of locking for guests

- Stop the vCenter Server VM

- connection to the host on which it is running and remove it from the inventory

- connect to the host of the second, browse the data store and add it to the inventory

- vCenter Server on the second host market

Generally, you will use Update Manager (if you are using vCenter Server), but in cases where this is not possible, you can also use vihostupdate.

André

-

Upgrade to 4.1 - U1 with stains staged on the host

I want to upgrade the two hosts that are running 4.0 to 4.1 U1 U2. A host has some stage patches for 4.0. Is it possible to not restore the patches and apply the upgrade? They will delete after the upgrade? Or what I need to fix these updates staged, and then restore the upgrade?

Thank you

You can go ahead and clean up the upgrade of base without cleaning up the existing staging patches.

VUM will return the error incase there is no freespace available for upgrade packages.

-

Reading and arraya thro DMA FIFO (PCI7813R)

Normal 0 21 false false false SL X-NONE X-NONE MicrosoftInternetExplorer4 / * Style Definitions * / table. MsoNormalTable {mso-style-name : « Navadna tabela » ; mso-tstyle-rowband-taille : 0 ; mso-tstyle-colband-taille : 0 ; mso-style-noshow:yes ; mso-style-priorité : 99 ; mso-style-qformat:yes ; mso-style-parent : » « ;" mso-rembourrage-alt : 0 cm 5.4pt cm 0 5.4pt ; mso-para-marge-haut : 0 cm ; mso-para-marge-droit : 0 cm ; mso-para-marge-bas : 10.0pt ; mso-para-marge-gauche : 0 cm ; ligne-hauteur : 115 % ; mso-pagination : widow-orphelin ; police-taille : 11.0pt ; famille de police : « Calibri », « sans-serif » ; mso-ascii-font-family : Calibri ; mso-ascii-theme-font : minor-latin ; mso-hansi-font-family : Calibri ; mso-hansi-theme-font : minor-latin ;}

Hello

Location:

I read 5-position encoder with PCI7813R. The position of encoder data format is I32. Following is each position encoder converted to U32 and build in a table by using "build the array function. Finally this table guided loop where I write it in DMA FIFO uses "FIFO write function. FIFO depth is equal to 16383 and Timeout to 0.

Side host I'm reading this table of DMA FIFO. The host FIFO depth is set to 1000000. I use 'Method Invoke with FIFO read' to read data from the FIFO. I read 10000 elements each time. Data output is converted to I32 and guided an extension to "decimate the 1 d array function. I use 5 indicators to represent the positions of Encoder on the host side.

And now the problem:

Position 1 Encoder shell displayed on indicator 1. But every time I close my application and run it again this position appears on the other indicator. Sometimes is the position of the Encoder 1 shown on the 1, sometimes on the indicator 5 indicator, sometimes on indicator 3... Although this position of the encoder is shown every time on the other indicator it has correct values. What I'll do as I will always receive encoder position 1 on indicator 1, position of the Encoder 2 Indicator 2...

My application has been built according to these instructions:

http://zone.NI.com/DevZone/CDA/tut/p/ID/4534

TNX,

Gregor

Normal 0 21 false false false SL X-NONE X-NONE / * Style Definitions * / table. MsoNormalTable {mso-style-name : « Navadna tabela » ; mso-tstyle-rowband-taille : 0 ; mso-tstyle-colband-taille : 0 ; mso-style-noshow:yes ; mso-style-priorité : 99 ; mso-style-qformat:yes ; mso-style-parent : » « ;" mso-rembourrage-alt : 0 cm 5.4pt cm 0 5.4pt ; mso-para-marge-haut : 0 cm ; mso-para-marge-droit : 0 cm ; mso-para-marge-bas : 10.0pt ; mso-para-marge-gauche : 0 cm ; ligne-hauteur : 115 % ; mso-pagination : widow-orphelin ; police-taille : 11.0pt ; famille de police : « Calibri », « sans-serif » ; mso-ascii-font-family : Calibri ; mso-ascii-theme-font : minor-latin ; mso-hansi-font-family : Calibri ; mso-hansi-theme-font : minor-latin ;}

Sorry Jochen, I placed the function reset at the end of my routine. L I corrected (put it on the beginning of the routine) and now it works as it is supposed to be.

Thanks a lot again!

Kind regards

Gregor

-

How is managed using DMA FIFO (target host) host matrix

Hi people,

I'm trying to pass an array of values of the host to the FPGA using DMA FIFO. Let's say 20000 items in the table. My FIFO host side can contain only 16000 items or almost. The data will be written element by element regardless of the size of the table or do I need to partition the table in small paintings before writing the FIFO method? Let's say that I write for the FIFO with berries small, 1000-element. The FIFO will read 1 element both of the side FPGA so the stream is blocked until I have at least 1000 free items on the FIFO method write, how he writes every 1000 the next setpoint at the same time? Or target values will be written permanently as soon as the individual elements are erased by the number of available items to write?

Hi Nathan,

Sorry for the late update, but I just thought that I should follow. I followed your advice and try it tested just for me (I probably should I have done it before posting). Turns out that the data table will write even if there is not enough empty elements to contain the table in its entirety. However, it always crashes until enough information is read and erased from memory on the side FPGA for the whole table. So if it's data that are constantly being played, it's always better transmitting data through in the form of smaller tables if you do not want to increase the amount of memory FIFO host OCCUPIES on your system. However, if you can afford the memory while you mentioned, you can always increase the depth of the FIFO on the host side. As I understand it, try to write more big berries to a host to target FIFO buffer does not diminish overhead costs (as is the case with a target to host FIFO) as it still passes an element at a time to the FIFO of FPGA-side without worrying.

Thanks again for your help.

Kind regards

John has

-

Target to host DMA FIFO not compensation when they are arrested

I use a PXI-7841R (Virtex5) and 32-bit data to the host via DMA FIFO transfer. When you read the FIFO on the host for the first time, the data are "stale" (which means that it is not what is currently coming in the FPGA, but what came in a few seconds ago stale). I tried both a stop and a configuration for clear memory FIFO before I use them. Documentation on one or both of these so-called clears the target and host the FIFOs. Does not help in both cases. With readings of the second and the following, FIFO has then 'valid' (same data as it appears on the FPGA entry node). What is curious is that each reading exactly the same thing:

- Stop the FIFO (must erase all data)

- Elements of reading 375 of the FIFO. (repeated playback of the FIFO)

Also interesting: FPGA FIFO is implemented for 255 elements. The first 255 items host-side contain the data "stale" on the first reading. It reminds me of the never erased FPGA FIFO.

Answered by support OR. The documentation for the FIFO, stop and configure FIFO is in error. Cars of documentation will be written against them.

Solution:

These methods remove only the FIFO on the side host. Data FPGA FIFO must be read following until no element.

-

Target to host DMA FIFO - actual number of items

Hello

I have a target of FIFO of DMA host using memory block. Under FIFO properties, "the actual number of elements" is indicated as part of 1023.

But when I wire a remaining indicator to the 'elements' of FIFO in the host of VI, said 16384 elements. And I read a lot of part of the FIFO.

Why is the actual number of items that much more?

The data type is 32. And I have a high-7965R FPGA.

See you soon.

There are two different buffers for the FIFO: one on the host, the other on the FPGA. Data is copied from one to the other. It may be more space allocated on the host, because there are more memory available here and the loop of the host, probably runs more slowly than the FPGA. You can set the host using a node to invoke FPGA FIFO set the buffer size value.

-

Hi guys!

I am writing here after many days of attempts without success...

My request is 'simple', send data from the Panel of Labview RT within a DMA FIFO target host. Then the FPGA core receives data and imported through a knot of VHDL processes, and then after the data is pointing to the Labview RT through a target to host DMA FIFO.

I tested my node VHDL simulation mode in Labview FPGA where data sent by a target scope THAT FIFO and just work fine.

But when I try to run the node VHDL in the real target with data from the RT by DMA FIFO basis, it won't. I already do some checks:

-Data are properly sent through the host target DMA FIFO;

-The data are correctly received in the FPGA base;

-The data are correctly sent to the node VHDL;

-Result of the node VHDL are correctly sent to the heart of the RT through the target to host DMA FIFO;

-Result are correcly received in the heart of the RT, , but the result is false and absurd. But I have proof that my node is semanticly correct with my mock test

So my question: are there reasons to see my work VHDL nice knot in simulation mode and not in mode real target with data from the base RT by DMA FIFO taking into account data Transfer between DMA FIFO work well in both sides? Is there some sample available with data send RT FPGA-based via DMA and data processing with a knot of VHDL and returned to the RT kernel to inspire me?

I can't post my screw here because I work for a company, I use a MyRIO with Labview FPGA 2014 target.

Thank you guys! I am available for some details on my implementations.

Afghow.

Hey!

Thank you for your answer but I solved my problem. Indeed, at first, I tried to make a knot of Combinatorics (without clock) pure, but the problem seemed to come from that.

I modified my node in order to incorporate a clock, according to the prescriptions of this white paper: http://zone.ni.com/reference/en-XX/help/371599K-01/lvfpgaconcepts/ipin_prepare_ip/ . And now, every thing seems to work well.

The question remains why the combinatorial node has worked in simulation mode en not in the actual target?...

But for people with the same problem, I suggest add them a CLK and check an edge of entry with rising_edge (CLK) and if it does not, add an input signal to check if the input signals are valid or not.

Afghow.

-

I want to transfer data to my FPGA using a DMA FIFO. The FIFO is 1024 elements, but can I write bigger than that of the side pieces PC? I don't know if the PC actually allocates a larger block of memory for this purpose?

I'm sure that you can set DMA on the side host is greater. There is a node of configuration DMA you can use host-side to define the size of the FIFO on the side host. The size is set in the hardware on the target side.

-

Transfer 1 d table using DMA FIFO of FPGA

I'm transferring a table 1 d of two U32, with a configured U32 FIFO for the host.

but I get the error because of the connection to different types of terminals,

It seems very simple, I found a lot of samples with a very similar treatment here, but I don't see the problem?

There is a loop of indexation of array... The write operation is therefore the element by element.

The operation of reading (on the host) can read several items at once (--> a table).

-

Hello

I'm developing an app for the compactRIO systems. I want to implement a heartbeat in the FPGA code that detects if the host vi gave up. I also want the FPGA vi at the stop with a stop of the host vi command.

I implemented the heartbeat signal within the host vi and the heartbeat counter is located in a loop of the single cycle timed (SCTL) in the FPGA vi. However, I have other loops while in the FPGA vi (b/c I/o analog are not compatible with the SCTL) and so I need to stop several multiple loops with a stop order from the inside of the loop cycle timed (by opposition from a user input, what you can do with a local variable).

As I have now, when I download and run the code to my compact goal of RIO, and I abandoned the host vi (and not by pressing the stop button), the code in the SCTL stops, but on the other the loop is not. Can anyone help?

Greetings Andrew P.

I took a quick look at your code, and while I'm not completely sure of the cause of the behavior that you are experiencing, I noticed a few things in your FPGA code. First of all, it seems that you use an appropriate method to report the other loop the SCTL is stopped due to the delay of heartbeat. Secondly, it seems that the logic around the heart rate monitor can be a bit off. Currently, you are taking the current value of the entry of Heartbeat/command and comparing it to the value returned by the shift register using a not equal to vi comparison. This allows to detect a change in the status of this entry if the shift register is providing the value of previous to this entry. However, it seems that you take the value of the comparison is not equal to to fuel the shift register, rather than the current value of the control of heart rate. What happens if you change?

Kind regards

Michael G.

-

I have 8 Fusion installed on Yosemite. I have a guest VM Windows 10 and works well. When I install El Capitan, do I have to recreate the Windows 10 VM guest or it should run with El Capitan as the host operating system? Thank you!

Hello

Upgrade to El Capitan shouldn't matter to your guest operating system, it must continue to operate as is.

However, DO NOT wipe your drive on the update as then it might erase your VM.

So best thing - as always - is to make a backup of your VM - with the virtual machine closed down and merge not running - before the upgrade to El Capitan.

--

Wil

-

How can I set up 2 physical network cards, 1 for the host and 1 for vm?

Hello

With the help of VMWare WS 7.1. I have a physical machine with 2 network as the host cards. Currently only one of the cards network is connected to the network.

It hosts a SBS 2008 Server virtualized (while we prepare permanent news of the home server). I know not to leave the virtual machine SBS see doamin on the network controllers.

I want to give a static IP address on one of the network adapters on the virtual machine and allow the host have the map of others.

Can someone give me the steps or point me to the instuctions?

Or is it better to use a NETWORK card? The virtual machine is currently using a NIC a nic virtualized in bridged mode.

Thank you!

1. disable automatic bypass on VMnet0 in network virtual and configured Editor to use the map NETWORK active on the host.

2. in the Virtual Machine settings > set it to network adapter connected by a bridge.

3. in the guest operating system, configure the IP address as you would on a physical computer. Take a look at: Managing Your Windows Small Business Server 2008 Network

It's as simple as that.

Maybe you are looking for

-

How to know Foxfire DO NOT keep in memory a login and a password that I said previously to memorize?

Previously, Foxfire popped up and asked if I wanted it to remember a certain username and password combo, I do a lot for some Web sites. However, I decided since this present a risk to the security of a site, and I want it ask me each time to connect

-

Compensation of host EEPROM on NI FlexRIO 6585 adapter

I'm trying to clean up memory host on 6585 LVDS adapter OR using methods descrived in the letter of volatility http://digital.ni.com/public.nsf/allkb/4B0A422D33D86C8986257788006ED0DE. The document indicates that no Volatile memory size in 2 KB. When

-

I guess the first problem I have is that I came across this forum to get an answer to a question from windows 7, and all I can see are XP and Vista of questions and answers. It's great, but I have the update above installed on Vista (Ultimate x 64).

-

Have a Live View remote problem...

I use the remote software a lot and started having a problem in Live Mode when connected to the laptop... If I am connected there is no problem, but when I go to Live View to see what the camera sees it running a little and then give a "Connection Lo

-

I plan to sign up to page 50 per month plan. My question: what constitutes a printed page? In others, if I print 10 pages each page consisting in 2-3 lines only, this is '10 printed pages'?