derived clock problem?

I am tring to derive a clock to 25 MHz using an NI PXI-7842R and labview project will not allow exact clock

But when I try to do the same thing for a PXI-7830R target, I'm successful.

What is going on?

I choose a base of 40 MHz clock

for 25 MHz, the multiplier is 5 and the divisor is 8

When I right click on the clock of new derivatives, I get only the possibility to enter a new frequency of the clock.

Why doesn't the tool let me simply specify the multiplier and divisor?

I'm using Labview version 2010

That should work just fine. The structure of the case will add some overhead to the total runtime of the circuit, but at 50 MHz, these costs should be minimal and you should not encounter many problems of timing.

Tags: NI Software

Similar Questions

-

I'm having a problem with sending the Midi out of Logic Pro X clock. It seems that every time I have connect my computer to my audio interface and open a new project (or old), I have to go into preferences and project settings for the Midi sync and restore 'Destination' under ' passed to ' to do things correctly implemented. Is there a way to set a default value? Thank you.

Yes... Create a new project... Configure everything as you wish... and then save it as a template via the file menu

Now, you can use this template with everything you want, set up the way you like it... When you start a new project...

-

Delay FPGA using a derived clock

Hello

Probably a simple answer to this. I have the PXI-7813R that has a clock of 40 MHz I database I need to create a delay time of 488nSecs in my code. Unfortunately with 40 MHz, I choose 475nSecs or 500nSecs. If I use a clock derived from 80 MHz I get a 487.5 delay which is very close to what I need. However, if I change my level above 80 MHz clock I get various offences of timing during compilation. Is there a way to keep the clock of 40 MHz top-level, but use the clock of 80 MHz for a time delay?

Thank you

Andy

Hi Andrew_Quick

Do you use this clock derived on a SCTL? I did some research on your question and find Knowledge Base article next talks a little about the way in which the clocks derivatives works with the SCTLs and in section shifts, there is a note that some codes can compile not at higher rates at 40 Mhz due to the time constraints of the FPGA , so I think that you should check that you don't have warnings or suggestions for when creating your clock derived to your target.

Even if you select the clock 40 MHz as the top level, if you select the clock of 80 MHz for the timed loop, the compiler will have to adapt all functions in the FPGA, and according to the error that you get that may be causing the violation of timing.

Hope you find it useful!

-

Hello

I'm working on a project using the star LM3S8962 evaluation kit and a 4-channel analog digital converter 24-bit Texas Instruments ADS1274EVM.

I want to get the data sent by the ADC with the LM3S8962 using the SPI bus.

I have all of the example provided by the following link for my case: http://decibel.ni.com/content/docs/DOC-7701

The ADS1274EVM provides 2 pins for SPI communication: DOUT1 and SCLK.

When it becomes a clock on the SCLK pin, it starts to send data via DOUT1 pin, there is no pin slave select.

If I'm right, I don't have to connect:

-PIN SSICLK for the LM3S8962 with SCLK of the ADS1274EVM pin

-PIN SSIRX for the LM3S8962 with the pin of the ADS1274EVM DOUT1.

The ADS1274EVM is powered independently of the LM3S8962, so I connect VA WINE GND as shown on the http://decibel.ni.com/content/docs/DOC-7701page.

I write because it does not work: the ADS1274EVM sends no data given that I cannot get a clock signal of the SSICLK of the LM3S8962 pin that allows the ADS1274EVM start the conversion

I think that him 'ARM of SPI create Configuration reference VI' configures a clock that is sent through the LM3S8962 SSICLK pin, but it does not work as expected.

Can someone help me please? Thank you

Luke Y.

Hi Luke,.

I just tested the example and had no problem generating a clock on SSICLK.

I join the project I did with LV 2009 SP1. I hope that you could test and tell us if it works.

Kind regards

-

Pavilion dv6 2170 clock problem after replacing the CMOS battery

Hello world. Sorry for my bad likely English

OK, so the problem started since I changed my laptop CMOS battery. and to be honest it wasn't whit any problem the clock when I replaced it but I if this may be the cause of another problem that later I figuered what the problem was because of the RAM.

in any case, I changed the Rams and this problem has been resolved. I just set the clock of the BIOS and rebooted the system. After awhile I figuered that windows clock is not fair. I restarted again and saw the BIOS clock. It has been reset for 2009! even when the laptop battery and power supply are attached the BIOS and windows continues to change clock! I even changed my windows and I replaced the CMOS battery with the former, but nothing helped. It seems really strange, but I don't think it's maybe a hardware problem there a driver or something for the CMOS battery... need your help! Thank you!

You mentioned that the BIOS has been reset for 2009? This means that there is a problem with the current or any leak and the BIOS has been "reset" back at the root of the plant. I'm afraid you have shorted something when you changed the battery not be grounded.

Worst case is that there is physical damage to your motherboard and there is nothing you can do about it, probably broken a capacitor - who cannot hold a charge to prevent the reset of the BIOS clock.

However, you can try this.

Completely, unplug your computer, remove the laptop battery, etc... Then browse 'Guide' your computer for the "hard physical reset" for your CMOS. I don't know what it's like on a laptop, I only did it on desktop with riders. Be sure to follow the directions precisely.

-Make sure you are properly grounded. touch the metal parts that is grouned before touching anything on your computer.

-the hard reset should be done for at least 30 seconds, this ensures that the power is completely served the system. Then you can set this back.Try this a couple of times, first without removing the CMOS battery and 2nd time after remove CMOS battery and placing it in.

Good luck.

BTW, you can also try running without your new memories (if there is more than 1 stick, try them separately). In fact, I would probably try first before doing a hard reset CMOS. The reason why I didn't say earlier, it's because I have assumed that you already tried this.

-

If there is a problem with the alarm clock since 4.4.4 updated and it's still in 5.0.2. When I try to clangw, sound alarm clocks it opens Commander file stock not his! 4.4.4 usually after phone restart everything has worked for awhile, but now in 5.0.2 is not fixing problem. Any ideas how can I get in stock clocks sounds? Or mount it at all?

You could erase the default values for applications in the settings-applications-all.

-

BlackBerry Smartphones Spinning clock problem

Here, I had a problem relates to a spinning clock that always appears when I lock the keyboard.

When I bought the first of all, it was not.

I thought that may be due to some applications that I installed, but I have not installed these heavy applications. My 9700 memory is always around 88 mb. and I uninstalled for some of them.

I just did a battery pull, but still it does not get rid of the spinning clock

Your memory active cleaning? Turn it off, you do not need.

Options > Security > advanced > garbage collection

-

After 1.4 update clock problem

Hello

I am a user of Palm Pre Telcel (Mexico) and I have problems with the clock on my device since the 1.4 update.

It is always 1 or 2 minutes before every day.

Someone knows how to fix this?

I have network disabled time...

Thank you!

I replied to your other post for this problem, we try not to cross-post here, thanks.

TreoAide

-

Hi all. I use the latest version of Skype and is now, for some reason, running three hours behind my computer clock. [Ex; my computer say 11:00 and Skype will say that the message is sent at 08:00.]

I get messages the same way. My friend will answer to something I said, and it will appear under mine, but also say that he has been sent three hours before. Essentially, Skype works fine it's just wildly incorrect time display. I followed a suggestion here and checked that Skype has been set on time - my computer is it. So I'm not entirely sure what's going on.

Does anyone have a solution?

ZephyrNocte wrote:

That's what is said about the time: line TZ;

* Time: TZ: UTC - 7, Server: 1461004250, Local: 1461015051

This translates to:

Server time: Monday, April 18, 2016 18:30:50 GMT

Local time: Monday, April 18, 2016 21:30:51 GMT

This means that the time on your computer is set to a wrong time zone.

You must set the correct time zone on your computer.

http://www.SevenForums.com/tutorials/944-time-zone-change.html

-

Instead of 'AM' or 'PM', my clock has my name! It has apparently been so for a while, but I never noticed until I tried to set a time within an application and found that I can't indicate whether the time is AM or PM - it is still my name!

Hey Ed :),.

Have you tried going to

Control Panel,

region and language,

by clicking on 'additional settings' in the first tab

and go to the tab "time"?You can change the AM and PM tags it. It looks like someone tried trapping you and changed the registry or the application of time management so that your name will appear. I don't see why windows would by default.

-Alex

-

HP pavillion a6720y clock problem

The time on my HP Pavilion a6720y desktop PC display is seriously wasting time.

I think I need to replace the internal battery, but I'm not sure if us a solution. Also, not sure where to find the battery once I find.

Standard button battery is a CR2032.

-

Clocks on board and derivatives of FPGA

Hello

I use a PCIe FPGA 7852R card to collect data at 200 kHz of channel 5. I was pretty confident that my collection frequency was correct, because my program was based on a derived clock of 40 MHz I had chosen to use a derived clock because the on-board clock is running at 40,02 MHz (instead of the 40 MHz specified for some unknown reason I ignored).

However, today one of the members of the LabVIEW support team told me that the FPGA clock rate may change during the compilation and optimization (constraints). He stressed that if the FPGA can run that fast, then it displays an error (as you might expect). He said also that in some cases, the on-board clock can run faster, but in this case no error will be displayed. I saw no errors in the past (which means that the system had no problem with that fast running), however, I'm not sure if during one of my compilations my derived clock could have run faster than 40 MHz. If it can happen? This will affect the time of all of my previously acquired data. Unfortunately, I have not saved any of my journal compilation of

.

.Thank you very much in advance.

Kind regards

Varun

Hi VarunSreenivasan,

I think that our support has meant that compile logs will show you some pieces of logic could operate at higher speeds. During the process of compilation, the compiler will determine the clock frequency more rapid that can be used for your logic and to ensure that the configured clock frequency is less than or equal to this value. If you have decided to try to run your code to 200 MHz and logic cannot run this fast, then you get an error. If you have decided to run your logic to 200 kHz and it is possible to run faster compilation logs will show you then the max frequency that will work, but the logic still run to 200 kHz. The code should run no faster than the frequency you specified.

-

Understand how to set up and use a sample FlexRIO clock

Hello

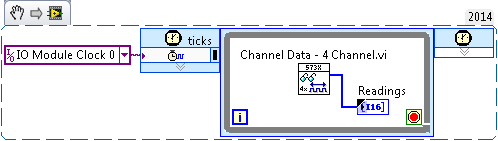

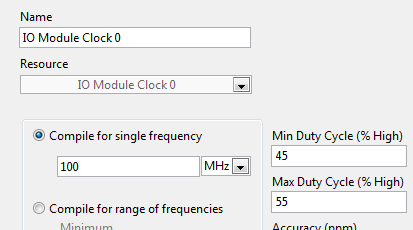

Following this discussion on inputs glitching, I learned that I need to use the area of the sampling clock to read nodes to HAVE it in my 5734 OR. So I right click 'FPGA Target'-> "New FPGA Base Clock" and selected "IO Module clock 0". In general, I followed the instructions at http://www.ni.com/pdf/manuals/375653a.pdf

Issues related to the:

- I noticed that, regardless of the value I put in "Compile single frequency", timed loops using this clock works at 120 MHz. Should it?

- I want to gain at 10 MHz, no 120 MHz. is there a way to create a clock derived from the sample clock? (Right click on the clock gives me not the option "New FPGA derived Clock")

- In the example of the FIDL, engine of CQI on 5734 SMU - 7962R.lvproj, 'IO Module 0 clock' is configured to be compiled to "100 MHz" instead of 120 MHz. is there a meaning behind this value? (# 1, I understand that the value is ignored)

- The code example below, I get "error-61046 occurred to read/write control" unless I have excluded the "Reset" of the VI host node. This problem does not occur if I use on-board 40 MHz clock instead of the clock of Module e/s 0, (although I'd get glitched data). Am I wrong configured something?

- In my current, more complex program, I get the same error even with disabled node, if I stop and restart the host VI - but the next attempt would succeed.

- I have attached the sample file project, the screw and bitfile, where they are useful.

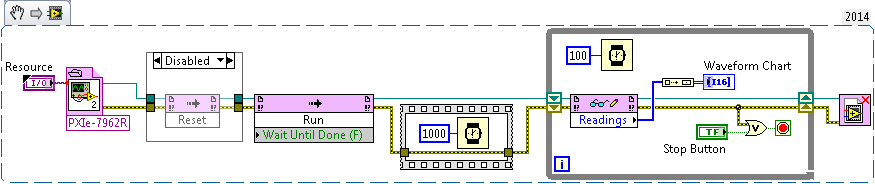

Hi FKSH,

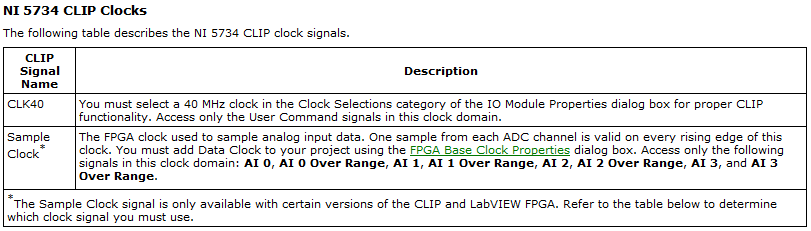

You are right that you must Access your e/s on the 5734 NOR in the area of sample clock:

(this information is by using LabVIEW for the CLIP of 5734 OR)

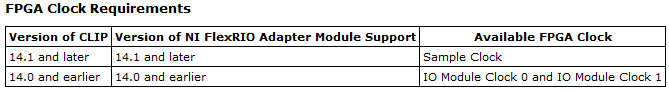

It is a clock Module e/s 0 or sample clock based on your version of the FlexRIO driver you have installed. Based on your statements, looks that you use LabVIEW 2014, so be sure to have FlexRIO 14.0 or FlexRIO installed 14.1. If you have FlexRIO 14.0 or earlier, the sample clock will be IO Module clock 0. If you have FlexRIO 14.1 or later, it will be the sample clock:

(also of the documentation NOR 5734 CLIP in help)

The only support for sampling rate is 120 MHz, unless you use an external clock CLK in and it must be between 50 and 120 MHz (see page 9 of the Manual). If you wish to purchase to 10 MHz, the best thing to do would be to sample the e/s to 120 MHz and then decimate the data by a factor of 12 (keep all 12 data points only and throw out the rest).

Regarding the FIDL, I'm guessing that you're referring to the configuration in the properties of the clock:

This configuration is not actually change the frequency of the clock. The compiler uses this value so that the logic can operate at the specified frequency, but the real clock is provided elsewhere (in this case, the FAM).

Finally, I saw error-61046 occurs more often because of the configuration of the internal clock. Make sure you use the clock on the right as the only cycle timed loop source as I mentioned above. In general, I do not recommend write directly on a 120 MHz indicator, as there are a lot of other logic that needs to be done in order to update the indicator. The data are sent to a domain different clock under the hood, so you can actually update the data and I suspect that there are some conflicts with the clocks. You also lose data as the host won't be able to read all the data before it gets crushed. Instead, I would use DMA FIFOs if you need all the data you acquire or to send the data to a different loop which will be responsible for the update of the indicator in a slower clock domain.

In general, I recommend always that the start-up of the examples in the Finder as a good place to check if the equipment works properly and as a reference for the correct configuration. Once you compile the code, you should be able to run it natively to acquire some data. "" "These examples will be under input and output hardware" FlexRIO "Modules e/s ' NI 573 X ' NI 5734.

Best regards

-

Hello

I'm looking for more details on the clock embedded to cRIOs stability (mainly 9076). Data sheet does not say much to that. So, what type of oscillator is used for the generation of on-board clock (40 MHz), how accurate is? Without this information I don't see for example, the accuracy of timing signal generated can be determined.

Thank you

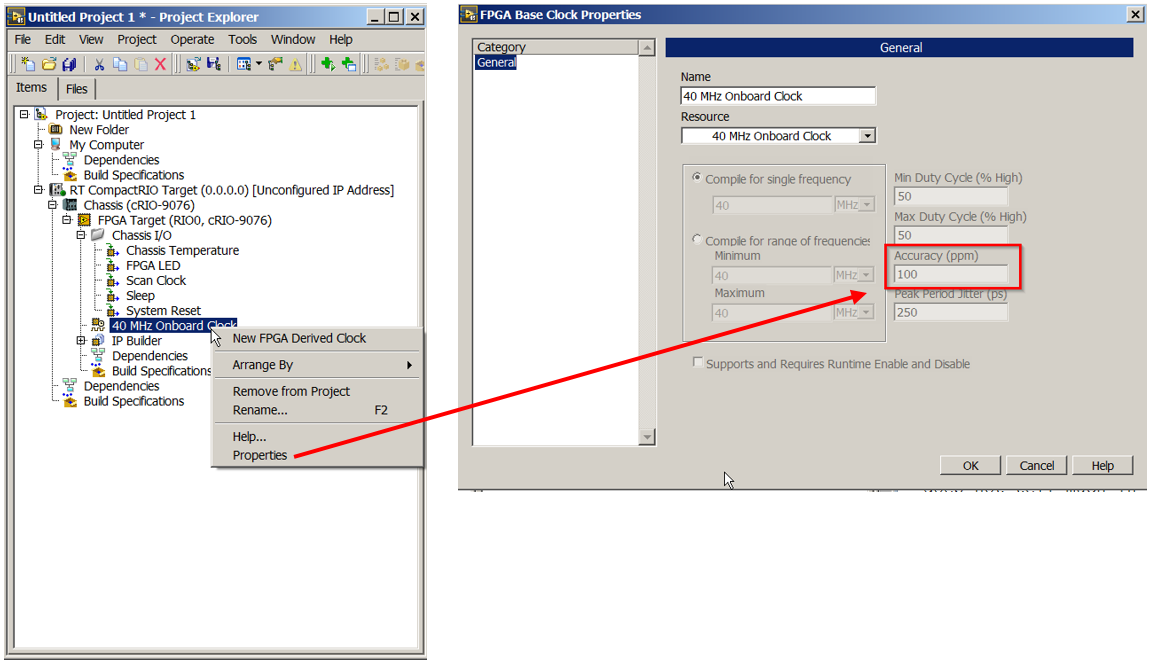

Dear Saimot,

for each clock target (40 MHz on board and some derivatives clocks - if the target allows and you created them) you can find the accuracy of the information in the Project Explorer by right clicking on the desired clock and selecting Properties. See attached picture. What is the answer to your question?

B/R

-

Areas of clock in the FPGA examples

I was looking through some examples of LabVIEW FPGA and I fell on the example of Crossing Clock domains.

In this example, there are 4 screws; FIFOs.vi; Global Variables.vi; Local variables.VI; and Registers.vi. In each of these screws, there is a timed loop which runs at 160 MHz.

How is that possible? Since the clock on the FPGA is only 40 MHz. did I miss something?

On the FPGA target, you can right click on the clock of 40 MHz and create a derived clock which can be a multiple where for a fraction of the base clock (40 MHz).

160 MHz is a trivial example of 4 times the base clock.

Maybe you are looking for

-

I tried to do a system restore on my laptop using the included recovery disks and had this error 0x400110020000100B. The drive looked pretty beaten last week so I ordered a new series. Now, when I got to put disc 2 in (to 80% full) I get the same err

-

8-bit word per pulse output USB-6009

I need to generate a 8-bit word and a strobe pulse in Matlab via a usb-6009. How do I do that? Any help is appreciated!

-

Someone been able to pair a headset bluetooth with the Xoom? I have the WiFi Xoom and Motorola S10 - HD bluetooth headset. I can get the headset to pair with my Droid phone, but my Xoom cannot see them. Does anyone have any suggestions? I know the wo

-

Passport, Playbook, BlackBerry and Blackberry Bridge

I've been to access emails etc. of my Playbook via Blackberry Bridge connection to my flashlight. Have now upgraded to a passport; Blackberry Bridge seems to connect at both ends, but at the end of passport he goes immediately to the lost connection

-

All-in-one HP 5610 shows offline

Mac OS x 6.8 is connected to the hp officejet 5610 but it also shows offline. HP software currently installed and put to date Checked cables and work. Help, please