Error of FPGA-RT 25

Hello!

I get the error message 'Error 25' when I try to read data to the RT in the FPGA. It has worked before, but then decided to stop working. Weird to notice is that I seem to be able to establish a contact with the FPGA, since the "target open FPGA" - block and 'execute FPGA"- block of work without error code. The path configured in the FPGA 'open' is correct. I submit the EIS.

Any ideas are greatly appreciated!

Concerning

Rickard

Nevermind, I got a later version of labview installed on the computer, and now it works all of a sudden!

Is there any list OR all the labview error codes?

Tags: NI Hardware

Similar Questions

-

Hello

When compiling a fairly basic FPGA VI, I get the following error:

61332 error occurred in niFpgaCompileWorker_ProcessStatusPipe.vi:1<><>

Possible reasons:

LabVIEW FPGA: An unexpected error occurred with the build tools. You try to compile the FPGA VI again could solve the problem.

The length of a line in "NiFpgaAG_0000002e_WhileLoop.vhd" is too long for xilinx 10.1. Length: 32845 Max length: 4150

Departure time: 17:22:06

End time: 17:22:12

Total time: 00:00:06Apparently, the vhdl code generator OR forgot to add some CR + LF in the intermediate files. How to work around this bug?

Kind regards

Lukas

Hi Lukas.

When LabVIEW compiles a VI, the VI is converted into virtual hard disk to be compiled into a file bit by Xilinx. As you have already understood, this error indicates that a line of code vhd had a length of 32 845 characters, which exceeds the maximum length of 4150 characters for the Xilinx 10.1.

Although 32 845 characters is very long, it is possible that this is due to the codification of LabVIEW rather than a bug. Some common causes of this problem include large enums, a matrix, or clusters in the code. Please check in your code. If you have no luck, please attach a screenshot of the code. I hope this helps!

Kind regards

Dayna P.

Technical sales engineer

National Instruments

-

Hello. My name is Jason. I'm working on what should be a very simple project to form a collaborator on the material OR that we work.

I used this equipment in the past to remotely control a ranger xp. I tried to use the exact configuration of the code... I'm not sure what I did wrong.

Screenshots of the Project Explorer, and the screw runs on the PC, the cRIO FPGA have all set up and.

The goal

I want to be able to Flash an LED using the crio and control the speed of the flashing of a VI running on my PC. The VI running on the PC has a slide to control the speed of blinking and a Boolean switch to activate and deactivate. The VI on the cRIO multiply the speed by two and shows the State of the Boolean switch. These values are passed to the FPGA VI which is supposed to turn off the led market and stop.

The problem

The PC code and cRIO seem to do exactly what I want to do. Digital i/o does not value. There is no error coming out blocks of reference or FPGA read/write.

I didn't know where to post this because I can't see the error is coming from. The only error I have found is when I right click on the program, I wrote and respected to run on the fpga and try to download it. This error - 50001 and causes "an attribute whether explicit or implied is not relevant or is not relevant given the current state of the system. The operation could not be performed as indicated. »

The system hardware

I have a PC running Labview 8.2 (ip or subnet address 192.168.0.70 255.255.255.0) it is connected with a cable crossed to a cRIO 9004 (address ip 192.168.0.2 255.255.255.0 sn) and a cRIO-9104 chassis. The cRIO has a digital I/o module (NI 9401).

Software

LabView 8.20

Module FPGA 8.2.0

Module time real 8.20

any help/advice/tips would be greatly appreciated.

Thank you

JAson

Hi jcoates,

Please take a look at this knowledge base article: Why do I get error 50003 when you run an FPGA VI on my real-time controller?

If this does not resolve the problem, you are able to get a simple FPGA VI, which does not interact with the LED work?

-

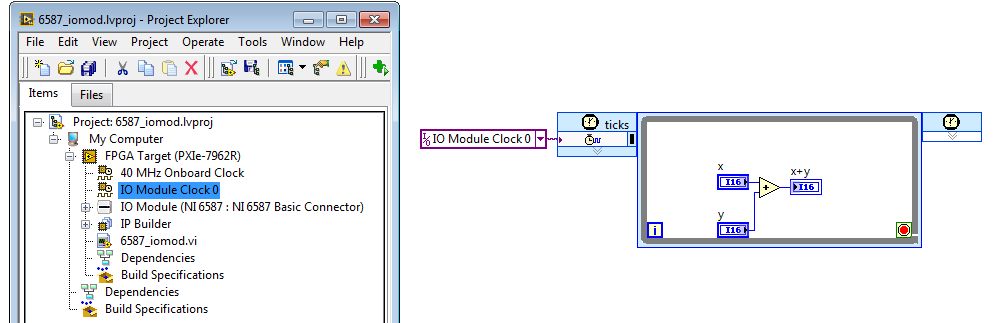

Clock or 6587 external in (simple nerve - ADM)

Hello

I have a PXI fpga 7962R module and or 6587 adapter. I want to use the external clock to set up a simple Adder xilinx Ip core. I have the e/s 0 clock input an external clock of 20 MHz with 3 V pk to pk. I then attached to single loop timed cycle and fpga clock allow VI and set up my IP core inside the loop. I haven't used the fpga disable vi since I want continuous running vi.

now the project, but on the spot and I don't see any other except top 40 MHz clock being implemented. At the end of the compilation, I received an error which fpga and host could not communicate. the clock z not connected or is nott generated according to specifications. What could be the problem?The project you attached had not included in FPGA vi so I am unable to tell if you were using the IOModClipClock0 correctly.

Anyway, attached is a draft that has the IOModClipClock0 added to the target, and an FPGA VI, who uses it to run in a single clock cycle logic loop.

-

Hi all

Please, for the love of God can someone take a look at the attached FPGA project, I hit to the top and tell my why it is that whenever I run, as soon as he's trying to read/write on the host computer, it returns error-61046? A screenshot of the error is included in the attached .zip file.

I made many programs FPGA before with no problems, while using the same FPGA and FlexRIO module and never had this problem. If I run an example program it works fine so I am confident, that the error lies in my programming, I can just see where!

As you can see all the clocks are internal and appear to be configured correctly according to the example programs and other programs FPGA, that I have done before, so I'm puzzled. I hope that it is just my stupidity and lack of coffee.

Congratulations in advance.

Mitch

The pilot FlexRIO comes two CLIPs for the 5781. At ' a "NI 5781 Sychronous system" OR 5781 "VIDEO CLIP.

The "NEITHER 5781' is what originally delivered with the FAM and is always delivered with the driver for legacy purposes. I would discourage the use of this CLIP because it uses regional clocks for IO Module clock 0/1 which limit the amount of fabric that can be driven by these clocks to the fabric available in the respective region of the FPGA. The advantage of this CLIP, it's that the ADC and DAC can be clocked at different rates through a clock divider that exposes the CLIP.

The 'NI 5781 Sychronous system"CLIP is what is recommended for all new models. It uses a world clock which can target tissue in all regions of the FPGA. This CLIP uses the same clock to drive the ADC and DAC (IO Module clock 0). IO Module clock 1 is not used in this CLIP.

If you used the sychronous CLIP system and always a logic had driven out by IO Module clock 1 it that would explain why you received the error of non-response from IO Module clock 1 is left connected in the sychornous CLIP system.

-

Error-63101 when executing the FPGA Interface C API Generator in LabVIEW 2012

I'm using LabWindows CVI 2012 and 2012 LabVIEW FPGA module. I try to use the FPGA Interface C API generator and I get the following error from a freshly generated .lvbitx bitfile. I use the local server compiles on my PC.

Error-63101

NOR-RIO: A valid .lvbitx bitfile is required. If you are using a valid .lvbitx bitfile, the bitfile maybe isn't compatible with the software you use. Determine which version of LabVIEW was used to make the bitfile, upgrade your software to this version or later, and then try again.

The problem occurs when executing CVI or LabVIEW. I was able to do this earlier when I was compiling the FPGA in LabVIEW with the API generator 2011 downloaded from the Web site.

A bit of weirdness in my setup, it's that I charged it off downloads from the website (latest files after 2012 NIWeek) rather than the normal distribution DVD. I installed LabVIEW, so NI RIO, then the Xilinx tools compatible with 2012. It works very well when you talk to the FPGA to a LabVIEW vi running on my Windows PC to the host.

Any suggestions?

Problem solved. I had to download FPGA Interface C API generator 12.0. It works now.

I would have thought that if a product was called on the menu in LabVIEW 2012, it would be prompted to upgrade to a compatible version, when I installed LabVIEW. The old version is not compatible with version 3.0 bitfiles, as identified on the following lines at the top of the .lvbitx file:

3.0 -

Broken the FPGA VI but the empty error list

Hello!

I'm trying to run a vi which includes a 'Open FPGA VI Référence' function. However, an error and it says that "not compiled FPGA VI. When I try to compile the FPGA VI a message saying "The VI is broken". I try to run the FPGA and when appears in the error list, there is no error or warning in the list, although the name on the fpga includes the Red 'X' ('show warnings' is checked). Any help?

I'm using Labview 2013.

Pablo

Hi Pablo.

Sorry for my delay in responding, you managed to get the respected FPGA.vi yet?

To answer your questions, if the project is ok with an empty FPGA.vi, then in theory, your hardware is configured ok. However, due to the vi being blank, you haven't tried to use one of the modules on your system, so it can introduce errors. The most common mistake is differentiation of mode Scan Mode/FPGA by installing the project in the first place. Also be aware that not all FPGA targets supports everything, for example some dislike for the rows that have an index to calculate the number of iterations, rather than a constant wired at the entrance to "n".

Out of curiosity, why you place every measure in the DMA separately and also specify address? Is there a reason you don't just place all the measures in a table and put everything in the DMA, then divide the table on the other side?

Generally speaking I don't think that incorrect programming should never cause LabVIEW crashing and you should always report the problem to the OR in order to take a look and see if they can fix it.

Hope that you managed to get your problem sorted and again sorry for the late reply.

Darren.

-

error 1136 When adding FPGA in SysDef

I have a PXI-7854R multifunction RIO installed in my SMU-1075 chassis. When I add it to the system under the FPGA node definition file, the RIO node is created with all its subnodes - as expected - but the attached dialog pop error. Whenever I highlight the node newly created Rio the same error appears. Everyone knows this?

I have an SMU - 6341 Multifunction DAQ designated as master hardware device Synch on the Bus 2 and moved to PXI_Trig0 through all three bus.

Also, I use Veristand 2011 SP1.

Thank you

Yes we have seen. Fortunately, it's just aesthetic. This happens when you have a DAQ master that is hidden in the tree and click devices FPGA. We hope to solve this problem in 2012. Sorry for the inconvenience

-

Why get error during execution the FPGA VI?

Hello world

I have a lot of sense of wrong during execution of a program that has been correctly executed previously. I don't know what I did wrong.

Now, whenever I run this FPGA VI, I get an error (in the attachment). And, then runs the FPGA VI, but it does not give the data required those he supposed to give as output.

Any help or recommendations would be appreciated also.

Thank you.

Hi auree123,

There are a few reasons for this error

may occur. Could you tell us more about what's going on?You are

I get this error when you compile and if so, at what stage?It looks like

as you may be running it in Interactive Mode, which means that you are viewing

the front of the FPGA VI on the development computer that you are running - is

that correct? If so, you could try to create a VI on your host

Open a FPGA reference and communicate with the FPGA programmatically rather than interactively.Thank you

Morgan S

Technical sales engineer

-

Internal software error of LabVIEW FPGA Module - 61499

I get the error next (in a pop-up window) in the phase of sompilation for the FPGA target with a vhdl IP. This error continues to occur even after restart LabVIEW and the PC. Someone at - it solved is this kind of problem before without having to re - install the software?

Here is the error information:

Error-61499 occurred at niFpgaXml_GetValue_String.vi<><><><>

Possible reasons:

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has occurred. Please contact National Instruments technical support on ni.com/support.

Additional information: lack the tag required XML (/ CompileServerList)

As a first step, I can compile the vhdl IP node successfully. However, once when I'm running a VI with the FPGA, the bureau stop working. After that I restarted by force, it cannot perform the build of a vhdl IP node. Even without connecing to the jury of LabView, he pointed out errors before the end of the sompilation.

Interestingly, the screw which also includes nodes IP vhdl that I properly compiled before, I can still run the VI to the Commission and it works correctly.

Thank you

Looks like your ActiveJobsList somehow has been corrupted. I saw occur when computers are hard stop or blue screen during compilation. I don't have that LabVIEW 2014 installed on my machine, so your path will be a little different, and the file extension will be a .txt or .xml instead of .json, but try this:

Move the file "C:\Program Files (x 86) \National Instruments\LabVIEW 2014\vi.lib\rvi\CDR\niFpgaActiveJobList.json" (or your equivalent) out of the above directory (back it upward and delete essentially) and restart LabVIEW. Must regenerate the file and resolve the problem.

-

When I try to create an executable from a host VI that has an "Open FPGA VI" reference who has run, the value "Dev computer w / Sim i/o" value, the application is built without error but when I try to run it, it opens with an arrow broken to run and has the following error:

"VI has an error of type 2302200. The full development of LabVIEW version is necessary to correct mistakes. "In fact, he repeats this message two times in the same window for some reason any.

Moreover, I * have the LabVIEW full development version and I use 2010 SP1

While the error message is not as clear as it could be, you're right: you cannot run an executable file that tries to run an FPGA VI in the simulation. It would be nice if there was an error in compiling. I always forget to switch to run on the target FPGA before building my application and discover the error until I have it copied on the system in the laboratory.

-

Compilation of FPGA - real formal error on the cost of the port cannot be an expression

Details:

ERROR: HDLCompiler:192 - "C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd" line 1408: real formal on the cost of the port cannot be an expression

ERROR: HDLCompiler:854 - "C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd" line 69:Unit ignored due to previous errors.

File VHDL C:\NIFPGA\jobs\BPO5kq2_O6tyN2U\OC4_Sine_Cosine_LUT_Constant_Amplitude_dash_optimised_vi_c.vhd ignored errors

-->The compilation happens to step "using the unit felt" but then stops soon after with a compilation error.

The line in question (1408) refers to the output of a "Reinterpretation FXP" node with the text

Cost => (others-online '0'),

in the part of port of the code card. This is the output of the FXP reinterpret node is directly connected to an indicator in a VI sub whose output is then entered directly at a crossing high multiply node. The code is part of a cosine sine LUT I programmed. She used to compile without a problem, but I think I know where is the problem. In one case, I have used only the sine of output of the algorithm and theory, Xilinx can optimize away from the part of cosine. I have two instances of this VI in my code and looking at those generating any errors, the output is associated with a cosine indicator.

Cost-online s_Cosine_2434,

It seems that the track is essentially optimized away, but the compiler, Xilinx has a problem with the flag being present on the sub - VI but the idnicator is not used anywhere. As a result, the cost gets set to an invalid value. I guess close to reinterpret it FXP at the exit of the Subvi is an important aspect of this problem.

I think I know enough now to fix this (remove the path manually by duplicating the sub - vi), but it may be useful for future bug fixes feedback in the FPGA module. It is not the first time that this kind of removal of incorrect code me has given problems, but this is the first time I could clearly identify the problem.

Shane

Hey Shane,

Looks like someone filed a bug report on it a month or two ago. It's the CAR # 475397 if you want to check for it in the list bug fixed for 2014 SP1.

-

ERROR: TclTasksC:process_077: in the FPGA Compilation

Hi all

I use for my application in which I am facing following error when compiling my fpga code compact rio 9072:

Compilation failed due to an error of Xilinx.

Details:

ERROR: TclTasksC rocess_077: did not finish. Please, look in the newspaper and report files.false

rocess_077: did not finish. Please, look in the newspaper and report files.false

When running

"process run"card.

(file "C:\NIFPGA\jobs\XI64xG6_My449tj\map.tcl" line 6)ERROR

ack:2310 - type compositions "SLICEL" too found to adapt to this device.

ack:2310 - type compositions "SLICEL" too found to adapt to this device.

ERROR ack:18 - the design is too large for the device and package.

ack:18 - the design is too large for the device and package.

Please see the Design summary section to see the cost estimates for

your design exceeds the resources available in the device.

NOTE: A file NCD will be always generated to allow you to examine the mapped

Design. This file is intended for assessment use only and will not be processed

successfully through NOMINAL.

This NCD mapped file can be used to assess how the logic of the design has been

mapped in FPGA logic resources. It can also be used to analyze

preliminary to the level logic (route pre) calendar with one of the static electricity of Xilinx

analysis of synchronization (PRHT or Timing Analyzer) tools.

Summary of the design:

Error number: 2

Number of warnings: 69

Use of logic:

Number of slice Flip Flops: 7 886 on 15 360 51%

Number of 4-input lut: 16 104 on 15 360 104% (OVERMAPPED)

Distribution of logic:

Number of slots occupied: 8 744 7 680 113% (OVERMAPPED)

Number of slices only related logical container: 8 744 100% 8 744

Number of slices that contains no logical relationship: 0 to 8 744 0%

* See NOTES below for an explanation of the effects of unrelated logic.

Total number of 4 input lut: 17 400 on 15 360 113% (OVERMAPPED)

Number used as logic: 15 998

Number used as a middle way: 1 296

Number used as Rams 16 x 1: 82

Used number recorded the shift: 24

The logical Distribution report slice is not significant if the design is

too mapped to a resource not slices or if Placement fails.

Number of IOBs servile: 183 on 333 54%

BIO flip flops: 74

Number of RAMB16s: 1 24 4%

Number of MULT18X18s: 2 on 24 8%

Number of BUFGMUXs: 4 to 8 50%

Number of DCMs: 1 on 4 25%

Fanout of the Non-horloge nets on average: 3.38

Peak Memory use: 361 MB

Total in time REAL in the completion of the card: 1 dry 12 mins

Time CPU until the end of the total map: 1 dry 12 mins

NOTES:

Related logic is defined as logical that share connectivity - for example two

Lut are "related" if they share common inputs. During Assembly of the slices.

Card gives priority to combine the logic that is related. Generates so

best performance of synchronization.

Without logical report does share no connectivity. Card will start only packing

logic not related in a slice once that 99% of the slices are held through

logical packaging partners.

Note that once the logical distribution reaches the level of 99% by related

logical packaging, this does not mean the device is completely used.

No logical report package will begin, continuing until all usable LUTs

and FFs are busy. According to your timing budget, an increase in the concentrations of

logical packaging unrelated can adversely affect the performance of timing set

your design.

Mapping performed.

See the report of map file "toplevel_gen_map.mrp" for more details.

Problem encountered during the packaging phase.

Failure of the process 'Map '.Start time: 18:29:23

End time: 18:44:42

Total time: 00:15:19Can someone tell me why this error came?

Thank you best regards &,.

Vipin Ahuja

Vipin Hello,

It seems that your code requires more resources that are available on the FPGA. Optimizing your code can help to solve your problem:

You may have noticed some "Overmapping", mentioned in the newspaper:

Number of 4-input lut: 16 104 on 15 360 104% (OVERMAPPED)

Distribution of logic:

Number of slots occupied: 8 744 7 680 113% (OVERMAPPED)Take a look at this article:

http://digital.NI.com/public.nsf/allkb/060BA89FE3A0119E48256E850048FFFE?OpenDocument

And this:

http://digital.NI.com/public.nsf/WebSearch/311C18E2D635FA338625714700664816?OpenDocument

Kind regards

Navjodh

National Instruments

-

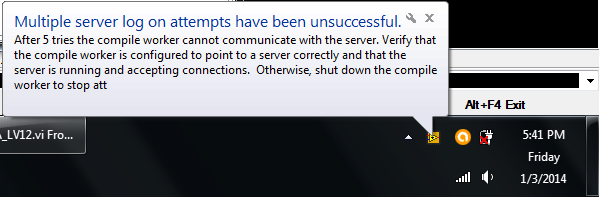

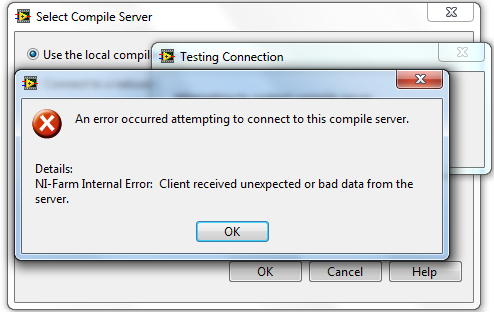

Internal error OR-farm - impossible to compile the FPGA VI

Hello!

When I try to compile any FPGA VI with LabVIEW2013 or 2012 SP1, I get the following error:

"Year error occurred trying to connect to this server compilation."

Details:

Internal error OR the farm: Client Server received unexpected or bad data. »

Intermediate files are not generated, the error message appears immediately after I have select build of build specification or I click the run arrow.

I use the local server for compilation.

The equipment I use: CompactRIO Evaluation Board - SbRIO9636, DELL laptop, Intel core2 Duo T5800, 2 GHz, 3 GB RAM, Windows 7 Ultimate 64-bit, SP1.

The intermediate files CAN be generated without any problems if I select in the menu. If I run the FPGA application compile worker, a ToolTip message specifying that "FPGA compile runs", but after a few seconds, another message appears: newspaper several attempts were unsuccessful - please see attached images.

At first, I thought that my firewall (Comodo 6.3) is the reason for this, so I disabled it but nothing changed. Then I tried to fix LabVIEW FPGA and XILINX tools with the firewall disabled but din do not solve the problem. I tried with LabVIEW SP1 of 2012 and 2013.

If you have any suggestions, please let me know! Thank you!

We would like that you try to reset the NIAuth database by following these steps:

1. go to Windows Services (Bring up Windows with Ctrl + Alt + Delete Task Manager, click the Services tab, click the Services button at the bottom right of the window.

2 stop the NI Application Web Server and NI System Web Server services in this order (right click, stopping service and select).

2 backup, and then delete all the files under %PROGRAMDATA%\National Instruments\NIAuth: registry.bin and commitmark.

3. run NI System Web Server and NI Application Web Server services in this order.

4. navigate to http://localhost:3580 / connection of an IE on the local computer and try to log in with username "admin" and password empty. Succeeds, the server will return one signed in as: message from the admin.

After you follow these steps, try and connect to the FPGA compiler, and then let me know what are the results.

-

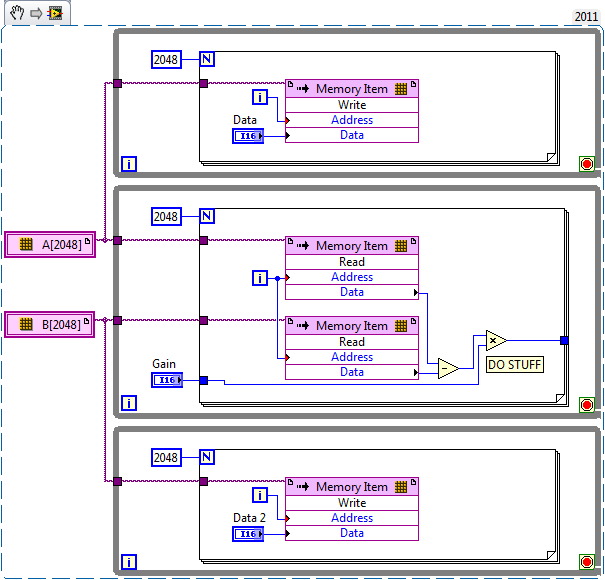

tables of fixed size in FPGA compilation error - how to implement a waveform control in an FPGA?

Hello

After being stuck for two days, please let me briefly describe my project and the problem:

I want to use the cRIO FPGA for iterative control of waveforms. I want to capture a full period of the waveform, subtracting a reference waveform period and apply control algorithms on this. Subsequently the new period of correction must be sent again for the output module OR. If it does not work, the captured waveform will look like the one reference after several iterations.

I am planing to create an array of size fixed for the capture and the reference waveform (each around 2,000 items for a given period). I use so 2 paintings of each elements of 2000. I use the function 'replace the subset of table' to update each element captured in the loop sampling and a feedback for each table node to keep in memory (I also tried shift registers, but then the berries do not have a fixed size any more and I can't start the compilation process).

If I try to compile the FPGA vi, I get the following error:

Details:

ERROR ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

"Synthesize - XST" process failedBefore I added berries to my code I could compile the FPGA without problems. So, it seems that the tables are too big for the FPGA. :-(

Therefore, I would like to ask if there is perhaps a better method to implement my problem in LabVIEW FPGA? How could avoid the tables to save my waveforms on a period?

Thanks a lot for your help in advance.

Best regards

Andreas

Unfortunately, the LabVIEW FPGA compiler cannot deduct stores shipped from berries (yet). When you create these two large paintings, you are creating essentially several registers very, very large. Just by looking at your picture, I guess that there are at least 4 copies of each of the tables.

You want to use LabVIEW FPGA memories instead. You can create memories outside the loop and then read/write them where you are currently referencing the berries. The only change that you really need to do is to break down your treatment in scalar operations. I have attached a simplified version of your plan, I hope it helps. Let us know if you have any other questions.

Maybe you are looking for

-

L70-B-126 Toshiba supervisor password problem

Hi, I have a problem. My son has set a supervisor password and forget it. How can I fix the problem and restart the BIOS do not the remove battery? Thanks for help.

-

How to configure my live (hotmail) account on my phone?

I'm a complete amateur when it comes to this kind of stuff. I have an account live [email protected] and am trying to set up on my phone so I can get emails coming through. But I do it every time it fails to connect. I use the settings it provides

-

[IdeaPad Y510] Compatible Wake On Lan?

Hello I'd like to wake up my laptop with Wake On Lan, but I did not find the settings "Enabled Wake On lan in the bios". How can he do? Thank you ------------------------------- I'm sorry, I'm French, I speak very well English

-

bad terminator in the Basler A504k CIM series

I'm talking about in series of LV to a Basler A504k via a NOR-1429th and, despite what says in the compatibility report and in this post, I perfectly managed, at least as long as I tried. A (still unpolished) example of my order that VI is attached (

-

Explorer.exe crashes because of the StackHash_1703

Original title: "problem Event Name: _APPCRASH__ Application Name:_explorer.exe__ Version: _6.0.6000.16771__ Application Timestamp:_4907deda__ Application Module Name error: _StackHash_1703 ' Problem event name: APPCRASH Application name: explorer.ex