executable cRIO-9072

Hello

I have a question.

SME at the time I did a version 2 of the program in real time cRIO-9072. First of all it is with PC remote control (has a problem as it crashes once a day) another a wasfor Web based remote control. I still have both versions on my project. Unfortunately the cRIO-9072 system was delivered long ago, so I did not have access with PC which have completely installed LabView.

The question is are there any way to install the executable on the cRIO-9072 so that it runs at startup without using LabView?

Hi Sergey,

Good afternoon and I hope that your well today.

Start of VI is on the ftp: / /

If you have the exe of RT which was built by the project, you can ftp (manually) or to the MAX of the target. For more information, please see the following article in the knowledge base, Startup configuration live on target time real LabVIEW http://digital.NI.com/public.nsf/allkb/CD3C7A3F58CBBAAA862570F8007D8D06?OpenDocument Please read the warning note too. Remember that it is recommended to use LabVIEW and select start VI - but I understand that this is not an option. Please let me know if the links help,

Tags: NI Hardware

Similar Questions

-

use of devices high cRIO 9068 FPGA

Hello. I have problems with my cRIO 9068 (dual-core, Artix 7 667 MHz), which uses a lot of FPGA resources. I did a little VI FPGA (LabVIEW 2013 SP1) allowing USER FPGA led to two colors (green and orange) for 500ms and then it is off for another 500ms. use of device Watch report 9193 records used(8.6%) and 9744 LUTs (18.3%). I adapted the VI even for a cRIO 9072 (Spartan 3 - 1 M) which have been allotted to me and use of the device is much lower: registers used: 443(2.9%) and read: 644(4.2%) - please see attachments!

I used the XNET library in the past with the 9068 and 9862 CAN Module: since I knew that these libraries use the FPGA space, I removed XNET 1.8 cRIO software before this test. Before removing, use of FPGAS was even higher!

Can someone tell me how can I reduce the resources used to 'normal '? Thank you!

Hi Lucien,.

The increase in the use of core resources that you see is normal for the family of targets Zync. Try to compile white VI for each (no user written code LabVIEW). You will notice that the Zync platform always uses an important part of the fabric (which targets Zync is used).

This behavior is due to the very different architecture of the family of chips Zync. As the FPGA and ARM processors are on a shared matrix, a large part of the logic and OR treatment implemented in ASICs Spartan/Virtex advice should be moved on the FPGA itself.

You should also notice that, although there is an increase in the use of FPGA base fabric, the gross number of LUTs/flip flops at your disposal as a user is much greater on Zync objectives than a Spartan comparable unit.

-

Crash when creating a new project FPGA cRIO

When I want to create a new project with the wizard FPGA cRIO, Labview freezes and blocks ("development system Labview 8.6 had ceased to function".) The wizard detects my cRIO-9073 integrated controller, but when he tries to discover the CompactRIO chassis, the program hangs and stops automatically.

In MAX, there is no problem discovering the FPGA chip in the cRIO-chassis (RIO0)...

I tried to use the new FPGA Project Wizard in Labview 8.5. While searching for the cRIO chassis, the program does not freeze, but he says the cRIO-chassis cannot be found...

When I want to manually select the chassis, I can only choose for the cRIO-9072 and cRIO-9074. There is no cRIO-9073-icon...?

What I am doing wrong, or is this a bug?

Kind regards

Kenneth

-

Many FPGA target as a controller cRIO

Hello!

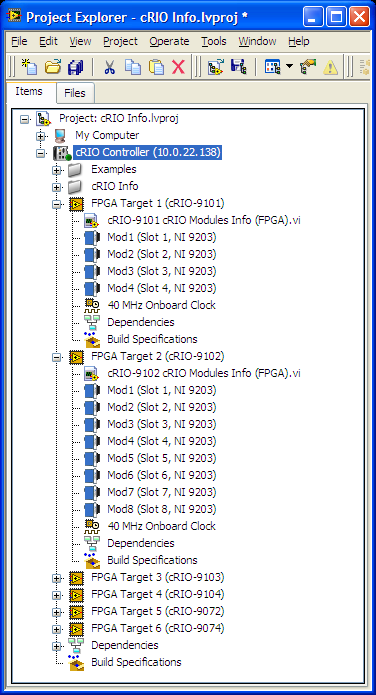

I was reading the cRIO System Configuration Information (CRY) Encarta article (http://www.ni.com/example/51852/en/) and here the Figure 9 shows a cRIO controller with multiple FPGA targets. How can this be accomplished?

In my case, when I tried to add a 2nd FPGA target, under my cRIO-9076, I get a message that can only be associated with the controller.

Any ideas?

Support of claims library CRY to LabVIEW 8.5.1, which leads me to believe this screenshot was taken in this version. The RIO Scan Interface/FPGA Scan Engine (IRS) have been introduced in LabVIEW 8.6 and NOR-RIO 3.0.x. To include this support, introduced the notion of a frame in the LV (notice there is no chassis under the Comptroller in the screenshot). To facilitate the RSI and the analytical engine and provides a more accurate representation of what is actually available in a system, you can only add a frame by controller. This allows the IHR charge the correct controllers for deployment.

BT 8.5.1, you can add multiple targets to an integrated system controller/FPGA (as the cRIO-9072) even if there is no way that could happen in real life, so it's not really desirable. You can always do is to add multiple FPGA targets (even chassis cRIO) in respect of the purpose of the workstation in your project. Still allowing you to communicate with the target FPGA, but no screws will run on your PC system, not the cRIO controller.

-

rror 8 has occurred to the file dialog-> Networked.vi URGENT

I have some project for cRIO-9072 control.

I used the network shares Variables to control cRIO PC remotely.

After I used it whenever I have to start VI I could see that the message

Error 8 has occurred to the dialog file-> Networked.vi

Possible reasons:

LabVIEW: File permission error. You do not have the correct permissions for the file.

=========================

NOR-488: Error detected DMA hardware.Method name: library

eploy libraries

eploy librariesDoes anyone know how to overcome this error.

The time is pretty critical to me. We will ship the material in the morning and I still couldn't create executable work to control cRIO PC remotely.

I have included the screenshot and project as well so you could see what is happening.

Hi all

The solution in my opinion for this error message was:

When you make an exe of a project using shared variables, you must have a local copy of the variables on the deployment computer which are then related to the 'real' shared variables stored on the target - cRIO, in this case.

This means that in the view of your project:

(1) Create static variable in the normal Manor on the cRIO.

(2) create variables shared on the host PC - llb under the Pc host in the project and then select the aliasing and how to link to YOUR PSP.

Kind regards

-

Several timers loop data acquisition

Hi all

I am developing a VI for FPGA Deployment. My equipment consists of a chassis/controller for cRIO-9072 with module 1-9211 thermocouple, card SD-1 module, 3-9215 HAVE modules and universal modules 2-9219. I will collect data of two thermocouples on the 9211, 14 channels on 9215 channels and 6 on 9219 modules. This system communicates to the host via ethernet.

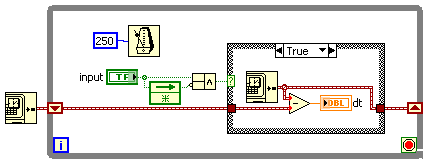

I have prepared a vi (see attachment), which used two DMA FIFO for writing data to data acquisition at a different speed. I will be sampling the s and 9211 9219 much more slow (500ms by samples), than other channels (40 ch/kech. / s). Currently, my FPGA vi trying only to taste two different modules. When I run the present on the host vi and try to read the data, I get only extracts of the data at different intervals. If either of her would reveal latency with the connection or the host vi failed to refresh quite quickly? I am relatively new to labview, so any help is appreciated. Thank you.

Gaussy

Hi Guassy,

There are a few things that you need to change:

(1) you must separate your acquisition in the FPGA in two separate loops if they have to operate at different speeds. As it is, probably will run at the slower speed of the two parameters.

(2) you must do the same in your VI in real time, or set up the DMA readings so that they will be read at the same pace. For example, suppose that a single module acquires 1000 hz and the other at 200 hz. If you want to read 100 samples from the first module (so your reading will occur at 1000 hz / 100 samples = 10 hz), you will need to read 20 samples from the slower module, so it is synchronized with the first module.

(3) your timeouts are too short on your DMA readings. Your slow acquisition is 500 us. It will take 50 ms to read 100 samples requested, but the delay is set for 10 ms, so 4 times over 5 playback will return nothing.

(4) you use graphics and no graphics. A chart will only show the current data buffer that was written for her. Refresh rate of the façade is nondeterministic, so that you can't see every update. If you use a chart, the chart will record all data written on it to the indicated depth (default is 1024 elements).

Also remember that you can have three FIFOs DMA between the host and the target FPGA, so use them wisely. It is often easier to perform your purchases on the FPGA at the same pace and send them through the DMA FIFO even in VI in real-time. If you need a few channels to connect at a lower rate, you can always throw the excess samples (there are some decimate wave screws that are perfect for this).

I hope that helps!

-

FPGA code with the evolution of the modules

I need to create FPGA code to a cRIO-9072 facing the development of the modules.

My cRIO will have a number any NI 9203 (analog acquisition) and modules OR 9411 (acquisition digital) as inserted by the operator. When turning the power on, the system must identify two possible modules were inserted in each of the slots. Subsequently, he will then know what choices of code to call to acquire data from the individual modules.

I found the article in the knowledge base for CRY that queries each module and again reports the type of module and I can use it to successfully detect modules, but what LabVIEW fails to allow me to do this is to compile my FPGA code that was designed to deal with possible modules. After compiling, I get the error: "IO found point FPGA project. You must add the I/O item in the Project Explorer window, or select a different element in the control of FPGA of IO or the constant"because the compiler requires the appropriate modules are configured in the LabVIEW project. Unfortunately, this would require two different modules to be configured for each slot at the same time as there are sections of code for the 9203 modules and sections for 9411 modules for all eight locations coexist in a vi.

Anyone have any ideas on how to get LabVIEW to compile my FPGA code somehow?

Many thanks in advance,

With the current draft of LabVIEW FPGA, you cannot compile a LabVIEW FPGA VI which manages several configurations of C Series modules.

For your application, you must create a target of your project for each of the possible configurations of module and build the corresponding FPGA VI. Then, compile each of the screws to create the necessary for each configuration FPGA bitstream. Then in your host VI, you can detect what the current configuration of the module and download the binary stream appropriate for the FPGA. Another issue to consider is that the reference to the FPGA VI/bitstream returned by the open FPGA VI reference function will be unique to each bitstream/module configuration. So in your host VI, you'll need treat each configuration of the module with a separate set of code by contacting the FPGA.

If you consider only two different modules and an eight slot chassis, there are 9 modules possible combinations. The condition would be to the end user to place all modules of the same type together, either from the left or the right side of the chassis.

-

We have a compact device of cRIO-9072 Rio FPGA.

1 analogue out, analogue 2 in 1 race of SSR. My program works well, but I can't get the cycle time for update reads to move faster than about 1 second / cycle.

I perform a host VI and the target FPGA VI. The clock frequency is 40 M.

I know this isn't much information but I can't find genericly how to control the speed of this card FPGA update. I would like to be updated about 10 to 100 times faster.

Any ideas?

Thank you

tophatjim

Most likely, the CRDD is slowing down the speed of the loop on the FPGA. I assume you are using the module 9485.

You must place the I/O nodes for your different modules in different loops so that your HAVE and AO can run faster. Updates of the CRDD will run more slowly in their own loop.

-

elapsed time after two output pulses

I have a gas with an output signal meter (or perhaps more accurately, a closing contact) for each cubic foot, put in the meter. The tricky part is that the closing time varies over time as the gas flow increases.

I am sucessfully measure the total volume of gas used in a 'run' by using a shift register to compare a change (closed or open) and divide the total by two changes. However, I would like to note the elapsed time for each foot cube through the meter and the putput that on-screen. This number should only be updated when each cubic foot passes through the meter. It's simple if it was just an impulse, or even two an amout set apart, but I have a problem with the irregularity.

No matter if the timer has elapsed begins on the forehead or the edge down so it starts and ends at the same place and the inverse of this number is then displayed on the screen.

My current control loop is a timed loop iterations to 250ms on a cRIO 9072.

Any advice on how to implement or the display would be great!

Hi, NXT,.

detect the rising edges of your meter. Store the current time in a shift on rising register and get the difference to the previous hour:

-

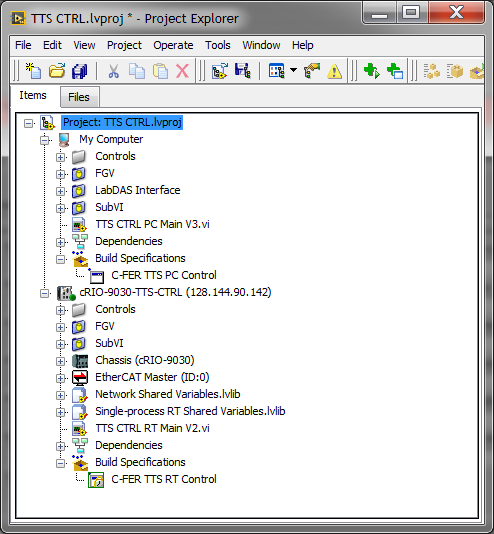

I have a project including a VI RT running on a cRIO-9030 and a host VI running on a desktop computer. The two programs communicate via shared variables that are hosted on the cRIO. As shows, when I run the screw of the project, everything works as expected. When I compile the RT VI in a start-up executable can deploy for the cRIO, as well as the libraries of shared variables (the record of support in the build specification-oriented), I am unable to connect to the executable running in real time.

I have 'Disable Autodeploy Variables' checked on the cRIO target, if I no longer get the prompt to stop the currently running application to deploy the variables. The host VI opens and appears to run, but has no connection with shared variables (data does not update). Compilation of the host VI as an executable file and it works outside the project result in the same behavior.

I read some relevant posts / knowledge base articles related to this problem, but still can't seem to find a way around it. I note a number of articles on the series in double bond of variables, but this is in contradiction with my possible behavior for this system: I finally have a number of cRIO controllers identical all runnning the same executable RT and want to be able to have a single host VI which allows the user to select from a list of available controllers (using the screw system configuration) and extract the host name of the controller selected, that would be later used for programmatic addressing of the variables on the host of part VI.

In any case, I want to start with the simple fact of being able to get that first controller running without an open connection to the RT VI project. With the deployed executable start, I checked via programmed behavior of LED application of the RT and FPGA are running on the cRIO. The problem, I think, has to do with shared variables, but I'm not sure where to go from here. I want to connect to RT executable running from the VI to the host (in project) to verify that the compiled executable of RT works as expected and then the subsequently compile host VI in an executable that can be run from any desktop on the local subnet.

Thoughts?

It seems that the error has now been corrected. There were three things, I changed: the file startup.aliases in the startup on the target directory (Home: / lvuser/natinst/bin) put in 'localhost' as an alias for the controller. I changed it to the IP address of the controller. Then, I got some features of IO files in my application RT relative paths using the path obtained by the 'current path VI' VI. As this path changes according to the location / delivery system, I had to create a VI that has used the Application property: type with a case properly structure band / build railroads desired regardless of the runtime system data files. This may have broke my RT request. Finally, I got a property node in one of my RT SubVIs, who attempted to change an indicator in the Subvi, which is not taken care of in an RT compiled executable. I can't do this for debugging purposes somewhere along the way, but in any case, I removed it, and after a recompilation and the deployment of the executable of RT, everything seems to work as expected today. The host VI on the desktop can connect to the application of the RT project, and when it is compiled into an executable file, which also works.

-

Getting 7 error with the HTTP POST vi method when deplyed ISO crio as executable... urgent!

Hi all

I have an application where I can access the net server point of LabVIEW via the HTTP protocol to send the data. My application works fine when I run it on XP, and also sometimes on cRIO. I'm writing and reading files to store and read data from the server.

When I do my application executable and deployed on cRIO I am constantly 7 error that says "Error in the node library function to call at the POST vi LabVIEWHTTPCLIENT".

After getting this error if I try to run the my new project the crio (not through exe) I keep getting the same error. This means once the executable file is deployed on the crio, I get the error in my project application which was working fine before you deploy the executable file.

7 occurs very frequently. and I am unable to find the reason. I gave all the paths in the constant form located on crio and files accessible also when the application is run.

Is someone can you please help me what this error 7?

as a result, that it is bound to the HTTP POST vi method...

How can it be fix?

Its quite urgent...

Thanks in advance.

Solution is provided by the NOR... Vi POST method missing two files that need to be there in the startup of the CRIO.insted folder there is in the system folder. That's why when running the exe that the startup on crio application it gives error as the files are not there. The fix for this HTTP POST vi update isn't out yet EITHER.

-

Deployment complete with static Variables cRio-9074 network errors, pc with executable file

Hello.

I am building an application runs on a machine without LabVIEW development system and connect via the network shared a cRIO Varibles (RT FIFO). I can successfully create an installer and EXE for PC and a RTEXE for the cRio. When I run on my development computer, the application is able to communicate using variables shared without a problem.

But, when I install my application on another computer and connect the cRIO, I get the following error when you deploy shared variables when the application starts:

Initializing...

Calculating dependencies...

The checking for conflicts. This operation can take a long time.

Preparation itesm by download. This operation can take a long time.

Deployment 169.254.84.198

Deployment VariableLib.lvlib\\169.254.84.198\VariablesLib (:-2147467259,)

LabVIEW: Unspecified error (Hex 0 x 800004005).).

Completed with errors of deployment

I created an exception in the Windows Firewall configuration. I have included the library of VariableLib on the EXE of RT, outside and inside the exe file to c:\.

I am downloading the SP1 for LabVIEW and Module RT and decided to reinstall all the software on my cRio.

Any help will be appreciated.

Hello Luis.

Thank you very much for your help. The Variable engine OR has been and should be included in the intallation.

I was able to get the application running. I installed the System Manager distributed on the PC without LabVIEW to control if the library has been get deployed. Using what I found that another device on the network use the same IP address as the cRio and so the IP address has been lying to the deployment, but the device has returned an error. I just changed the IP address on the cRio and I was good to go. I have not reproduced on both devices such as network shared Variables suggests on some positions, nor I needed to modify the ALIAS files on devices.

Best regards and thanks again for your time.

-

cRIO-9002 - sees in MAX but Can not control

I have a cRIO-9002 with chassis cRIO-9201, I try to configure so that I can use it for a new project in the lab that I am working. So far I was able to get on our network and am able to see to the MAX; However, once I click on it in MAX, MAX is here trying to cool off for a while and system resources all is listed as not available (once MAX gives up on refresh). I'm not able to see the installed software and it disconnects frequently. I turned on the CONSOLE OUT on the cRIO and here is the result:

[2J

General software embedded STPC BIOS 2000 (tm) revision 5.2Copyright (C) 2003 General Software, Inc.

Copyright (C) 2004 National Instruments Corp.

Controller OR cRIO-9002

[23; 01 H (C) 1996-2003 General Software, Inc..]

STPC - 5.2 - 01DE-EB2E [01; 01 H [06; 01 PM

00000016K low memory passed

00000512

0000058900000000K Ext memory passed

00031744 [08; 01 pm [s [u [08; 01HWait...]]]PCI device table.

Bus Dev Func VendID DevID class Irq

0 b 00 00 and 104 has 0201 Host Bridge

0c 00 00 104 a 0210 ISA Bridge

00 0D a 00 104, 0229 IDE Controller 11

0E 00 00 104 a 0230 Serial Bus 11

0f 00 00 104 a 0238 Ethernet 11

00 18 00 1093 705E 11 unknown device

1F 00 00 104 a 0981 Ethernet 10

[2JBIOS review: 1.1.9 (10/08/04)]

Firmware revision: 10.1.94

LabVIEW RT the start player...

FAT16

Jump to 07E0:0000

Checksum: 018D9C6A

Executive in time real LabVIEW

Construction time: June 21, 2011 01:17:21

(C) copyright 2002-2011 National Instruments Corporation

MAX system identification name: englab-fpga

LabVIEW time real Single-Core Kernel

The initialization of the network...

Device 1 - MAC addr: 00:80:2F:0 A: 7E:E2 - 131.151.115.38/22 (primary - auto)

System Web server started

NOR-RIO 4.0 Server started successfully.

NI-VISA 5.1 Server started successfully.

Welcome to LabVIEW Real-time 11.0

FTP SERVER ERROR: Cannot start threaded

FTP SERVER ERROR: Cannot start threaded

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

FTP SERVER ERROR: Could not create threaded command

Of course, there is some kind of problem here, but I don't know what it is. Any ideas?

Hi nslogan

What version of the drivers OR RIO, LabVIEW and LabVIEW RT do you have installed on your computer?

OR MAX was able to communicate the fine before? Nothing changed?

Is your cRIO executes any RT executable launch, request or communication with an FTP server?

If your computer has all the software and drivers may be easier trying to format and reinstall the cRIO, it doesn't take long and it takes a few simple steps.

How do I format my target in real time and reinstall the software?

Concerning

R. Esteban

-

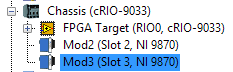

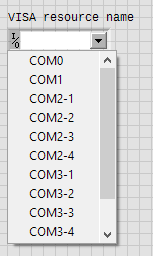

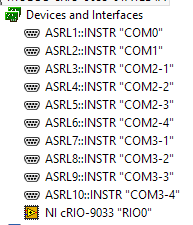

9033 OR & NI 9870 - series recording parameters do not restart the cRIO.

Hello

I have a cRIO OR 9033 with two RS232 9870 cards. The two cards series and their ports do not appear when I turn on the cRIO. When I run my executable in real time, once it crashes, saying: he cannot find the ports I ask. After that it crashes, the channels appear in MAX and VISA resource controls, and when I run the program a second time, it works very well. Why does this happen? Is it possible that I can have the save of the series, so I don't need to have the program crash whenever the cRIO starts?

I run my program in hybrid mode. I Interface FPGA and including two maps cRIO outside the FPGA target, like this:

I tried the cancellation of the deployment and the deployment of all, but it does not help. It blocks the first time regardless if I execute the suite of LabVIEW Development or if I deploy it as an RT executable and run at startup.

Here are some pictures of what is happening:

10-port VISA should be available. The two on the chassis and four for each card to 9870.

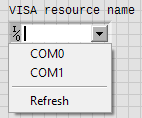

When I start first cRIO, only the ports of two chassis looks for selection in a control channel VISA:

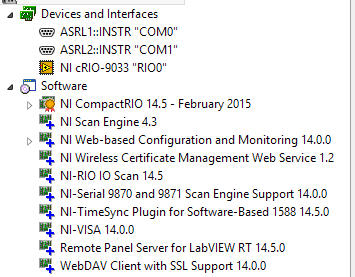

And the channels do not arise to the MAX:

Showing also currently installed software.

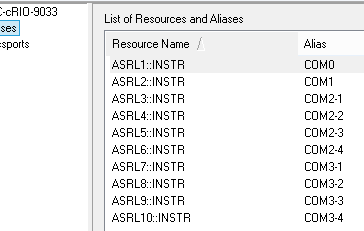

When I go to the settings of NI-VISA 14.0.0 page I see this:

Channels appear here, but nowhere else.

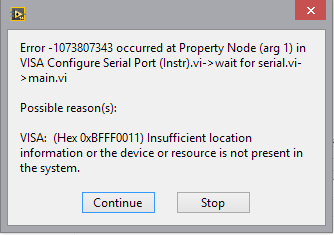

When I try to run my program, I get this error:

And after the error, the channels appear in LabVIEW and MAX!

Series settings will remain as long as I leave the cRIO powered. If I disable, settings series pannals and I need run my program once only it crash before I can use the serial ports.

I would really like for these settings apply automatically without having it fail the first time.

Any suggestions?

I also run hybrid FPGA on cRIO with cards 9870 and 9871 under the scanning engine you are. I also noticed behaviour buggy when accessing the COM ports - for example, if the cRIO running the executable version of his program and you interrupt it to run the same program in interactive mode, often, you receive the error message "missing resources VISA." So what I do is restart the cRIO with the disabled startup application.

I honestly would not bother to configure anything through MAX when it comes to your cRIO. You configure port configuration programmatically. In the process of initialization of your program, open your bitfile, run it, wait, a few seconds to have everything settle, make a VISA "find resources" and confirm all your ports appear, then use the VISA to configure and open the port by program. This way worked for me.

-

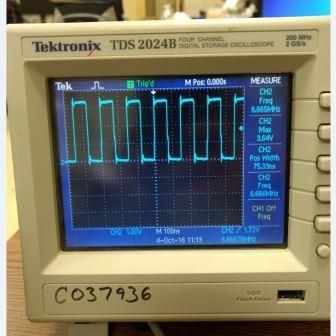

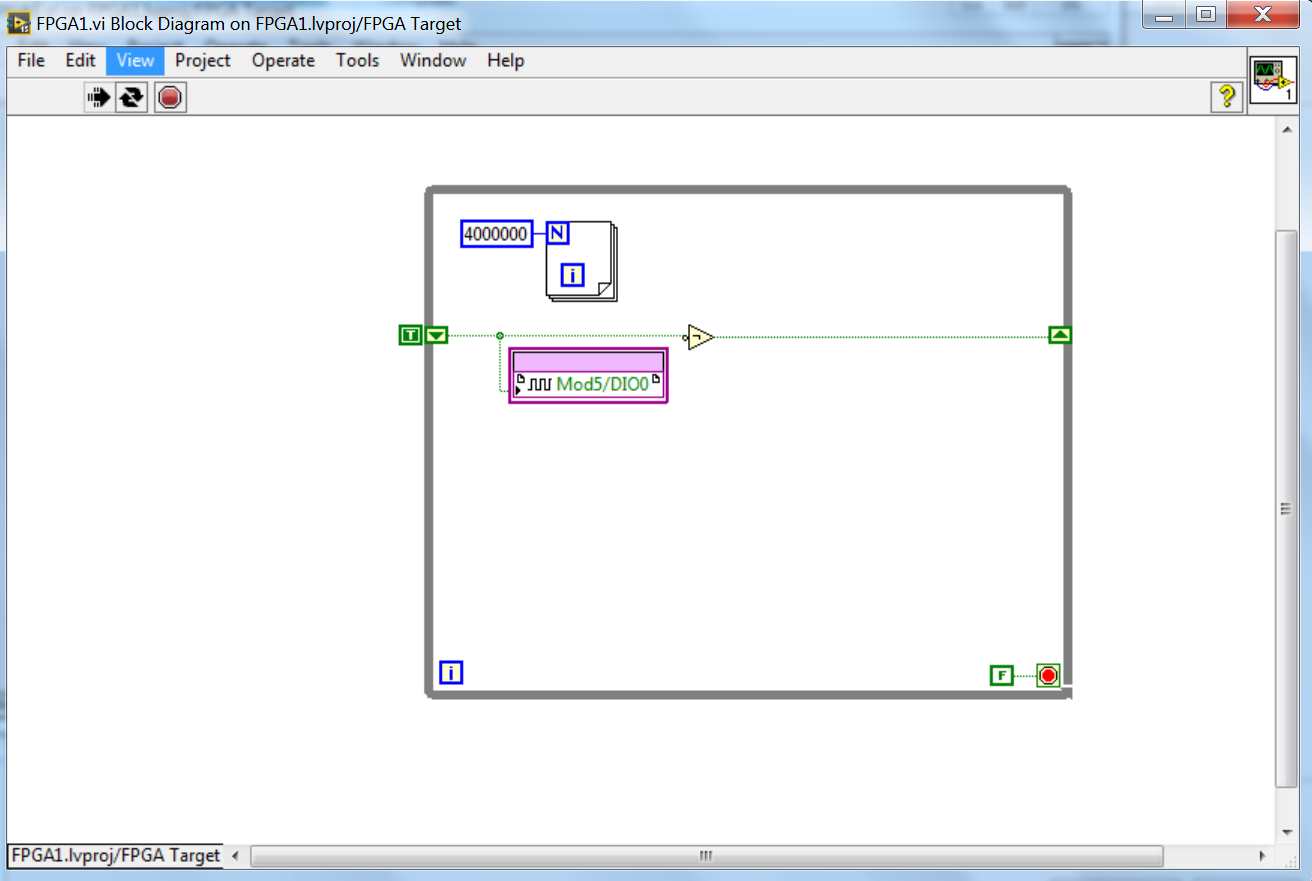

FPGA CRio do not give good digital outputs

I'm working on a project with the compact RIO fpga. I tried following the youtube tutorials and written tutorial, but I get no similar results in scanning FPGA interface.

I have attached my project. Here's the signal that I get from the Basic VI, which is a digital IO defined as output in a while loop. Alongside this, there is a loop for fundamentally changing the frequency of the digital signal from the top down. But whatever number I put in the loop for, it gives me the same frequency.

My thought process goes like this: If the CRio has a processing time of 40 MHz to a loop that cycles 400 times should give me a swing of 100 kHz output, which is not any number, I put in.

Any help is appreciated.

Thank you.

LabVIEW is almost certainly that compile to loop out like dead code (nothing happens so LabVIEW gets rid of it). I advise to use the loop timer function if you are looking to change the frequency or put everything in a timed loop. All in a timed loop will execute a tick.

Maybe you are looking for

-

Hello! How can I install Firefox OS on Huawei TT101? Is it good? And will it be upgraded by WiFi? Is italian available? Is it faster than CyanogenMod 7? I have just a problem: after I installed CyanogenMod 7, my tablet can not be accessed soon after

-

I have a hp photosmart 5510 and Hp sent me a replacement due to a different problem. When I plugged it in for the first time I get an error message saying print head is missing. I tried troubleshooting on their website and nothing has helped. Does a

-

Well I did just have written a letter very very long, I had been typing for more than two hours, I right click it and copied... But my computer crashed and shut how do I get this letter?

-

Hello I have a new laptop HP Pavilion D002tx, Windows 7 x 64. I did a clean install. I found all the drivers on the HP site PCI\VEN_10EC & DEV_5229 & SUBSYS_21BC103C & REV_01PCI\VEN_10EC & DEV_5229 & SUBSYS_21BC103CPCI\VEN_10EC & DEV_5229 & CC_FF0000

-

I downloaded El Capitan. Now how to load images to bridge?

I had no problem before downloading, and Apple isn't going to help. I got my card from my 6 d and to the bridge it is said it can not read this device and I have no idea how to download the images. Please can you help me?