FPGA compile incorrectly configured worker

Hello

I've recently updated my software using the CD that spring 2014. I have NI LabVIEW 2013 Professional sake system. Now all the screws project, I used to compile successfully are communication error. It is said that compile worker is configured incorrectly. How can I configure it correctly? I am a new user of LabVIEW FPGA. I am attaching screenshots of a project that I do as an exercise. Someone can you please tell me what I'm doing wrong and how can I fix this problem. I will be grateful.

Thank you and best regards,

Kamal

I installed the hotfix published by OR for the compilation tools from Xilinx 14.4 and after installing this patch, I have no difficulties in the compilation of the screws. I am grateful to all those who have offered their help to solve this problem. Thank you very much.

Kind regards

Kathar

Tags: NI Software

Similar Questions

-

Question of server FPGA compile

Hello

I want to implement a system of compilation farm. There is only a PC development (possibly 1 later) and compiles a worker. The question is, the compile Server (one which dishes to the worker of the compilation of the tasks) possible on the same PC used for development, and in the affirmative, he introduced the bottleneck important compared to using a dedicated machine?

Thank you

Hi ToeCutter,

The compile server can be on the same PC that is used for development without any problem

' ' ' ' Refer to the getting started with the FPGA document compile farm, available by selecting Start "all programs" National Instruments "FPGA" start-up of the farm to compile FPGA, for more information about configuring and using FPGA compile farm.

Use "localhost" as the host name of the server for your compilations to compile.

Compile farm server uses the same compiling installed tools (Xilinx) on your PC, but instead to directly obtain the LabVIEW project files

It compiles the files downloaded by the user, there is no difference in performance.

I hope that helps!

Kind regards

-

FPGA compile Server Corruption

Background:

I have an installation of Windows 7 64 bit running on an i7-930. In Oct. I installed LabVIEW FPGA 2009 SP1 build server from a copy of the .iso image of NEITHER.

In addition, I have VMWare Player installed with the full development suite installed, targeting the server hosts compile.

We book this system into 'production' for the 3 months preceding the feast of the new year...

Question:

When I returned from vacation, not a single machine in the factory can hit the compile server on Win7 host, including installed VMWare LV tools running on the same PC. It seems that the clock carried over from 2010 to 2011, and the compile server went poof! Initially, the compile Server complained that Xilinx tools license had expired. Once I reinstalled the server compilation, nothing can connect to it, not the server errors, delays network comes from the development tool.

Troubleshooting:

Obvious things:

' 1) ' reboot ' on the VMWare image and host; no change,.

(2) double check anti-virus is disabled; no change,.

(3) check the Windows Firewall is disabled; no change,.

VMware, other servers in fine compilation on the work of the other PC on the network (for VMWare isn't the issue, but played with bridged vs NAT anyway; without change).

VMware, the 'local host' compiles Server works very well (remember, it's that of virtualization, it doesn't have the VM host on Win7 version).

Reinstall the server compilation; no change.

But here's where things get funky. The IVR folder with the compile server has only a handful of files it contains with no record. On the other compiling work servers, IVR file is loaded with support files files. It's as if the installer does not install all the files right...

Copy IVR system folder of work on top of the half installed folder; no change. Bluff installation and start fresh with another to continue troubleshooting (this has been done a lot)...

Do the various Registry hacks to take away the remains of uninstall process and align with the work of compiling server machines registers; no change.

Walked through the Knowledge Base of NI.com and Forums. Several issues that either I solved with relocations, left unanswered, or have been resolved without getting clarification on exactly what happened or how to fix it.

A run the TList hack manually (difficulty TList.vi does not unless you have the run-time installed LabVIEW and my Win7 OS host does not work). no change.

Hunting the Perflib fix rabbit in this hole; no change.

Next steps:

Will try to install it from another copy of the DVD LVFPGA in case my .iso image have fried or 'cleaned' by McAfee.

Any ideas? I would like to avoid reimage your computer for a number of practical reasons, including not seen the Win7 install DVD without invoking the wrath of it, tape / associated explanations invoking it or the huge amount of time lost in this process (and the square itself)...

I saw a funny similar behavior when you use a server remote compilation when VMware gets thrown into the mix.

My specific case was:

Windows XP (32 bit) Welcome + to compile the server

Reviews of Windows XP (32 bit) + LV development system (bridged network operation)

Under certain conditions (I couldn't understand what was the trigger), LV development system could not connect to the server for compilation. Boost LV and even the virtual machine it ran into would not solve the issue. Moving the server to another physical machine compilation does not resolve the issue.

All firewalls was extinguished without a change in behavior.

I ended up resorting to statically assigning the port that the server remote compilation using this KB works on:

http://digital.NI.com/public.nsf/allkb/BE02DC97330CD1D8862576A500015AB8

Once set, all my LV development environments have been configured to use static port. I have not seen the problem since. I think there may be some problems with Service Locator of NEITHER when dealing with VMware.

It doesn't sound like you are experiencing exactly the same problem, but this can give you more options to try.

-

Sync error, incorrectly configured server after the installation of Update 7.0.1

Since the update of Firefox (I have a Mac OS 10.6.9 on SnowLepard) by installing the Firefox 7.0.1 update, now on every page I get the Sync error message at the bottom line. Incorrectly configured server.

Synchronization error message constantly displayed after updating to Firefox 7.0.1

There is currently a problem with the Firefox Sync server, and the developers are working to fix it. See http://status.mozilla.com/ for updates.

-

Why is the FPGA Compiler server so slow?

FPGA Cloud compiler is faster because NO servers are performing, right?

Well, my Windows 7 PC is powerful, but no luck there!Total CPU utilization is never more than 25% and the total memory (including other applications) usage is less than 16%.

Why, the compile Server uses all available resources? has been restricted?

How can I leverage more power from my PC?If servers OR compile faster code, there must be a plausible explanation / reason?

Please indicate, how to make the compile server running faster in place?I don't know what machines compilation cloud service works, but I do not.

It seems that the compilation is much faster on a Linux machine on a Windows machine (I think I've heard up to 30% faster). The Linux FPGA compile server is available for LV2012. Set up a Linux machine with a clock high enough CPU and RAM speed and you will get on the fastest possible compilation with current tools.

-

tables of fixed size in FPGA compilation error - how to implement a waveform control in an FPGA?

Hello

After being stuck for two days, please let me briefly describe my project and the problem:

I want to use the cRIO FPGA for iterative control of waveforms. I want to capture a full period of the waveform, subtracting a reference waveform period and apply control algorithms on this. Subsequently the new period of correction must be sent again for the output module OR. If it does not work, the captured waveform will look like the one reference after several iterations.

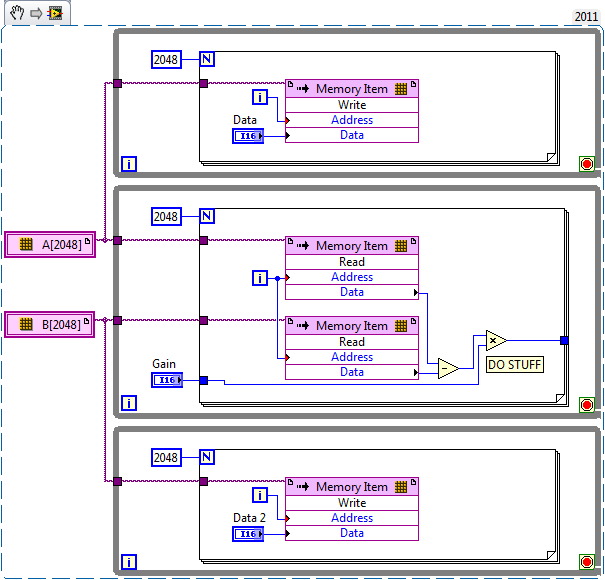

I am planing to create an array of size fixed for the capture and the reference waveform (each around 2,000 items for a given period). I use so 2 paintings of each elements of 2000. I use the function 'replace the subset of table' to update each element captured in the loop sampling and a feedback for each table node to keep in memory (I also tried shift registers, but then the berries do not have a fixed size any more and I can't start the compilation process).

If I try to compile the FPGA vi, I get the following error:

Details:

ERROR ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

ortability:3 - Xilinx this application runs out of memory or met a memory conflict. Use of current memory is 4167696 KB. You can try to increase physical or virtual memory of your system. If you are using a Win32 system, you can increase your application from 2 GB to 3 GB memory using the 3 G switch in your boot.ini file. For more information, please visit Xilinx answer Record #14932. For technical support on this issue, you can open a WebCase with this project attached to http://www.xilinx.com/support.

"Synthesize - XST" process failedBefore I added berries to my code I could compile the FPGA without problems. So, it seems that the tables are too big for the FPGA. :-(

Therefore, I would like to ask if there is perhaps a better method to implement my problem in LabVIEW FPGA? How could avoid the tables to save my waveforms on a period?

Thanks a lot for your help in advance.

Best regards

Andreas

Unfortunately, the LabVIEW FPGA compiler cannot deduct stores shipped from berries (yet). When you create these two large paintings, you are creating essentially several registers very, very large. Just by looking at your picture, I guess that there are at least 4 copies of each of the tables.

You want to use LabVIEW FPGA memories instead. You can create memories outside the loop and then read/write them where you are currently referencing the berries. The only change that you really need to do is to break down your treatment in scalar operations. I have attached a simplified version of your plan, I hope it helps. Let us know if you have any other questions.

-

Question of FPGA compile farm 2012

I was under the impression that my FPGA LV code can be compiled by several workers when I bought and installed the FPGA compile farm Toolkit. What I have, however, is that each work of compilation can only be compiled by a worker. I expect that a single compilation work can be divided by the number of workers.

So I see that a worker of computers will compile two computers of worker work. It's just that a worker will be compiled at the same time.

I just misunderstand the features to compile farm Toolkit or is it an installation problem?

Thank you

No, a unique compilation cannot be shared between workers. Nature of the beast-FPGA "compilation" is not something that lends itself to parallelism. You have the advantage that the build tools run much faster under linux, however.

-

GRAVE: Password file may be missing or incorrectly configured.

Platform: windows xp 32-bit

Refresh your Oracle 10.2.0.2 to 10.2.0.5 patch 4 (Group) (P820632)

WHEN you use the DBUA I get the following on C:\oracle\product\10.2.0\db_1\cfgtoollogs\emca\ftdcdb\emca_2010-08-19_02-37-49-PM.log

The dabatase works well (East and upward and running), I can connect, run sql queries, but I wanted to update EM too, but I am not able to understand this, someone has any suggestions? Basically, the problem is on the part of The Enterprise Manager.

GRAVE: Password file may be missing or incorrectly configured.

See the log file at C:\oracle\product\10.2.0\db_1\cfgtoollogs\emca\ftdcdb\emca_2010-08-19_02-37-49-PM.log for more details.

August 19, 2010 14:38:14 oracle.sysman.emcp.EMConfig perform

CONFIG: Stack Trace:

oracle.sysman.emcp.exception.EMConfigException: password file may be missing or incorrectly configured.

at oracle.sysman.emcp.ParamsManager.checkPwdFile(ParamsManager.java:2633)

at oracle.sysman.emcp.EMDBPreConfig.performConfiguration(EMDBPreConfig.java:690)

at oracle.sysman.emcp.EMDBPreConfig.invoke(EMDBPreConfig.java:255)

at oracle.sysman.emcp.EMDBPreConfig.invoke(EMDBPreConfig.java:176)

at oracle.sysman.emcp.EMConfig.perform(EMConfig.java:170)

at oracle.sysman.emcp.EMConfigAssistant.invokeEMCA(EMConfigAssistant.java:494)

at oracle.sysman.emcp.EMConfigAssistant.performConfiguration(EMConfigAssistant.java:1161)

at oracle.sysman.emcp.EMConfigAssistant.statusMain(EMConfigAssistant.java:478)

at oracle.sysman.emcp.EMConfigAssistant.main(EMConfigAssistant.java:426)Re-create the password file...

-

FPGA Compilation fails because of the mistake of Xilinx

My FPGA compiles and I cannot understand why. There is nothing crazy in my FPGA VI of really, it seems strange to have this type of problem. I can't reach the code because its owner, but it's pretty simple because it reads all channels from a single module and records them in a data FIFO. I have compiled successfully any FPGA code on this computer, so I should definitely have everything needed to compile.

My system consists of one NOR cRIO 9030 with a single module 9220. Below is the Compilation of summaries.

---

LabVIEW FPGA: Compilation failed due to an error of Xilinx.

Details:

ERROR: [Synth 8-1031] knidmahighspeedsinkbase is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:295]

ERROR: [Synth 8-1031] knidmahighspeedsinksize is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:296]

ERROR: [Synth 8-1031] knidmahighspeedsinkbase is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:301]

ERROR: [Synth 8-1031] knidmahighspeedsinkbase is not declared [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:302]

INFO: [Synth 8-2810] pkgshimswitchedlinkdmaportifc unit ignored due to previous errors [/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/PkgShimSwitchedLinkDmaPortIfc.vhd:68]

---------------------------------------------------------------------------------

Development of finished RTL: time (s): UC = 00:00:07. delay = 00:00:31. Memory (MB): peak = 798.605; gain = 204.203

---------------------------------------------------------------------------------

ERROR: [Common 17-39] 'source' is not due to previous errors.

INFO: [Common 17-83] release license: synthesis

3 info, 0 Warnings, 0 critical warnings and 4 errors.

synth_design failed

: ERROR: [Common 17-39] 'source' is not due to previous errors.When running

«source - notrace.» /. Xil/Vivado-6035-ip-10-60-203-176/realtime/toplevel_gen.tcl ".

called inside

«synth_design-top "toplevel_gen" - part "xc7k70tfbg676-1"-"full" flatten_hierarchy "»»

(file "/ opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/synthesize.tcl" line 21)

called inside

"source" / opt/apps/NIFPGA/jobs/mC683d5_WCf98Qm/synthesize.tcl "" "

exit #.

INFO: [Common 17-206] exit Vivado at Tue Mar 24 23:58:54 2015...Compile time

---------------------------

Introduction date: 24/03/2015-16:46

Date recovered results: 24/03/2015-17:00

Waiting time in the queue: 00:24

Compilation of time: 13:22

-Generate a Xilinx IP: 00:00

-Summarize - Vivado: 01:27Compilation has restarted on

24/03/2015-16:57---

Any help would be much appreciated!

Thank you

James.Morris wrote:

Okay, so it seems that I get the error with a project from scratch and an FPGA with a single command and an indicator.

I download the latest FPGA 2014 SP1 installation and I hope that will solve my problem.

Well I'll mend, which fixed the problem! Somewhere along the line, my install FPGA must be corrupted.

Thanks for the help, guys.

-

After uninstalling my XPSp3 o.e., I started getting the following error message: "the address book failed to load. Outlook Express is incorrectly configured, please re-install. "at the start of XP and the machine.

Uninstalling included 7 entries registry to remove all the * files dbx and files *.wab addressbook, except himself. After uninstalling and receipt of the error message above, I tried to use my CD of XP OS to re - install O.E. as a component of Microsoft without success.

I upgraded to Outlook 2007 and imported to the address book of O.E. successfully before uninstalling.

Please advise me how to get rid of the error message always appearing at startup.

Thank you

You can't really uninstall and reinstall OE without having to reinstall XP as OE is a part of it. I hope your foray into the registry does not require a reinstall of XP.You now have the DBX files? WAB files?If Outlook has been on your machine before this event, see the reference by PA Bear in this thread

http://social.answers.Microsoft.com/forums/en-us/xpnetwork/thread/a8c8cf17-d792-481e-BCCA-13b03852a995If Outlook has not been installed, see these.All of you who have the same cause. Something is screwed up with your address book.It could be several specific problems, which include:

-corrupted WAB file

-damaged or incompatible DLL files for the addressbook

-have OE set to use the Outlook98 / 2000 + contacts instead of the WAB

folder and there is something wrong at the end of OutlookFor more details, take a look at:Error message: the Message could not be sent. Some invalid recipients

(Outlook Express: there was an error opening this message)

(The address book failed to load. OE is configured incorrectly)

(Corrupted or incompatible WAB32. DLL file)

http://support.Microsoft.com/?kbid=239135

OLEXP: Error Message: failed to load address book

(There was an error opening this message)

http://support.Microsoft.com/?kbid=269777

http://support.Microsoft.com/?kbid=310873

OLEXP: MSIMN has caused an IPF in Module Wab32.dll

http://support.Microsoft.com/?kbid=247706

Error message: failed to load address book, Outlook Express is...

http://support.Microsoft.com/?kbid=191946

Error message: could not open address book, a component is missing

http://support.Microsoft.com/?kbid=192321The address book Windows (WAB)

http://www.insideoe.com/files/WAB.htmTo share Contacts between Outlook and Outlook Express

http://www.slipstick.com/contacts/oeshare.htm -

I can't launch Messenger and AVG anti-virus because next to incorrect configuration.

Hi, I can not start my Live messenger as msncon.dll and msnmsgr.exe cannot start because next to incorrect configuration. I tried to uninstall and reinstall the essential MSN and removed the Microsoft Visual c++ redistributable...

Now my antivirus AVG cannot also be launch due next to incorrect configuration.

For your kind assistance, please.

Hi Hokkle,

1. have you reinstalled the latest version of the Visual C++ Redistributable package?

Method 1: Users have solved similar issue by installing the latest version of Microsoft Visual C++ 2010 Redistributable Package.

You can see thefollowing links to download the Visual C++ package for the version of Windows that you are using.

Package redistributable Microsoft Visual C++ 2010 (x 86)

Package redistributable Microsoft Visual C++ 2010 (x 64)

Method 2:

You can also scan [SFC] System File Checker on the computer that will replace missing or corrupt files & check if the problem persists.

For more information, you can consult the following link.

For more information, consult the following link:

Check the logs in Event Viewer for more information on this issue.

What are the information in event logs? (Event Viewer)

Hope this information is useful.

-

Incorrect configuration of update KB2559049

Original title: incorrect Configuration of update

Update (KB2559049) will not properly configure during the next reboot after installation.

[1] Q5. All specified updates installed, except for KB2544521

[2] , I have installed on my system "Trusteer report"

[3] Q1. Microsoft Security Essential. No third-party firewall.

Q3. Free trial of McAfee.

Q4. Firefox, Chrome and Safari.

A1. If IE9 installed, KB2544521 would not be installed.

A2. Many other Internet Explorer users have reported that KB2559049 will install after uninstalling Trusteer report & restart the computer. Give it a try.

CF. http://answers.microsoft.com/thread/fa3bae62-312b-4428-963e-8260b9dde33c

A3. If still no joy...

Please answer all the questions of diagnostic following by number in your very next answer (no need to quote this post):

1. when (date about) don't you install Microsoft Security Essentials (MSE) and has been the computer fully-patched to Windows Update in time?

2. What antivirus application was installed before installing MSE, was your subscription always news, and did you uninstall it before installing MSE?

3. do you have a uninstall the pre-installed McAfee free version to test AND THEN (b) download/run the McAfee Consumer products removal tool & reboot (c) before installing any other anti-virus applications (especially MSE) as well as updates of Windows (including the Service Packs & IE) upgrades?

-

Network status reports "an incorrect configuration detected.

Network status reports "an incorrect configuration detected.

Ensure that the physical switch and the ports used by Virtual SAN are active and enabled multicast. Enabling multicast can be made in one of the two tracks on your physical switches:

- Disabling IGMP surveillance.

- Configure IGMP snooping for selective traffic

Also, validate the configuration of the virtual switch for correct uplink VLAN, NIC failover configuration of team strategy and the virtual SAN traffic service is enabled on the VMkernel interfaces.

Virtual SAN requires a VMkernel network with active virtual SAN traffic interface. All members of the cluster need to communicate on the same network segment of L2 with multicast enabled, and all members of the cluster should be able to ping each other. Having failed to meet this requirement will prevent virtual SAN to be configured successfully, since it prevents the hosts communicate.

-

HY all!

I have a few questions using Xilinx compiler tools.

The reason why I want to use FPGA is to get the analog measurements of two modules NI 9205 and also filter these measures. Modules are configured to run in terminal diff mode, while the other parameters of this module are set to default values (+/-10 V etc.).

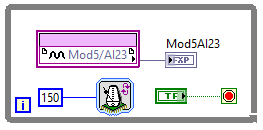

2.1 when I try to compile the program easier - read one analog measurement every 150 US, see the figure below - just compilation takes too much time, namely fear for a few hours, specifically, compiling stucks on mapping. I followed my PC performance, processor is about 20% 3.84 GHz, while the memory is on 10% 31.9 GB. Q1: is it possible to configure the compiler to use as many resources as possible PC?

I'll post probably questions once I managed to get this simpler program to work

Thank you in advance!

Best regards

Marko.

Hello

What operating system do you use? I read somewhere on this forum that windows 8 and possibly windows 10 are not taken in charge by xilinx compilator.

I have simular problem faceing with the compilation of the code. On Windows 8 compilation take over 50 minutes and not finished yet. Then tried to compile the same code on Windows 7 it only take 10 minutes. -

stuck FPGA compilation, no errors

Hello

I wrote a LabVIEW FPGA 8.6.1 program (I have written several, this is my most recent). When I run it on the development computer it seems to work fine without any errors. When I try to compile, however, it still stalls on this part:

'Analysis of generic entity

library ( Architecture). This isn't feeze (the compiler is always updated time and you can see it working). It just doesn't progress no further than this point. By chance, does anyone know what could cause this? I know that maybe it's a little vague, sorry. Thank you!

Nevermind, I figured it. I had a knot of analog input within a For loop. This wire entry (i.e. given out the analog input node) was connected to a tunnel auto-index on the loop For I have just disabled automatic indexing on this tunnel and everything seems to compile fine now.

Maybe you are looking for

-

you periodically to Apple TV, mine will suddenly link is no longer

You have updated Apple TV? Mine connects suddenly is no longer. Good HDMI cable. Need to connect to the computer and go to iTunes for a updated?

-

How to restore the icon of mail on the iPhone 5

How can I find the mail icon, which has disappeared from my icons?

-

How can I remove wiseofferz popup ad on my mac?

How can I remove wiseofferz popup ad on my mac? I'm glad that you have set the preferences to block pop ups, but this doesn't seem to work. Thanks in advance

-

partition on hard drive for windows vista Ultimate edition

Hello iwant to repartition my HDD = 160 gigabytes to install windows vista ultimate on it so I would like to know how to make the partition (C) for windows vista ultimate

-

Visual Studio 2015 connection Bug

Hello My provisional driving licence expired on Visual Studio 2015 and I need to connect get a new one. The access to the sign on screen in Visual Studio via the sign in button and enter in my (valid registered Microsoft) email, I gives me the follow