FPGA dynamic Refnum

I am trying to auto index a table of fixed-size FPGA of IO constants. The wire and the loop tunnel in the loop for the error even "possibility of dynamic Refnum not supported for the current target. What does that mean and what someone has suggestions to work around this problem.

Hey Waldo, I would recommend having a look at the following KBs. Occurancs and refnums must be statically defined in LV-FPGA applications. This is by far the most common reason for this error.

By passing an instance of a Subvi in LabVIEW FPGA

http://digital.NI.com/public.nsf/allkb/30496B921D344B8686256FEF005224D6?OpenDocument

Can I get a reference to a Subvi, which runs in the FPGA?

I hope this is useful,

Best wishes

Tags: NI Software

Similar Questions

-

Impossible to check the FPGA reference with "not a number/path/Refnum?

How can I check if an FPGA interface refnum is valid? It seems (LabVIEW 2009) that "Not a number/path/Refnum?" always returns true when connected to the output of open FPGA VI reference. I write code that needs to be able to run without an FPGA for testing purposes, so I wrapped all calls to the FPGA in a case structure that I thought would run only if the FPGA reference is valid. Turns out that they run ever, even when the FPGA reference is valid (probe shows it has a numerical value, and the FPGA VI is running). I guess it's sort of similar to semaphore and appointment of references that have their own special function to verify the validity, but I do not see such a function for FPGA. I have to cast to int and check if it is not equal to zero?

-

Cluster for the FPGA reference constraint

I have a cluster of clusters. One of the internal piles went 25-29 items, but I forgot to update several of my Subvi reflect. I remember before when I did, I got a broken line not executable VI, but now the result is a constraint. You can really force a cluster with multiple items to a cluster with fewer items? My outdoor group consists of some FPGA with clusters of register references.

Hi Adams,

FPGA reference is the special data of type "FPGA dynamic reference", which includes a cluster of records, elements, and associated with the referenced FPGA personality FIFO dynamically. Dynamic data types do not follow the same rules of coercion expected of them a defined data type statically to follow. The dynamic nature of reference FPGA son allow wire any FPGA reference in the entry of an order of read/write, regardless of whether the control of read/write was created explicility for the FPGA reference. This makes it much more practical FPGA programming.

-

compactRIO: selection channel dynamically

Hello

I would like to order multiple power supplies using compactRIO PCI modules, AI / AO. The problem is that I need a solution that fits good based on how many power supplies are controlled by a perticular cRIO system. There could be 5 on a single system and there could be 40 on the other so I won't have to change the program every time, I'd rather just a simple configuration for each source file. I thought that I could set up all parameters power supply and sense in a multidimensional array then have a loop to process each entry in the array. Speed can be a bit of a problem since you can not deal with this in parallel but the speed is not too big of a concern right now.

My problem with this plan is that I do not know how to select a channel in the FPGA dynamically, without that it does not seem that my idea would work. One has a few suggestions on how to deal with this? Is there a way to select the channel you want to acquire the deactivation data? Or y at - it a better way to make a program like this that can cope with an indefinite number of power supplies? Help and feedback would be greatly appreciated.

Pawel

You can create a program by using the scan Mode which will assign dynamic channels based on which modules are present.

White paper this gives an overview of this operation

and this example goes into details

Discovery by programming, Configuration and access of the system CompactRIO Scan Mode IO in LabVIEW

-Hunter

-

Hi all

Currently I develop an app RT on LabView 2014 SP1 which consists of three parts:

- A PC vi that read the data and sends it to the target of RT;

- A RT vi running on the CRio-9074 which receives data, convert it to current values and send it to current output modules. It also sends PFGA a number of pulses must be generated.

- A FPGA target that receives a number of pulses to be generated and then do the work by a module ttl

Things will work perfectly when the RT vi cover is open on the PC. This happens when I enter debug mode simply run the vi RT of the Project Explorer. The problem started to happen when I tried to run the program without the RT vi front open. After some research, I discovered that the application of the RT was generating an error 1055 in a stream property node. The strange thing is that this does not happen while the RT vi façade is displayed on the PC!

Althouth it seems to be a problem known as I found on the Web site of NOR, it is not clear for me, how do I solve the problem. Should I just close the RT VI, open it, close the vial, compile and deploy it finally? Well, if it is that means that workaround, it did not...

537230 Changes to the VI with dynamic references breaks VI with the error-1055 the Node property

When a VI deployment that allows to get a dynamic to refer to a control on a x 64 Linux target in real time, the VI deploys successfully. After you make a change to the VI, error-1055 is thrown from any node property is trying to access the dynamic refnum. The error says "error-1055 has occurred to the property node...". »Workaround: Close, and then reopen VI.

Report version: 2014 SP1 Solved Version: N/A Added the: 23/07/2015 Thank you all for the help. I use a few cards in the RT vi and was the use of the nodes properties to clear the history. These cards are only for the control of the application while it is still in development, and it worked fine while I ran the RT application with its façade exposed on the PC screen. At the moment I leave be executed only in the CRio, he started planting and throwing the error 1055. I removed the nodes properties because they are not indispensable and everything works fine.

-

LOCATION:

-I am developing a software plugin based on plug-ins based on LabVIEW classes that are instantiated in running. Plugin real classes come from the plug in generic classes that define interfaces to the VI instantiation and can provide basic functionality. This means that many of the methods of the class are dynamic distribution and even methods of child classes can call the parent method.

-Plugins top level (the ones directly accessible by the main VI) each have a run method that animates a plug-in specific state transitions.

-Transitions of the plug-in data acquisition (DAQ class) class calls a method of the DAQ class that reads data from an FPGA card OR and transmits to another component via a queue.

PROBLEM:

-Higher sampling rate, a FPGA-to-host FIFO overflow occurs after some time. When I "weigh" the system just by moving a window of Firefox browser on the screen, the overflow is triggered immediately. I did not have this kind of problem in older software, where I was also reading a FIFO of FPGA, but made no use of LabVIEW classes or diagrams.

SOLUTIONS I'VE TRIED (WITHOUT SUCCESS):

-J' put the transitions in a timed (instead of a simple while loop) loop that I assigned specifically to an own kernel (I have a quad-core processor), while I left all the other loops of my app (there many of them) in any simple loops. FIFO overflow still occurs, however.

QUESTION:

-Does anyone have a tip how I could fix this problem? What could be the cause: dynamic distribution methods, the acquisition of data of state transitions or just the fact that I have a large number of loops? However, I cannot change the fact that I have dynamic distribution methods because it is the essence of my architecture...

Tips are greatly appreciated!

I've now changed the execution priority of all the screws involved in reading of the FPGA FIFO '(highest) priority critical time '. This seems to be improving the situation much: so far I have not a FIFO overflow, even when I move around the windows on the screen. I hope it stays like that...

-

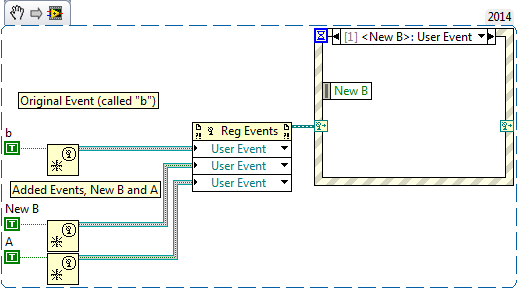

Add more dynamic events registration refnum

Hello

I have a wire that passes Event Registration refnum to my structure of the event. This thread is from VI, that I don't want to touch. He spent recording for the cluster of user events.

I would add more dynamic events to the refnum (but not to the cluster), so I would like to re-record with the addition of new events.

When I'm passing this refnum to block 'Register for events', LabVIEW does not allow me to expand this block and add new events, which I think is understandable.

How can I add more dynamic events to the refnum?

Close, but no cigar. When you add user events, you want to be sure that every event has a unique name, then name your constants defining the events differently (as shown here).

Bob Schor

-

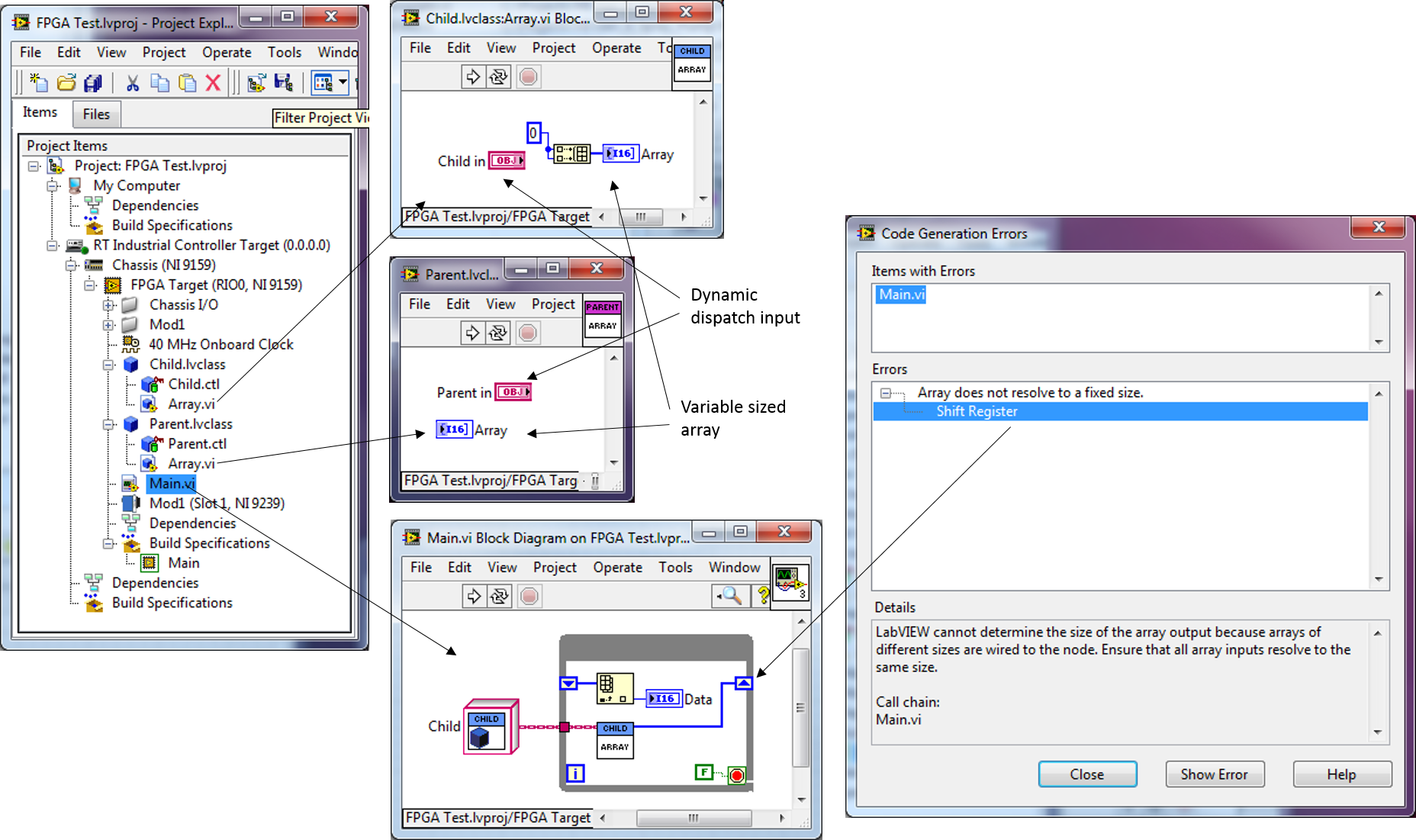

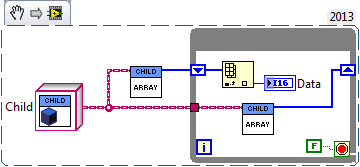

Dynamic release of variable size of dispatch class method array on FPGA

I have a parent on the FPGA class that will serve as a model/framework for future code which is developed. I had planned on creating a class of the child and by substituting a few methods. The child class constant would have fallen on the schema so that the compiler would have no trouble knowing which method (parent or child) should be used (i.e. the parent method will in fact never used and will not be compiled with the main code). The output of one of the methods is a table. This table will have a different size depending on the application. I set the size of array as a variable. In the method of the child, there is no doubt about the size of the array so that the compiler must be able to understand. However, when I try to compile, I get an error on the size of the array. I can't figure a way around it. Any thoughts would be greatly appreciated!

Thanks, Patrick

The question implies the use of the register shift unitialized. On the first iteration of the loop, the value that comes out of the shift register is the default value for the data type, which is an empty array for a table (size zero). Therefore, unless wire you a table empty for the shift register to the right, the size of the array cannot infer statically by the compiler.

To resolve this problem, you must feed an initial value for the table. Here, I just used the function of the matrix, but if you need to have a separate method that returns an array of default or the size of the array that will work as well.

-

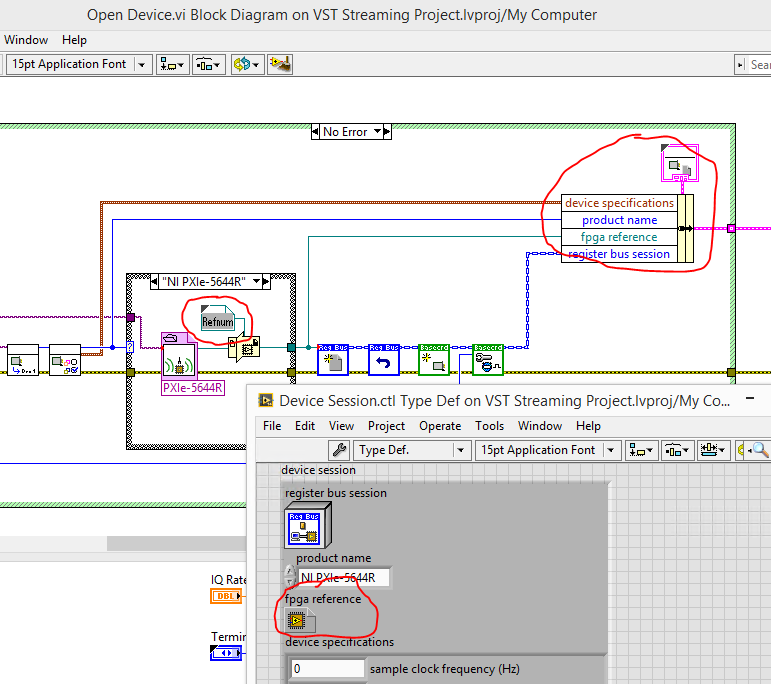

I play with a VST 5644 and model VST streaming. On the FPGA VI, I added the code, then added an indicator of the face before of the FPGA VI and compiled. Executes the FPGA VI in interactive execution mode, the indicator works well. Side host, however, I can't access the new indicator with read/write control.

Coming out of the open FPGA VI reference I can see the indicator on the wire, but in the Dynamic Cast of Interface FPGA function is have rooted out the refnum somehow. If I connect to control read/write directly to the output of the function of open reference I can access the indicator very well.

No idea what I am doing wrong?

Thank you.

You re-configured your FPGA VI reference with the new bitfile interface? The cast of dynamic interface defines the lead as all methods and indicators according to the type of wire connected. You can right click on the constant of type and select "Configure the FPGA VI... of reference". In the pop up window that follows, select "import of bitfile...". "and select the new bitfile you've built.

You must update the fpga reference type in the "Device Session.ctl" type def as well. This is the type that you will be able to access throughout the project.

-

Hello

I use card FPGA 7966R with Module of e/s 6587. I have two sets of screws FPGA, one that uses 6587 mode series (Serdi channel) and the other in parallel mode (Serdi connector). I'm trying to select one of the FPGA VIs via the host VI and I don't know if it's possible.

Some things to note:

- All IOs have the same names, FIFO has the same data type and name.

- Because they use the IO 6587 controller in a different configuration, I can't parallelize them and combine them into a single VI.

Thank you

MILIN

You should take a look at the function of Bitfile dynamic reference opened .

-

Reverse and pseudo inverse Matrix on FPGA

Hi all

How can I calculate matrix inverse/pinv on pushed more logical clock (*.gcdl), for FPGA? (Labview Comms 2.0)

Maybe someone has a solution for this task? Or that the best algorithm I use for this task?Thank you.

Hello togoto,.

We have matrix Inverse and matrix screw Pseudo-inverse for code side host, but these are not supported on FPGA. The reason for this is because without a known matrix size, there is not a way to implement a dynamic matrix math function (the compiler couldn't know how many resources which requires). If we consider that more algorithms of inverse depend on the division, which is very intensive on FPGA resources, which provides another reason why we would be unable to put implementation in CDL.

That being said, Comms has Matrix multiply and transpose the matrix of features that you can implement in CDL. Because for a long time the matrices are always a fixed size and uniform, you can implement a custom algorithm to achieve pseudoinversion and matrix inversion. It would take careful pipelining to ensure it worked in a single clock cycle.

Could you elaborate on what exactly the application is supposed to accomplish? If possible, the math movement matrix your screw host-side may be the best approach.

Best,

Daniel

-

problem running example project USRP FPGA connected via Ethernet

Hello

I am trying to run the example project of USRP FPGA on a USRP-2940R connected to a PC windows using Ethernet. I have not made any changes to the FPGA VI or screw host and I'm tryign to run the host Rx in Streaming, VI. I get the error-63180 function Open Bitfile dynamic reference (called from the VI open device), with a possible reason for "the specified resource name is a reserved word or an invalid alias. Alias of RIO can only contain alphanumeric characters, '-' and '_ '. I specified an IP (192.168.10.2) for entry of address of device to function. I guess the address of the device is the problem. This who should I be specifying the address of device in this case. Any help would be greatly appreciated.

Jerry

jerrysydir wrote:

The restriction you mentioned is specific to the USRP platform? The website NOR talk using Labview FPGA with a RIO Ethernet expansion chassis. (http://www.ni.com/tutorial/11703/en/).

LabVIEW FPGA on Ethernet is only available through LabVIEW RT. Behind the scenes of the target is still connected to the well RT via PCIe controller and then the RT controller is connected to the host via Ethernet. There are also some USB LabVIEW FPGA targets (http://www.ni.com/white-paper/14821/en/).

For the RIO USRP, MXIe is currently the only bus taken in charge for LabVIEW FPGA.

-

Open FPGA references change to no. target when compiled with executable in time real start

Hello again you useful forum fans! I have a problem that I hope someone can give me a hand with.

I have a project that has a Windows component and a component of the target in real time, that are running on a hypervisor type NI PXI-8110 system. Communication both sides between them using shared variables.

On the real-time side, I have four FPGA targets who are reading and writing various analog and discrete inputs and outputs. I several periods loops which opens a reference to one of the FPGA targets during the first call, then pass this reference in several subVIs that read and write to panels prior to the FPGA. The loops the FPGA reference thus made available and reuse it in the next iteration through the shift registers. Each FPGA target has only a single reference open to him. One of the loops is using the FPGA reference directly and does not pass it in any subVIs.

It all works very well in the development environment, I can read and control inputs and outputs FPGAS via the front panel of the application of the side Windows. It also works very well if I start the game real time in the development environment, and run the code of windows as a stand-alone executable file.

However, when I compile the code in real-time in an executable startup and deploy it to the target, it does not work. I enabled debugging on the executable, and when I connect to it via the operation-> debug executable in the menu, I see an arrow broken at execution. Further investigation shows that each of the four open screw reference FPGA is now empty, the text under them is "no target" and the thread for reference on their part to my first Subvi is broken. I need your help to understand how to operate as it does in the development environment.

I followed the instructions of these two knowledge base articles to compile and download the bitfiles FPGA on the FPGA target and execute on start or restart:

http://digital.NI.com/public.nsf/allkb/39795847AC67296D862575FB0046944F

http://digital.NI.com/public.nsf/allkb/BC513C2A0DC29C89862574BF0002B0B9?OpenDocument

Open FPGA reference screw are configured for the FPGA to build specifications that I created for each target in the LabVIEW FPGA project.

I called technical support, NO phone, and yet were able to determine this one out, so additional "brownie" points if you do!

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.

I would offer you the same no detailed screenshot that I have (I can't give more detailed code out because its owner, unfortunately), but apparently the forum doesn't like my image file, as I can't seem to load.Please let me know if you have any ideas regarding what is happening! I appreciate it.

Jon,

I'm always up for the challenge. Have you tryied recompile the FPGA VI that accesses the RT VI? I also suggest to try and open the bitfile instead of the FPGA VI. You run in dynamic mode (this is not a suggestion, it's just a question)? There is no difference if you try to open the FPGA VI reference outside the while loop, then past the reference to use inside the while loop without shift registers, then close the reference to the FPGA VI outside the while loop?

Let me know if these suggestions makes no difference.

-

Exhibitor block signal - Xilinx FFT v7.1 - FlexRIO - FPGA

I use Xilinx FFT v7.1 IP (FPGA - OR 7965R, LabVIEW 2012). I am computing the FFT of real integer 16 bit signed.

Bit 5 signal exposing block block floating point FFT in module v7.1 Xilinx FFT signed or unsigned? Pdf document talks shift to the right of the data output to use the dynamic range, mentions not moving to the left, neither gives sufficient detail on this subject.

Is there a base value as format IEEE floating point should I use to find the correct output value?

I guess that it is unsigned unless you have comments to the contrary. The basic behavior is to keep bits on the left in order to prevent any overflow, so the scale always implies move on to when you think that some of the more significant bits are unused. They provide an example of b00101 = 5, so that indicates there is no bias to apply.

-

Events unregistering on a cluster without Unregistering for all dynamic events

Hello everyone

I've been playing with dynamic event record but I hit a problem.

Normally if I want to stop triggering events on a single control I will be wire constant ref with the correct type in the registry for block of events. This means that I don't have to use the unregister for events block and then rebuild the entire events list to registry when I only want to stop the events on a control.

However, if I try to bring together a group of the refs (which cannot necessarily be of the same type) in a cluster then I can no longer cancel the events on this cluster registration from the register of events work a group of control constants.

An alternative would be to use an array instead of a cluster, but this has two disadvantages: it does not create a case of dynamic event for each Member of the array and all controls must be the same type or they are co-erced to a more generic control class.

I've attached an example VI (labVIEW 2011 SP1)

I think I finally get the problem now.

You need feed two references in separately. You can cluster the registry OUT for events, I know, but I don't think that what you want will work. You know that you can enter the tables in a table instead of a cluster, right?

Shane.

PS to be clearer.

Register to activate your button separately from the rest. Save all your "to be marketed" references - individually, not clustered - in a second 'register to events' and then together the two outputs (with the Save refnums event) before passing into the structure of the event. You might have what you want. So big cluster AFTER signing up, not before.

Maybe you are looking for

-

Can I use the fingerprint and password to unlock the phone?

Is there a way to allow the fingerprint reader to unlock the passcode as second security (or even it the other way around would be better for me, I like to read reviews before you unlock and put another finger on the button count as a lot of fingerpr

-

How should I go for an i have read e-mail notifications

When a recipient has read an email me how to do a review so I know that the email has been read.

-

I have a combo DVD/CD-RW drive in my Tecra 9000, model number UJDA710. Unfortunately, when I start the laptop, I get the message Error in IDE #1.It will always start in Windows XP, but the drive is not available and isnot shown in Device Manager. I r

-

How to save data quickly to the high sampling frequency

Hi all I use a structure of producers and customers to measure and record the data. The sampling rate must be as high as 10 kHz. Given that so much data, it takes a long time before the data is saved. At first, I saved the data in an excel sheet. The

-

Win7 upgrade or version disk full?

I'm currently running Vista Home Premium and want to upgrade to Win7 Home Premium. I know that the upgrade disk is cheaper but I would like to have the full version sitting around, in case something goes south and I need to perform a clean reinstall