FPGA Interface Cast question

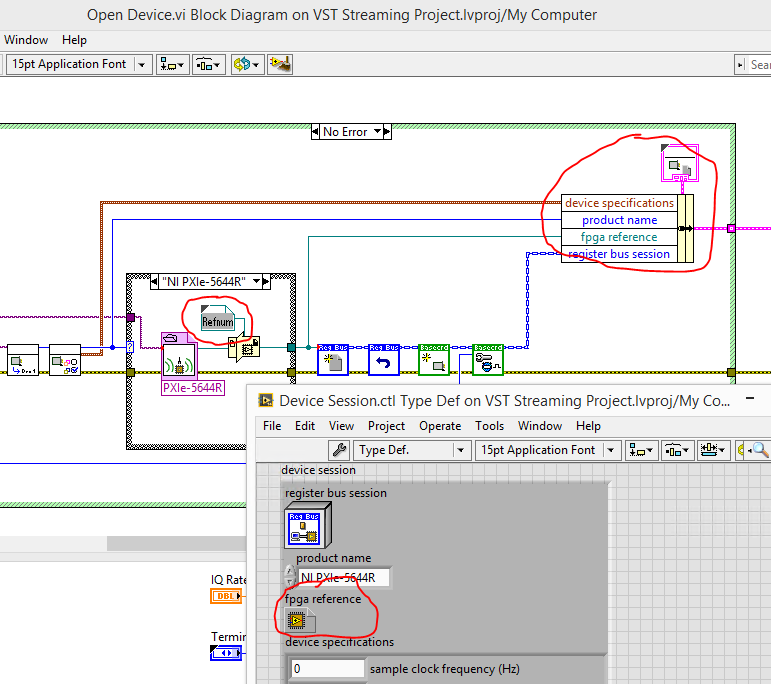

I play with a VST 5644 and model VST streaming. On the FPGA VI, I added the code, then added an indicator of the face before of the FPGA VI and compiled. Executes the FPGA VI in interactive execution mode, the indicator works well. Side host, however, I can't access the new indicator with read/write control.

Coming out of the open FPGA VI reference I can see the indicator on the wire, but in the Dynamic Cast of Interface FPGA function is have rooted out the refnum somehow. If I connect to control read/write directly to the output of the function of open reference I can access the indicator very well.

No idea what I am doing wrong?

Thank you.

You re-configured your FPGA VI reference with the new bitfile interface? The cast of dynamic interface defines the lead as all methods and indicators according to the type of wire connected. You can right click on the constant of type and select "Configure the FPGA VI... of reference". In the pop up window that follows, select "import of bitfile...". "and select the new bitfile you've built.

You must update the fpga reference type in the "Device Session.ctl" type def as well. This is the type that you will be able to access throughout the project.

Tags: NI Products

Similar Questions

-

General questions about FPGA Interface C API 2.0

I developed an application in LabVIEW FPGA 2011 on a Board of the R-Series PXI and a host application LabVIEW 2011 Windows XP to communicate with him via DMA FIFO. I'm trying to adapt the interface to CVI 8.1 (preferred) or CVI 2009 using the Interface of FPGA C API 2.0. The example of FIFO that it stores in the directory C:\Documents and Settings\All Users\Documents\National Instruments\FPGA Interface C API\Examples\ gave me a few questions:

- The functions NiFpga_WriteFifoI16 and NiFpga_AcquireFifoWriteElementsI16 are two different ways to do the same thing? I wasn't clear where I do the extra copy if you use NiFpga_WriteFifoI16. I guess the combination of NiFpga_AcquireFifoWriteElementsI16 with NiFpga_ReleaseFifoElements is the way to go if I want to stay out of trouble.

- I intend to call NiFpga_Initialize and NiFpga_Open in an initialization function that gives the word initially, then keep the session handle in calls to other functions. The session handle is always not null when it opens successfully? Could I use it as a test to make sure that I have a session valid before calling any other functions-example:

If (session) {NiFpga_WriteFifoI16 (...)} - Interface of FPGA C API 2.0 is only announced work in CVI 2009 up on. If I include NiFpga.c and .h in my project CVI 8.1, it seems to compile fine, but I did have the chance to integrate yet. Is there something specific that would make CVI 8.1 not work? Our deployment environment of difficult application CVI upgrades

-Jim

Jim,

With regard to your questions:

1. Yes, these two functions are the same, however there is a big difference between the two. NiFpga_AcquireFifoWriteElementsI16 acquires, prepares and publishes FIFO elements to avoid the need to write the first in a buffer allocated by the separate user, then copy the contents of the elements in the memeory host buffer. Considering that, in the NiFpga_WriteFifoI16 does not work. So the NiFpga_ReleaseFifoElements should always be used with the NiFpga_WriteFifoI16. The example is just showing how the code should be used, but is not necessarily displayed works should be used together. I understand perfectly why he was confusing.

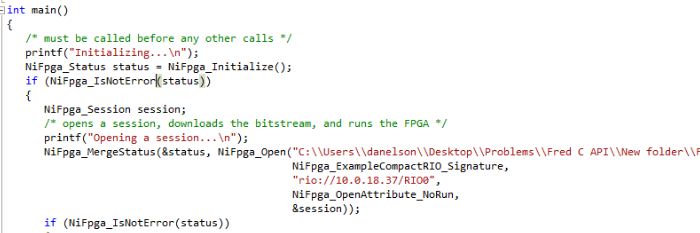

2. the best way to ensure you have a valid session is by using the NiFpga_IsNotError() function. I've attached a screenshot of the example code that illustrates how best to achieve this and inserted the image below.

3 regarding using CVI 8.1, there is nothing in particular, which would make your code does not work in point 8.1, but we can guarantee that C API 2.0 will work correctly with 9.0.

Kind regards

Larry H.

-

Error-63101 when executing the FPGA Interface C API Generator in LabVIEW 2012

I'm using LabWindows CVI 2012 and 2012 LabVIEW FPGA module. I try to use the FPGA Interface C API generator and I get the following error from a freshly generated .lvbitx bitfile. I use the local server compiles on my PC.

Error-63101

NOR-RIO: A valid .lvbitx bitfile is required. If you are using a valid .lvbitx bitfile, the bitfile maybe isn't compatible with the software you use. Determine which version of LabVIEW was used to make the bitfile, upgrade your software to this version or later, and then try again.

The problem occurs when executing CVI or LabVIEW. I was able to do this earlier when I was compiling the FPGA in LabVIEW with the API generator 2011 downloaded from the Web site.

A bit of weirdness in my setup, it's that I charged it off downloads from the website (latest files after 2012 NIWeek) rather than the normal distribution DVD. I installed LabVIEW, so NI RIO, then the Xilinx tools compatible with 2012. It works very well when you talk to the FPGA to a LabVIEW vi running on my Windows PC to the host.

Any suggestions?

Problem solved. I had to download FPGA Interface C API generator 12.0. It works now.

I would have thought that if a product was called on the menu in LabVIEW 2012, it would be prompted to upgrade to a compatible version, when I installed LabVIEW. The old version is not compatible with version 3.0 bitfiles, as identified on the following lines at the top of the .lvbitx file:

3.0 -

NEITHER 9512 with Labview FPGA Interface

Is it possible to use the NI 9512 stepper with Labview FPGA interface drive unit or is it only possible to use it with the interface of scanning? When I try to add the module to a FPGA target, I get an error telling me that Labview FPGA does not support this module with the latest version of NOR-RIO, but I have the latest version of OR-installed RIO.

Hi Checkit,

You're right - the 9512 cannot currently be used in FPGA. There is an error in the documentation. The 9514 and 9516 can, however.

-

FPGA Interface C API, error-63105, OR-RIO: C/C++ identifier is already in use and cannot be created.

Hello

Installation program:

1 x the NI PCIe-7841R

When I am trying to automatically generate a C++ API for my top FPGA VI using the FPGA Interface C API 12.0 I get the following error.

Error-63105

NOR-RIO:

The "NiFpga_FPGATop_IndicatorBool_DMAFIFOtimeoutoccured" C/C++ identifier is already in use and cannot be created.

Anyone know what this means? Is there some kind of limitation on the appellation of front interface controls?

/Mola

Problem solved.

I had placed two flags with the same name on the front panel - by mistake. It builds the FPGA without errors, but the C API generator was not in favour of that.

/ Mola

-

Safe multithreading NI FPGA Interface C API?

Hello

I use the FPGA C API interface to communicate with the software labview on my FPGA OR. Some calls take a while to run, for example, reading on a FIFO so long timeout. So far, I assumed that the interface was not safe multithreading. It has now become annoying given the timeout problem described above. Try simply was not good, it can take a long time to create a "collison.

Is the FPGA interface safe multithreading C API? Or, more specifically, the functions of FIFO reading can be called in parallel with read/write variables on the FPGA?

Thank you.

Hello MKAP,.

It has been a while since I used the NI FPGA Interface C API, but it is what I remember and seem to be able to remember (and also found in the documentation):

Functions related to the unloading and loading of the library are not thread-safe:

http://zone.NI.com/reference/en-XX/help/372928D-01/CAPI/functions_required/

On itself, this should be a problem:

Your application should require that the NiFpga_Initialize is called before any other function associated with function calls NIFpga.

In a similar way that unloading (NiFpga_Initialize) lof NiFpga brary should occur only when you are finished using it.

With regard to multithreading, you must also keep in mind its mono-thread interrupts IRQ (if you plan to use them):

http://zone.NI.com/reference/en-XX/help/372928D-01/CAPI/functions_interrupt/

-

Sharing of Variables does not not under an FPGA interface?

Hi all

I have a controller 9074 cRIO 9074 chassis.

I defined a number of variables shared under my RIO controller and writing a UI VI in my host PC, where I feed some variables of network shared in RIO and get another return to RIO on the front panel of my host. Naturally, the VI which deals with read/write variable network data to IO channels real is under my RIO controller.

The problem is that, although everything seems to work fine when my RIO is set to the interface of the Scan Engine, the same screws give the following error message when I pass my RIO FPGA interface dependent.

-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

Possible reasons:

CompactRIO: (Hex 0xFFFF0000) unable to communicate with the module. Re-insert the module and check the connections. If the chassis is in Interface FPGA programming mode, make sure that you have opened a FPGA reference bitfile or VI FPGA with the load of the Interface of scanning for the module you are trying to access using the scanning Interface.

This error or warning occurred when writing the following shared Variable:

\\AMR-cRIO9074\B1-DO\JCV1_C1_B1

\\160.40.15.231\B1-DO\JCV1_C1_B1-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------

Note that I get this error message for each channel of e/s that I call my RIO. Also note that it is there still no reference FPGA currently in any of the screws... I want to solve the problem is because later, I'll have to add some FPGA in my code, so I can not just impersonating my RIO scan interface...

Any help would be appreciated,

Harry

When you disable scanning on the cRIO platform engine, you must have some runing FPGA code.

There is noway that knows your controller on any module, and he can't read anything from any module.

If you do not have an FPGA vi, which sends the values of a port of the module on your controller, you need to do active Scan Engine.

The error message clearly indicate that you must have an open reference FPGA vi or analytical engine to be able to read the values of and to a module.

You are able to have custom analysis engine and a footstool of FPGA code at the same time on an FPGA.

Is there a reason you do not run with the scanning engine?

-

Control of read/write of FPGA Interface

I need help on control of FPGA read/write Interface. I would like to connect data TCP Read (String) directly to VI FPGA Read, but the entrance is an FXP... How can I do this?

Then change your FPGA control to be a byte (U8). On the side of your host, use the array of strings of bytes, then Index Array to get the specific byte you want to write on the FPGA.

-

ASA "route inside 0 0 192.168.1.1 by tunnel" interface ACL question

Hello

Small question around the road inside 0.0.0.0 0.0.0.0 192.168.1.2 in tunnel command.

Do you need to add a u-turn traffic within the ACL interfaces (for example internet related http traffic) or 'same-security-traffic permit intra-interface' negates the need of this?

So if my site remote vpn outside is 10.1.1.0/24 should I add entering permitted statements for the 10.1.1.0/24 inside my interface.

Thank you

same-security-traffic permit intra-interface allows then-input-output traffic on a single interface

allowed incoming 10.1.1.0/24 statement in the list ACL allows traffic (output - then-) penetration on a single interface, but you must disable the RPF check

-

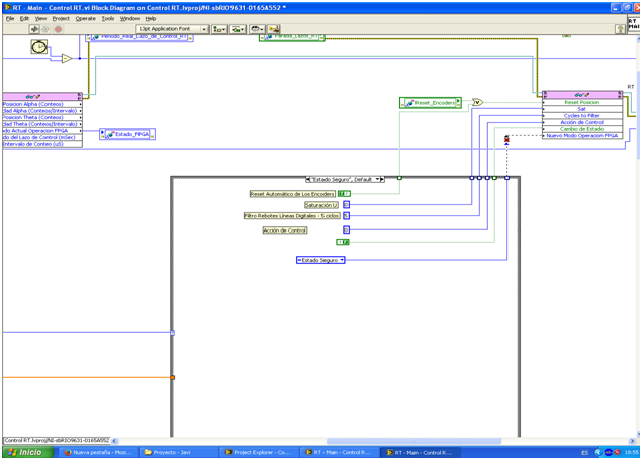

Broken thread - FPGA Interface Node error

Hello

I am programming my application of RT and I get this weird error:

As you can see, I'm trying to set the value of a FPGA control (which is a typedef enum) and I get this strange cut wire

for me, error.

I was looking for a solution in the forums but I luckily able to get a... Could someone help me?

Thank you!!

PS: The error message was "the type of sink is zero" that is false, as already defined in the FPGA vi.

Solved.

To the right, it was like if I've changed some of typedefs and who did not have in mind. Recompiling solved the problem.

-

FPGA interface of data acquisition

I have a repetitive loop in a PXI-7813R producing reasons. The output of the PXI-7813R is TTL, but I need 0-15V levels. In the same PXI chassis, I have a DAQ (PXI-6528) hardware that can handle the voltage levels. The question is, can I somehow link the the 6528 7813R patterns using PXI backplane and leave this market while I wear the use of PXI rack for other functions?

Thank you

Andy Quick

The problem with the PXI-6528, is that it is software programmed. Which means trigger won't help you here.

What you need to do is to do some work of material. You can have the PXI-7813R output profiles and drive an opto-coupler or FET circuit to change the level of voltage of 15V. Or maybe there is there a digital stamp which can output 15V for you.

-

LabVIEW Interface Kinect question

Hello. I hope someone can help with this problem. I try to get the Kinect Demo.vi LabVIEW and additional vi (from Kinect LabVIEW using Microsoft Kinect API Interface) to run on my system:

64-bit Windows 7 Professional SP1

LabVIEW 2011 w / Vision

Microsoft Kinect SDK (most recent)

.NET 4.0

I was able to get the vi to load without errors, but when I run it I get the error message attached.

7 error to the constructor of node in Kinect_API.lvlib:Initialize Kinect.vi-> Kinect_API.lvlib:Kinect Demo.vi

Possible reasons:

LabVIEW: File not found. The file may have been moved or deleted, or the path to the file would be incorrectly formatted for the operating system. For example, use- as Windows path separators: on Mac OS X, and Linux. Check that the path is correct using the command prompt or file Explorer. = OR-488: the non-existent GPIB interface.

Any help is appreciated.

Thank you.

Problem solved. I uninstalled the SDK Kinect (I think that's the important part) and .NET 4.0. Then reinstalled .NET 4.0 and the Kinect Beta SDK (not the most recent SDK of Kinect):

http://www.Microsoft.com/en-us/kinectforwindows/develop/beta.aspx

Everything works fine now. I had to go through the LabVIEW VIs and re - select a few .NET runtime calls, but everything works fine now.

Thanks for all the help.

-

User interface simple Question

I apologize in advance for the simplicity of this question is probably, but I can't seem to find a way to do it.

I want to show a label that is framed with a value that is justifield just so that the labels are all on the left and the values are all right on the left.

I tried:

HorizontalFieldManager row1 = new HorizontalFieldManager(); LabelField l1 = new LabelField("Linked: "); LabelField l2 = new LabelField( (theApp.getIsLinked()?"Yes":"No), Field.FIELD_RIGHT); row1.add(l1); row1.add(l2); add(row1);That did not work. I also tried a few other things but can't seem to make it work.

Thanks in advance.

Here you go:

HorizontalFieldManager Row1 = new HorizontalFieldManager();

LabelField l1 = new LabelField ("Linked:", LabelField.FIELD_LEFT);

LabelField l2 = new LabelField ("No.", DrawStyle.RIGHT |) LabelField.USE_ALL_WIDTH); -

Hello

I'm trying to fix a problem with After Effects CS6 that has appeared recently. The Comp Viewer seems to be rendered behind which sits the playhead of a picture. For example if I use PageUp and PageDown move forward and backward between frames, the frame that appears is the previous frame to that indicator sits to the timeline. As soon as I hit the previous or following once again it shows the frame which would have disclosed last.

Also if I use the mouse wheel to zoom in/out of the comp Viewer, it also accused a step behind, i.e. to zoom, nothing happens... Zoom again, zoom to the 1 step... To zoom out, zoom IN another step... To zoom out, zoom 1 step.

Everything works perfectly until I recently updated to Quicktime, Nivida pilots and adjusted some parameters for another program (Cubase) to work with the video. After that, I was unable to get After Effects works again. The strange thing is that I now properly installed Windows 7 and tried running AE at different stages (print drivers and version of QT), then updated everything (including all Adobe, graphics drivers, Quicktime products) and I have exactly the same problem on all points. CS6 is currently the only program on the computer.

I tested this problem with. R3D (Red camera) files with H264 'normal '. MP4 files. I also tried to use the files from an external drive. Exactly the same problems in all cases.

Data sheet:

Windows 7 64 bit

16 GB of RAM

2 x Nvidia Quadro FX1700

Help would be greatly appreciated that I can't find anyone else encounter this problem.

Thank you very much

Ben

SOLUTION:

I diagnosed the problem; It relates to the use of dual screen with two separate graphics cards. The problem can be tested for by race AE full-screen on one monitor, then the other. The question should be on one of the two screens. Once sent, I was able to run AE on each screen OR spanning the two without problem.

TO SOLVE:

After effects CLOSED, open Nivida Panel and select 'manage 3D settings '. Choose "Open GL made GPU" in the list of options and select 1 of the 2' or 2 of 2' but not 'Auto '. Apply the changes and the re - open After Effects.

I very much hope that that someone saves some time!

Ben

-

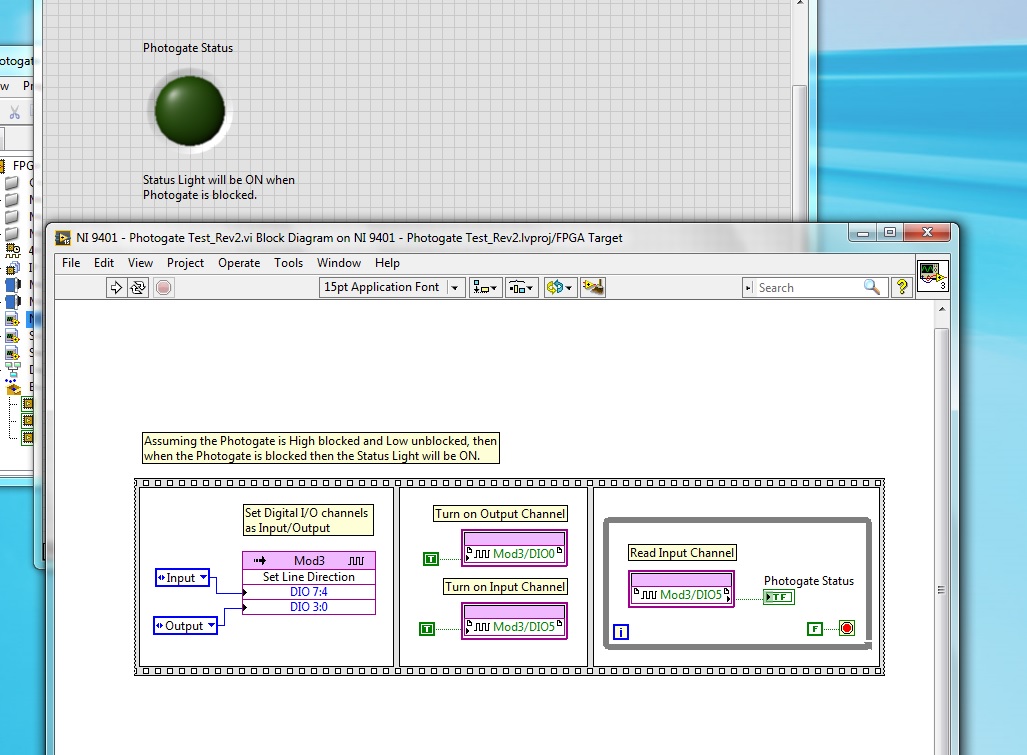

Playback of digital input [FPGA] - NI 9401 - questions?

I'm having some trouble with the digital input NI 9401, which is to have a uniform reading. I have a photogate that power of a digital output is turned off and goes in to a digital input module, but I can't read the entry several times. My LED flashes once and never again will blink until I restart my CRIO or recompile. I have launched the ports of entry and exit, their market and constantly for loop. Any idea what's going on?

Hi Allan,

Why you "light up" a channel of entry?

Writing a value to a DIO PIN is usually for outings!

What is connected to your PIN DIO 5? Have you checked the entry with a DMM measure?

How long the impulses are measured with this entry? Do you really you can see short pulses of light flashing?

Maybe you are looking for

-

Occurs on several sites. My banking site - when I go to my account and then try to click on print a Bank Reconciliation window flashes and then goes. My health care provider site - went there today and I tried to click on the "explanation of benefits

-

No sound from HP - 8560p, windows 7 64 bit elitebook docking station

I was issued a laptop Elitebook 8560p for use with a 90 W HP Docking station at work. When the laptop is plugged into the docking station, the port ' audio out ' of the docking station does not work. The sound continues to come out of the computer

-

I am using a microphone. When I whistle (a single frequency), I need to receive a value of true. Any suggestions

-

I have vista sp2, I have an update of XP, I also have Win 98, then I install XP and still have Vista? If I can't, I could just wipe the drive and just install XP, I try to get the old game ' keeper dungoen 1' work and I'm having NO luck with vista, a

-

Check the notification of space on my computer backup drive (Important)

My local disk C says that he is free to 78.8 GB only 9,00 GB. But the sum of the four individual record (by flogs (empty), program files (4.49 GB), users (26.7 GB) and Windows (18.4 GB)) is only 49.5 GB. My computer I check space (Important) shows wh