FPGA: Error of timing

Hi all

I have a problem with the compiler for FPGAS. When I try to compile the VI attached, it gives me an error of timing, which I can't understand. When compiling on a different computer, however, it works fine. The latest critical updates are installed, but the error message is him even without the updates.

Any help would be much appreciated!

Kind regards

kwalker

Hello

On the system that fails with the error of timing: what is the margin of error? In other words, what is the difference between maximum clock speed than the tools that your design could work in and the specified clock rate? If it's barely failing one, then it's probably barely passing on the other and this could be an indication that your design is marginal in terms of timing. If this is the case, you could try channeling the logic in your SCTLs to see if the timing error disappears. For example, it seems that you could put safely a knot of feedback between more than block and the last block selection without changing the behavior of your algo (just adding 1 cycle latency).

Kind regards

bcl511

Tags: NI Software

Similar Questions

-

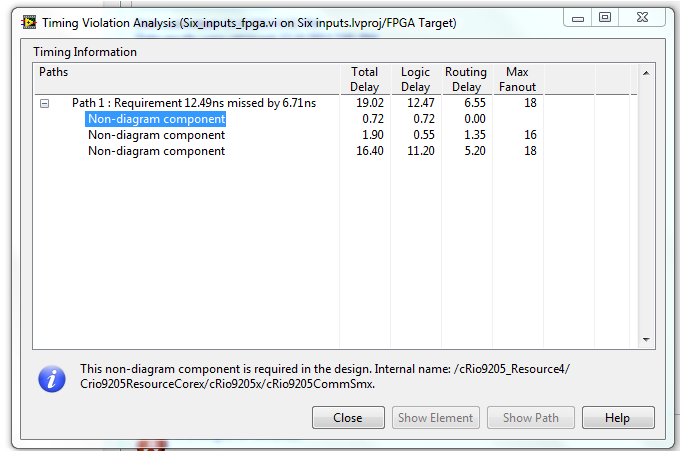

Error of timing in my fpga code

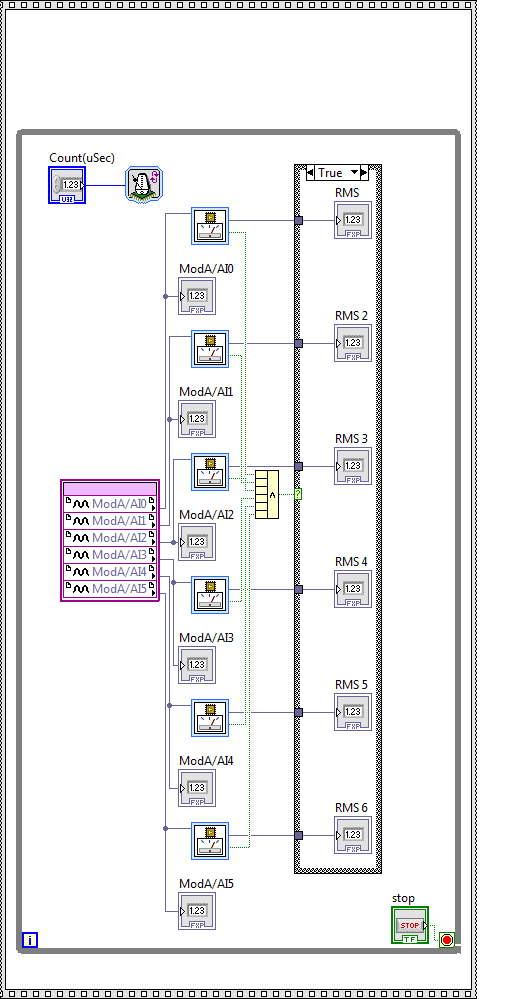

Hello everyone, I have attached an image with which basically indicates an error that I get when I compile my FPGA code. I am also attaching a photo of my code with it. I am a newbie in Labview FPGA and this code might not be effective way to achieve what I'm trying to accomplish. Basically what follows is the application.

I have a sbrio 9642 and I'm six analog inputs and I would get the effective value of these six signals to be as accurate as possible. The entries are pure sinusoids with a frequency of 60 HZ.

If anyone has questions about the code or demand, please post in this discussion. I will try to answer as soon as possible.

Kind regards

Kumar

-

Podcast Connect Error: Read timed out

Hi all

I am quite new to podcasting and has just published my first episode. Now, I submitted the podcast to itunes and got the "approved podcast" - message from last night. So my podcast is listed on itunes now and works absolutly fine.

But when I check on it to 'Podcasts Connect' I get an error message "connection to your feed was interrupted because of a connection timeout error. Read timed out ".

For your understanding: I use a host externally (www.podhost.de), which should be implemented for all data in the RSS feeds from http://headlock.podspot.de/rss.

When I downloaded the information, everything seemed to go well. Now I'm as stuck in the middle between labor and does not not :-)

Is just a matter of time, because the cast has gotten only approved? Check the iTunes on the RSS feed on a regular basis and as a result, this error can be temporarily?

Thanks for your help in advance, it is much appreciated!

I was able to susbcribe and check it into Podcasts Connect and http://castfeedvalidator.com/ without problems. A time-out would be the cause of your server is slow to respond, but you can just hit a temporary problem that can be anywhere in the internet connection between Apple and your server. As long as it works in iTunes when you subscribe, I shouldn't worry about this. Temporary hiccup in internet connections is very common.

-

FPGA: error message - Item not supported

Dear all,

I am a new user of Labview. I try to use OR 7855R. FPGA Module is installed on the computer, but when I try to run sample files, I get an error message that FPGA plugin is not installed or there is an expired license. But FPGA module is installed, two times to make sure that is not the problem, and I also have a license for the development of FPGA too.

Do you have an idea how to fix this? I'm stuck here for almost 10 days now!

Thanks in advance!

It's true. You should have received a disc or two for this with your copy of LabVIEW, if you have bought this module. It also appears you can download from http://www.ni.com/download/labview-fpga-module-2014/4827/en/ , but note that this is a large installation (I have not downloaded this file, I just know it's a great Installer off the discs).

-

I have an entry and exit FPGA running program on NOR 7831R. The output is used for a motor drive. When I click on shutdown, the following errors occurs:

LabVIEW FPGA: The operation could not be performed because the FPGA is busy. Stop all activity on the FPGA before asking this operation. What can cause this error?

-

FPGA error: failed to create the C Series module

I use sbRIO 9631 with LabVIEW 2012, as well as the FPGA 2012 module. Everything worked fine until yesterday, I got this error when creating a new FPGA project.

«LabVIEW FPGA: an error has occurred loading the VI on the FPGA device.» Check that the target is connected and powered and that the target resource is configured correctly.After ignoring this error, I can create any VI in the FPGA target, compile it and it works but can not do anything with host one. MAX configurations show so no error.

I have attached snapshots for convenience.Note: This sbRIO came with a DVD of LabVIEW 8.6 and similarly associated modules version. I had been using this version for a year. Then I got LabVIEW 2012 with the last modules and now facing this error.

Hi NapDynamite,

You should not need to uninstall your previous version of LabVIEW for the development of your PC.

You can see what version of NOR-RIO you have installed on your sbRIO? You can view it by selecting the sbRIO under "Remote Systems" of MAX, and then by selecting the category of software. You may need to update the version of NOR-RIO that is installed on the sbRIO.

You can try this first?

Kind regards

-

LabVIEW FPGA error - Urgent please

Hello

I had this problem for a while and it drives me crazy. When I try to program my 3rd Spartan fpga Board, I get a message, it compiles successfully. Then, I get an error indicating that

"Labview called another component of software and that componen returned ther following error:

Error code = - 2147483648

2147473648 error occurred at nilvcseInitChain.vi

This error is not defined. No one has provided a description for this code or you could have wired a number which is not an admission of error code error code. »

Help, please!

1. what version of LV run you, 8.5 or 8.6? What operating system do you use? XP, Vista (32/64-bit?)

2. go to the Device Manager (click right tab of my computer/hardware). You see a category called "Programming wires" and the Xilinx Board is listed under it?

Reid

-

Error of timing architecture producer/consumer

Hello

I use architecture of producer/consumer for the acquisition of measures of constraint by using several channels. Also, I am interested to write data all 1 minute given that the program should be run for a month. Currently, I get a 200279 error whenever I increase the time of 10 sec. To control the execution of the loop of producer, I use 'weight up to the next multiple ms' function. According to the error message, I tried to fix the samples to read without increasing the frequency of data acquisition, but I still get the same error.

Thank you

Piyush

Your test3.vi was not included, so we do not know what is happening there.

What is the rate of acquisition for your data acquisition task? DAQ hardware do you use?

Have you tried to increase the size of the buffer? There is a property node that can define it.

-

FPGA timing when compiling PID loop error

Hello.

I'm using Labview 2011 card FPGA PCI-7833R.

My problem is that whenever I try to integrate FPGA designed screws in my code, I get an error of timing. See the photos displayed below.

In this case, I have an express VI PID which I use in a used while loop (not even timed!) in my FPGA code, but when compiling, I get an error saying that the possible maximum clock frequency is the 43 MHz.

I have a lot of loops, a few running at 80 MHz. Is there a way to slow down a specific while loop, so that it runs at 40 MHz and not 80 MHz, as others? The compiler does not seem to meet the simple addition of a timer loop...

Thank you

Orel.

PS the same thing happens when I try to add a lowpass filter VI of the FPGA code.

Is it possible that you set the level above 80 Mhz clock? This is what it looks like to me. In Explorer, right click on the FPGA target, select Properties, then go to the category "first level clock.

-

Violation of compilation-Timing error FPGA

Hi all

I've been LV around for years, but I am a complete newbie when it comes to FPGA. I'm working on programming for a 9651 (SOM) using the Dev kit. I'm starting by small steps, but already tripped. I have a simple VI which retrieves a value from a FIFO and passes it réécrirait a different FIFO. When compiling, it gives an error of timing violation, and I don't know how to study. The VI is attached.

If background for the curious... I'm working on the side of our application to signal processing. I'm passing data from a prerecorded TDMS file to a FIFO. I want to send the FPGA, treat it and send it back. Eventually, it will come of I/O, but for now, I just want to work on the processing of the signal. Before starting work, I thought I'd just make sure I can transfer data to the bottom and back. Once I get this job, I'll start to developing processing screw for between the two.

Thank you!

Hi thutch79,

You can specify the version of LabVIEW you use and implementing CLIP half bridge that you use for the IO DevKit?

It was a timing violation introduced between LabVIEW 2014 and 2015, given the way the compiler Xilinx handled VHDL which takes in charge the second port Ethernet on SOM. If you use a CLIP half bridge that has been generated before 2015 LabVIEW (as the example of the expedition which I think begins with a CLIP called "DevKit"), then you can get a timing error. There should be a second sample CLIP called DevKit2, I think, which was regenerated with compatibility for 2015 of LabVIEW and later versions.

This problem has been discussed here: https://decibel.ni.com/content/thread/42711

You can check your half-bridge CLIP in the project by ensuring that you have selected the version called DevKit2 if you have a version of LabVIEW FPGA which is 2015 or newer.

Kind regards

-

GPS Timed Out error when querying location

Hi all

I worked with GPS and maps on BlackBerry OS 5.0 and it has been frustrating to say the least. I have everything working, however I get an error 'GPS timed' out whenever I try to question my location. I get this error on a real device, and not on the Simulator. This happens for a MapField both the native BlackBerry map.

Essentially, what I'm doing is looking for the current coordinates via GPS, translating these coordinates in an address through reverseGeocoding (a separate thread) and then using that zip code to find and locate a web service. The web service to function properly, it is the GPS which is the problem.

I'd appreciate it if someone could take a look at my code and see if something comes out. Here's my LocationHandler (implementation of LocationListener):

import javax.microedition.location.Criteria; import javax.microedition.location.Location; import javax.microedition.location.LocationException; import javax.microedition.location.LocationListener; import javax.microedition.location.LocationProvider; import javax.microedition.location.QualifiedCoordinates; import com.usps.mobile.blackberry.Constants; import com.usps.mobile.blackberry.Inform; import com.usps.mobile.blackberry.interfaces.ScreenLocation; public class LocationHandler extends Thread implements LocationListener { private ScreenLocation screen; private boolean periodicUpdates; public LocationHandler(ScreenLocation screen, boolean update) { this.screen = screen; this.periodicUpdates = update; } public void locationUpdated(LocationProvider provider, Location location) { QualifiedCoordinates qualifiedCoordinates = location .getQualifiedCoordinates(); int longitude = (int) (qualifiedCoordinates.getLongitude() * 1000000); int latitude = (int) (qualifiedCoordinates.getLatitude() * 1000000); new myReverseGeocode(longitude, latitude, screen); } public void providerStateChanged(LocationProvider provider, int newState) { // So far, nothing for this } /** * The thread */ public void run() { Criteria criteria = new Criteria(); criteria.setVerticalAccuracy(Constants.DEFAULT_VERTICAL_ACCURACY); criteria.setHorizontalAccuracy(Constants.DEFAULT_HORIZONTAL_ACCURACY); criteria.setCostAllowed(true); criteria .setPreferredPowerConsumption(Constants.DEFAULT_GPS_POWER_CONSUMPTION); try { LocationProvider provider = LocationProvider.getInstance(criteria); Location location = provider.getLocation(-1); locationUpdated(provider, location); if (periodicUpdates) { // Update every 1 minute provider.setLocationListener(this, 60, -1, 10); } } catch (final LocationException e) { Inform.inform(e.getMessage()); screen.setLocation(Constants.DEFAULT_LONGITUDE, Constants.DEFAULT_LATITUDE); } catch (final InterruptedException e) { Inform.inform(e.getMessage()); screen.setLocation(Constants.DEFAULT_LONGITUDE, Constants.DEFAULT_LATITUDE); } } }Method setLocation in my main screen:

public void setLocation(int longitude, int latitude, AddressInfo addrInfo) { synchronized (UiApplication.getEventLock()) { mapField.moveTo(latitude, longitude); mapField.setZoom(Math.max(mapField.getZoom() - 1, mapField .getMinZoom())); doWebService(addrInfo.getField(AddressInfo.POSTAL_CODE)); } }As I said, reverseGeocode() is on its own thread, and it's back a correct information.

Thank you!

On verizon.

You will not be able to be assisted without access PDE. The criteria that you have shown, is not mapped to stand alone.

Autonomous may take some time to get and quite well must have a clear view of the sky for correct performance.

-

FPGA: update w / 14,4, fails w / Vivado 2013.4

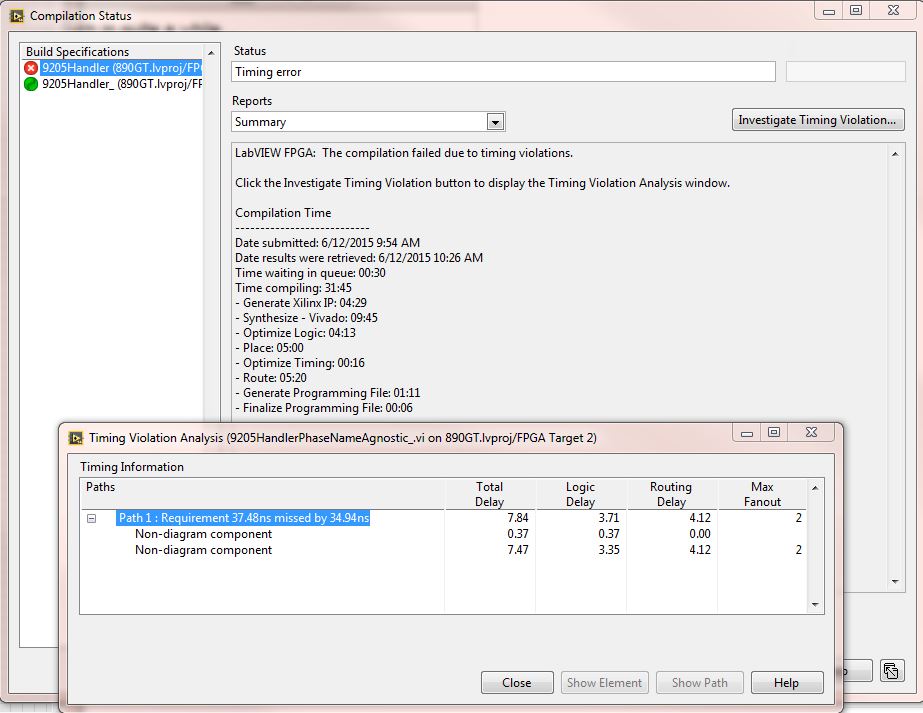

My FPGA code that compiled fine in LV 2011, then 2013 LV (using Xilinx 14.4). I didn't contact for some time...

The upgrade to SP1 2014 LV, I believe that I have to re - compile to get the bit file to run on the target of the cRIO. However, now it does not compile. Cloud compiler error of timing. Clouds (local and compiler and elsewhere) report using Vivado 2013.4

The code handles a moudle of analog input of series C 9205. 6 of the 32 channels are run by a calculation of RMS. A time loop is set to do this each 185 uSec (9205 card channels = minimum update 4uSec * 32 channels = 128uS = maximum theoretical to run the FPGA and to obtain valid data). Each value of 650 samples a new RMS is calculated.

The rest of the channels get on average, 8 samples are averaged every 100th iteration of the loop above.

The timing of the loop is a front panel control. I tried this increasing by 185 to 200 uSec, but it does not help. All inputs and outputs to the FPGA VI are written in / reading of the *(cRIO-9068) of host real time be using the controls on the front panel.

This code has not changed in a very long time. I could share it if it helps.

My questions around the investigate Center window timing results. Here, nothing seems useful. What is "path 1' and how is it related to the block diagram? View items and path are inhibited. I have tried to change the build - optimize the performance and optimize for area etc... but the compilation always fails.

I will create a ticket with NEITHER. But thought pehaps someone here might have additional guidance.

For applications using hybrid...

(1) update install to 14.5 CompactRIO: C Series Module Support 14.6

(2) change of generation to optimize performance

-

LabVIEW FPGA Module 2015 Compilation to PXIe7820 with 'no timetable '.

I did a first compilation for the SMU with the Xilinx Vivado 2014.4 tool 7820 (64-bit). Compilation report said.

Compilation successfully completed.

Use of the device

---------------------------

Total bands: 19.1% (25350 4848)

Records of slice: 6.9% (13937 on 202800)

Slice lUTs: 12.3% (101400 12430)

Block of Rams: 0.9% (3 out of 325)

DSP48s: 6.2% (37 out of 600)Calendar

---------------------------

None.Compile time

---------------------------

Introduction date: 16.07.2016 12:48

Date recovered results: 16.07.2016 12:59

Waiting time in the queue: 00:08

Compilation of time: 10:16

-Generate a Xilinx IP: 00:00

-Summarize - Vivado: 04:18

-Optimize the logic: 00:14

-Place: 01:17

-Optimize the Timing: 00:18

-Road: 03:04

"- Generate the programming file: 00:56.This means no timetable? The embedded clock's 40 MHz. It runs with this clock? Beacause 7833 compilations for the pci or pcie 7842 report displays the maximum clock time.

Hello

"none" means simply from what I can understand, that there is no violation of timing. The source of synchronization that will be used is (as you have already suspected it) on-board 40 MHz clock.

As to why you don't get a mention of the MiteClk and the ReliableClk in summary, I think that it is due the 7833 and the 7842 relying on FPGA Virtex-II and Virtex-5, while the 7820 uses the Kintex-7 family. Depending on what type FPGA using different estimates regarding the use of the device and synchronization are not always available.

As I said, as long as you don't get not an error of timing and your compilation is completed successfully, you should be fine.

Kind regards

Alex

-

CLIQ: Signature error into account demand for the timeout of waiting for an answer.

I need help! I'm trying to enter my motorola cliq and have some difficulty to get past motoblur... I did a master reset on the phone two times so I know it isn't the issue... I know that my motoblur account info it correct... Whenever I put in my info an error msg showing... What can I do to use my phone someone help please...!

If your out a timed mistake you're on 3G or wifi to connect to fade. During the installation of blur if necessary to turn on the wifi, press menu and configure your wifi to activate it. If this isn't your problem please indicate what you get the error. Timed out error is the most common.

-

Instant incorrect error messages

I get messages like this from time to time for our regular shots on a PS6000:

[ID: 4.18] Annex 4 hour for mesa volume less than expected clichés. Planned 8, but the volume has only 0.

But when I check the Group Manager, the right number of snapshots exist and I have no problem, create a new. The error is generally somewhat random and usually happens for one of two specific LUNS. In addition, it detects less than expected (such as 5 instead of 8). This morning, a single message listed 5 different LUN and says that everything has zero snapshots. I checked each LUN, and all had the right number of snapshots.

He expects the last update of the firmware, but it is not very far exceeded. This has happened for at least a year, so I've mostly been ignore it since the problem seems to be cosmetic. Is there anything else I need to check?

Hello

These part of a collection? I have seen where an error of timing at the time of the creation, which causes this error when they are part of a collection.

Kind regards

Maybe you are looking for

-

I have big problems with Firefox and if I reset it. Now, I seem to have lost all my plugin and I can't figure out how to restore them or how to reinstall them. Help, please. I am lost without anti-ad and the magnifying glass text Plugins.

-

Qosmio X 770-13 G - slow Internet access

Hi all I just purchased a Qosmio X 770-13 G with Windows 7.WIRELESS data transfer is very slow, even using a high speed AP (tried on several locations) and after you disable the anti-virus program. Using the Config Free Watch 6Mbps program second dow

-

Where are stored e-mail messages Toshiba Windows 7?

I have a Toshiba L650 with Windows 7 Home Premium 64-bit and Windows Live Mail. Despite trying all types of repair of Toshiba, can't do Windows and so my computer at startup (I think I downloaded a virus). I intend to transfer data to a memory stick,

-

Try to install the fax component in XP home. However, when the installation program asks for the location of the SP3 CD-ROM (as it seems a fxs file * folder i386) will not accept the ISO burned I (on disc L) which is functional because I used to inst

-

My weather of Windows 7 gadget on my desktop has changed color

After you install Internet Explorer 11 via Windows Update, I rebooted the computer and my weather gadget had turned pink and fuzzy. I did something wrong? Any help would be good. Jimmy