Error of timing in my fpga code

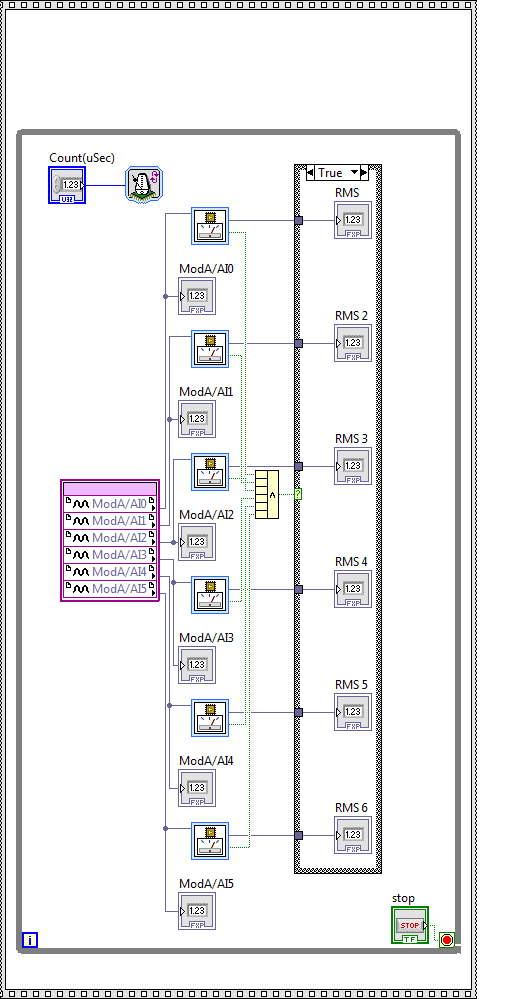

Hello everyone, I have attached an image with which basically indicates an error that I get when I compile my FPGA code. I am also attaching a photo of my code with it. I am a newbie in Labview FPGA and this code might not be effective way to achieve what I'm trying to accomplish. Basically what follows is the application.

I have a sbrio 9642 and I'm six analog inputs and I would get the effective value of these six signals to be as accurate as possible. The entries are pure sinusoids with a frequency of 60 HZ.

If anyone has questions about the code or demand, please post in this discussion. I will try to answer as soon as possible.

Kind regards

Kumar

Tags: NI Software

Similar Questions

-

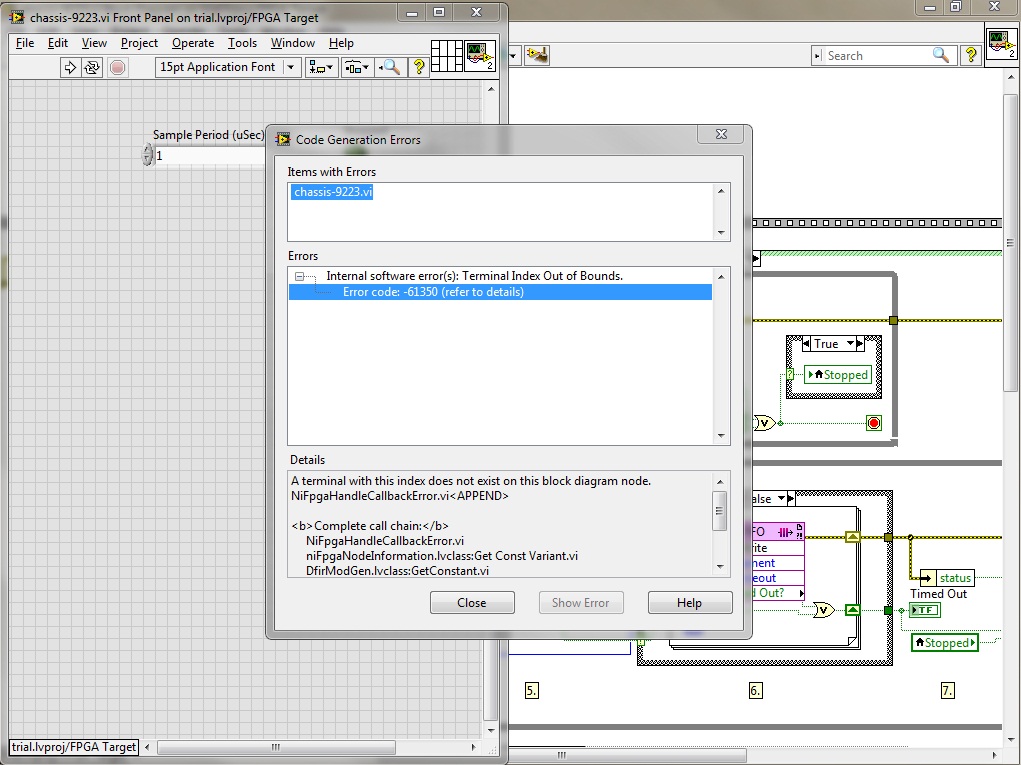

I get the error (in a popup window) when my VI FPGA code in chassis 9118 OR NI 9223 module compiled help. This error occurs when compiling the process (generating intermediate files, scene 7 of 7). How to solve this error?

Thank you

additional information:

Original error message:

-------------------------Errors:

Software (s) internal error: Terminal Index out of Bounds.

:-61350 error code

Details:

A terminal with this index does not exist on this block diagram node.

NiFpgaHandleCallbackError.vi«"" "String of full appeal:»»"»

NiFpgaHandleCallbackError.vi

niFpgaNodeInformation.lvclass:Get Const Variant.vi

DfirModGen.lvclass:GetConstant.vi

niLvFpgaMungerBrainwashIONodeCommon_Dfir.vi

niLvFpgaMungerBrainwashSingleIOGrowableMethod_DFIR.vi

nirviEIOMethodImplementation_SpecifyDFIR.vi

nirviEIOMethodImplementation_SpecifyDFIR.vi.ProxyCallerHi tesa,.

This is a bug that has been fixed in LabVIEW 2012 SP1. The number of CAR created for this bug is 332811 and as you can see in this link, it is already in the list of bug fixes.

Carmen C.

-

Hi all

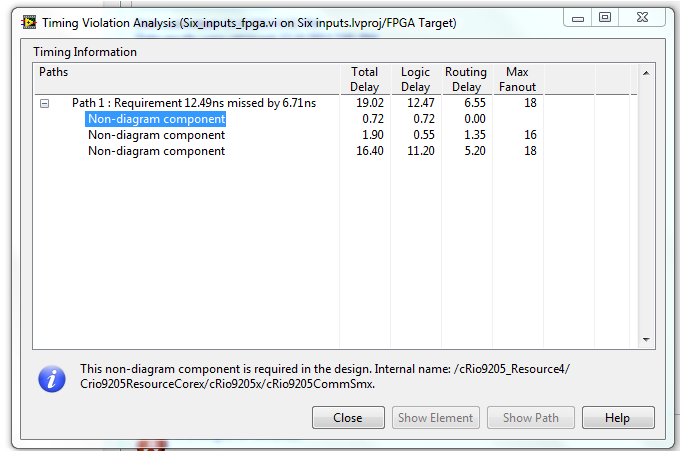

I have a problem with the compiler for FPGAS. When I try to compile the VI attached, it gives me an error of timing, which I can't understand. When compiling on a different computer, however, it works fine. The latest critical updates are installed, but the error message is him even without the updates.

Any help would be much appreciated!

Kind regards

kwalker

Hello

On the system that fails with the error of timing: what is the margin of error? In other words, what is the difference between maximum clock speed than the tools that your design could work in and the specified clock rate? If it's barely failing one, then it's probably barely passing on the other and this could be an indication that your design is marginal in terms of timing. If this is the case, you could try channeling the logic in your SCTLs to see if the timing error disappears. For example, it seems that you could put safely a knot of feedback between more than block and the last block selection without changing the behavior of your algo (just adding 1 cycle latency).

Kind regards

bcl511

-

ERROR: TclTasksC:process_077: in the FPGA Compilation

Hi all

I use for my application in which I am facing following error when compiling my fpga code compact rio 9072:

Compilation failed due to an error of Xilinx.

Details:

ERROR: TclTasksC rocess_077: did not finish. Please, look in the newspaper and report files.false

rocess_077: did not finish. Please, look in the newspaper and report files.false

When running

"process run"card.

(file "C:\NIFPGA\jobs\XI64xG6_My449tj\map.tcl" line 6)ERROR

ack:2310 - type compositions "SLICEL" too found to adapt to this device.

ack:2310 - type compositions "SLICEL" too found to adapt to this device.

ERROR ack:18 - the design is too large for the device and package.

ack:18 - the design is too large for the device and package.

Please see the Design summary section to see the cost estimates for

your design exceeds the resources available in the device.

NOTE: A file NCD will be always generated to allow you to examine the mapped

Design. This file is intended for assessment use only and will not be processed

successfully through NOMINAL.

This NCD mapped file can be used to assess how the logic of the design has been

mapped in FPGA logic resources. It can also be used to analyze

preliminary to the level logic (route pre) calendar with one of the static electricity of Xilinx

analysis of synchronization (PRHT or Timing Analyzer) tools.

Summary of the design:

Error number: 2

Number of warnings: 69

Use of logic:

Number of slice Flip Flops: 7 886 on 15 360 51%

Number of 4-input lut: 16 104 on 15 360 104% (OVERMAPPED)

Distribution of logic:

Number of slots occupied: 8 744 7 680 113% (OVERMAPPED)

Number of slices only related logical container: 8 744 100% 8 744

Number of slices that contains no logical relationship: 0 to 8 744 0%

* See NOTES below for an explanation of the effects of unrelated logic.

Total number of 4 input lut: 17 400 on 15 360 113% (OVERMAPPED)

Number used as logic: 15 998

Number used as a middle way: 1 296

Number used as Rams 16 x 1: 82

Used number recorded the shift: 24

The logical Distribution report slice is not significant if the design is

too mapped to a resource not slices or if Placement fails.

Number of IOBs servile: 183 on 333 54%

BIO flip flops: 74

Number of RAMB16s: 1 24 4%

Number of MULT18X18s: 2 on 24 8%

Number of BUFGMUXs: 4 to 8 50%

Number of DCMs: 1 on 4 25%

Fanout of the Non-horloge nets on average: 3.38

Peak Memory use: 361 MB

Total in time REAL in the completion of the card: 1 dry 12 mins

Time CPU until the end of the total map: 1 dry 12 mins

NOTES:

Related logic is defined as logical that share connectivity - for example two

Lut are "related" if they share common inputs. During Assembly of the slices.

Card gives priority to combine the logic that is related. Generates so

best performance of synchronization.

Without logical report does share no connectivity. Card will start only packing

logic not related in a slice once that 99% of the slices are held through

logical packaging partners.

Note that once the logical distribution reaches the level of 99% by related

logical packaging, this does not mean the device is completely used.

No logical report package will begin, continuing until all usable LUTs

and FFs are busy. According to your timing budget, an increase in the concentrations of

logical packaging unrelated can adversely affect the performance of timing set

your design.

Mapping performed.

See the report of map file "toplevel_gen_map.mrp" for more details.

Problem encountered during the packaging phase.

Failure of the process 'Map '.Start time: 18:29:23

End time: 18:44:42

Total time: 00:15:19Can someone tell me why this error came?

Thank you best regards &,.

Vipin Ahuja

Vipin Hello,

It seems that your code requires more resources that are available on the FPGA. Optimizing your code can help to solve your problem:

You may have noticed some "Overmapping", mentioned in the newspaper:

Number of 4-input lut: 16 104 on 15 360 104% (OVERMAPPED)

Distribution of logic:

Number of slots occupied: 8 744 7 680 113% (OVERMAPPED)Take a look at this article:

http://digital.NI.com/public.nsf/allkb/060BA89FE3A0119E48256E850048FFFE?OpenDocument

And this:

http://digital.NI.com/public.nsf/WebSearch/311C18E2D635FA338625714700664816?OpenDocument

Kind regards

Navjodh

National Instruments

-

FPGA code with the evolution of the modules

I need to create FPGA code to a cRIO-9072 facing the development of the modules.

My cRIO will have a number any NI 9203 (analog acquisition) and modules OR 9411 (acquisition digital) as inserted by the operator. When turning the power on, the system must identify two possible modules were inserted in each of the slots. Subsequently, he will then know what choices of code to call to acquire data from the individual modules.

I found the article in the knowledge base for CRY that queries each module and again reports the type of module and I can use it to successfully detect modules, but what LabVIEW fails to allow me to do this is to compile my FPGA code that was designed to deal with possible modules. After compiling, I get the error: "IO found point FPGA project. You must add the I/O item in the Project Explorer window, or select a different element in the control of FPGA of IO or the constant"because the compiler requires the appropriate modules are configured in the LabVIEW project. Unfortunately, this would require two different modules to be configured for each slot at the same time as there are sections of code for the 9203 modules and sections for 9411 modules for all eight locations coexist in a vi.

Anyone have any ideas on how to get LabVIEW to compile my FPGA code somehow?

Many thanks in advance,

With the current draft of LabVIEW FPGA, you cannot compile a LabVIEW FPGA VI which manages several configurations of C Series modules.

For your application, you must create a target of your project for each of the possible configurations of module and build the corresponding FPGA VI. Then, compile each of the screws to create the necessary for each configuration FPGA bitstream. Then in your host VI, you can detect what the current configuration of the module and download the binary stream appropriate for the FPGA. Another issue to consider is that the reference to the FPGA VI/bitstream returned by the open FPGA VI reference function will be unique to each bitstream/module configuration. So in your host VI, you'll need treat each configuration of the module with a separate set of code by contacting the FPGA.

If you consider only two different modules and an eight slot chassis, there are 9 modules possible combinations. The condition would be to the end user to place all modules of the same type together, either from the left or the right side of the chassis.

-

The create a System Image will save the FPGA code and the RT code?

I have some cRIO systems which were broadcast in our manufacturing plant for some time. A slight problem has been discovered in the programming and created a workaround solution, but a fix should be implemented. Currently, I have no way to test my new code without loading on the cRIO and it works on the tool while the product is running. If there is a problem and I need to do some debugging, the tool cannot be down for an extended period. I would write a vi that will save an image of the cRIO so I can reload the software that is currently running and prevent a situation of prolonged downtime.

My question is, when I did in the past with a product that has different tests, calibration and the final client software RT, it seems that the code FPGA not be saved (not a big deal at the time since the new FPGA code was compatible with different deployments RT). The new FPGA code won't be compatible with the old RT software, so now I'm worried. I would like to just check on it until I have all the boss breathing down my neck. If the service will not save the bitfile FPGA, is there anything else I can do for the tool to return to the previous running state while I solved problems that may exist with the new code review? The original code was lost by my predecessor. Otherwise, I would use just that.

Hi Jeremy,.

You are right, because the create a System Image does not record the bitfile with the image of the RT. Using the configuration system API, you will need to deploy the RT image and then the bitfile FPGA compiled later. To ensure that you can return to the previous version of the software running on your RIOs, you could simply save the current image and bitfile before deploying the new image and bitfile.

However, the best way to proceed is to use replication Deployment Utility (RAD of OR). I have provided the link to the tutorial on the wheel, where you can download the utility. This exe will make images of the any of your RT targets and will also include the bitfiles with them. You can also deploy these images to several targets at once. In particular, you can read about the Bitfile (s) configure for FPGA Deployment Flash; the bitfile will be deployed at the start when stored in flash memory.

Replication and deployment (RAD) utility-

-

Hello

I'm working on 802.11 application, I tried to change the FPGA code.

I really need to compile all the code after changes? or just save the VI to observe the effects of the change.

Yes, LabVIEW code must be compiled using the FPGA Toolbox after you make all the changes. I think the only exception is when you run mode simulated on your PC.

-

Hi all

I have a pretty "urgent" problem here:

I wrote a FPGA code, I tested for a loop of 1 kHz with success rate before an important week of laboratory. Now I discovered that I need to increase up to 5 kHz sampling, however, I notice that my FPGA code can run that fast.

As I am not this experience in FPGA, can someone give an indication on how to speed up the code?

Thanks to you all.

-

FPGA code will stop when the code RT

I developed a FPGA code to manage a piece of hardware. It's the installer to read some default Panel control configuration values and then sit there constantly respond to signals input and output signal. The bitfile FPGA is written in flash to load FPGA memory and starts almost immediately. So far, everything is good.

Then I layered on the code of RT (cRIO-9075) system that opens a reference FPGA to the FPGA façade and allows me to follow a few indicators and change configuration settings and cause the configuration settings is changed be used by the FPGA. So far, it seems to work too when I run the RT code interactively (eventually there will be an interface for a host system).

The problem occurs when the code RT is ordered to stop. If you stop the RT code also, the judgment of the FPGA code and I will not stop the FPGA code. The RT code does not all calls to order the FPGA code to stop execution. When the RT code is stopped, the only thing she does in regards the link to the FPGA is to close the reference FPGA VI which was opened when the RT code was started.

What should I do to cause the code FPGA to continue to operate as the RT code is started and stopped?

I have to wait that I return to the office tomorrow to test this, but I think that this link has the answer to my problem.

http://lavag.org/topic/16412-confusion-regarding-FPGA-Deployment/#entry100294

It is said: "close FPGA VI reference. If you right click you have an option to close or by default close and reset. This means the VI FPGA is reset (read aborted in standard LV talking) when we close the reference. »

-

I have the following code in the FPGA (didn't integrate the png because it is too big. You will have to click on the attachment below) and I noticed a bottleneck in the FIFO, when both running on the FPGA and jusing simulating values in the Dev Enviroment. Here are the values of control

Sampling frequency - 1 ms

Btwn samples - 1000 ms delay

NB of static samples - 10

I know that my conversion fxp is lousy right now and I will correct this, but I know that's not the issue. The question is in my FIFO because when I disable it everything works correctly. See the following questions which I will describe here is what I notice when I do not disable the part of the diagram:

Running in the Dev Environment:

Code works very well... for a while. If I look at the indicator loop counter it goes fast (about 1ms as programmed to do) of 0 to 9, then breaks for 1000 ms wait and then goes again. After about 20 all iterations of the loop, the for loop suddenly slows down way. I can see this because if I look at the counter of the loop, it starts to increment once every 5 seconds. I thought, well maybe the FIFO DMA reaches its limit, but is it not fixed? Old data should not only be overwritten? Is not delay because the delay indicator will never true so I have no idea whats going on.

Running on FPGA:

Never the time to fast as iteration above. From the outset, will slow down. I noticed this, because my side of RT, I have a dedicated loop to only read items in FIFO (see below). I put it to the top to read 340 items both (34 samples of table x 10 element). It takes forever for the FIFO reach 340 items (it should take only 10 ms). Because I have 1000 ms pause between entering the data there is no reason that my buffer should be overflowing.

Suggestions? Sorry, I cannot post my RT code, but may be able to view the FPGA code if it is really necessary.

Found the problem. The RTD I use by default in mode 'accuracy '. These RTD also do not have simultaneous sampling (NI 9217). In fine mode, the conversion time is set to 200 Ms. which explains why when I bench marked it took 800 ms to run one to the loop iteration (200 ms/Channel * 4 channels).

To fix this, go to your project, click with the right button on any given RTD, choose Properties, change the conversion time of 2.5 ms.

-

So I'm currently write code that will run on a cRIO (the processor in real-time and FPGA). Is there a way that I can run on my computer without be hung to the material? I do not have easy access to the material and would really like to test the behavior of my code.

Thank you.

Hello

You can create a cRIO in your LV project without having the hardware, you can compile the FPGA code and run in simulation mode too, but you cannot run the code of RT.

Christian

-

I have a Hp laptop, 2000 but I neeed to access the bios and I do not know the password the error I get is the following code.

85280672

Help

Hello

Come in:

30188274

-

Cannot access the he DVD drive in Windows Vista. Error: This device cannot start. (Code 10)

All of a sudden my DVD drive has stopped working. Windows Vista SP2 doesn't see it, but I can see it in the BIOS.

Error: This device cannot start. (Code 10)

The driver has the exclamation point. I uninstalled the driver and restarted the PC, but the system does not re - install.

The exclamation point is up there.Help, please

Thank you

Hello

This article can help...

http://support.Microsoft.com/kb/314060

Tricky

-

Windows Update, error! Impossible to update. Code Code 8007045 D 80071 has 91

Original title: Windows Update, error! Impossible to update.

I have try the update to have a better PC but it won't allow me because of an error.

There are 2 errors in fact, which areCode Code 8007045 D 80071 has 91All 23 updates have an error which are these codes. Help, please!I have a 32-bit and I have NO SERVICE PACK! This is the reason why Im trying to get the update!

I also use Norton 360, the firewall is enabled.I have a Windows Vista Home Premiumhttp://oi39.Tinypic.com/20qyo2d.jpg

That link above is the number of KB of all the im trying to install updates.

Hello

1. What are the exact error messages?

2 have you made changes on the computer before this problem?The following articles may be useful:

Error message when you try to install a Windows Update, a hotfix or a service pack after completing the system restore in Windows Vista: "0x80071A91".

http://support.Microsoft.com/kb/948252

Problems with installing updates

http://Windows.Microsoft.com/en-us/Windows-Vista/troubleshoot-problems-with-installing-updates

How to reset the Windows Update components?

http://support.Microsoft.com/kb/971058 -

Error 80070020 and 80070490 Windows upgrade codes

I tried to update windows and cannot install updates I got these error code 80070020 and 80070490 how can I fix this problem and get the updates to install?

CATFISH

You receive error 0 x 80070020 when you use the Windows Update Web site or the Microsoft Update Web site to install the updates

http://support.Microsoft.com/kb/883825and

0 X 80070490 - ERROR_NOT_FOUND

Corrupted system file; You will need to perform an upgrade on the spot or reinstalling the operating system.The error you receive occurs if there is corruption in the manifest of component maintenance base.

Ignore the title: the "Windows features" dialog box is empty in Windows 7 or Windows Vista, or you receive an error message that includes the following code when you try to use Windows Update: "0 x 80073712".

http://support.Microsoft.com/kb/931712

"Explains the SFC / Scannow.See also: how to use the System File Checker tool to fix the system files missing or corrupted on Windows Vista or Windows 7

http://support.Microsoft.com/kb/929833A repair install is the usual solution of SFC/scannow does not work.

However, a repair (AKA In-Place Upgrade) installation will be not solve the problem if it is due to a hijackware infection.You receive an error code "0 x 80070490" when you use Microsoft Update or Windows Update Web sites to install updates

http://support.Microsoft.com/kb/958044NB: If you have installed SP1 or SP2 for Vista

Step 7 (method for Windows Vista), the * UPGRADE option is not available because Service Pack/s are installed and that your operating system is newer than the system you are trying to reinstall, so service pack/s must be removed in this case.

Uninstall the Service Pack/s: How to uninstall Windows Vista service packs as a troubleshooting step

http://support.Microsoft.com/kb/948537See also:

How to overcome error 0 x 80070490 when installing updates in Windows Vista/Server 2008

http://blogs.msdn.com/andrekl/archive/2008/09/29/how-to-overcome-error-0x80070490-when-installing-updates-in-Windows-Vista-Server-2008.aspx

Maybe you are looking for

-

9.3 IOS safari and Mail links do not work

I updated my IPhone 6 to IOS 9.3 and links in Safari and Mail now no longer work. I press/touch them and nothing happens. Google chrome and other e-mail applications don't work well, but not Safari and Mail, those that I use the most.

-

I went to put in a cd to look and he wanted to get on-screen computor Ive seen it before, but for some reason any it stoped working. I went on a local drive Q and click with the right button to open it, but then it reads that q:\ is not accessible. a

-

I recently received a phone call from someone who said they were by Microsoft and that my computer was in danger from malicious software, etc. He stressed that he had nothing to do with viruses, etc.. He asked me to connect to my computer and then

-

Microsoft Office XP and Windows 8.1

My old faithful office went to heaven PC so I need but a new. I wonder if my copy of Office XP Pro 2002 version runs on Windows 8.1? The compatibility chart is a bit confusing, it says that my version compatible but then underneath said some programs

-

How to add data to a write-protected micro SD memory card

original title: write protected disk my removable disk (f :)) is write-protected, so I can't put music on my micro SD memory card, how do I remove this then I'll be able to transfer my music from my android phone?)