LabVIEW FPGA Module 2015 Compilation to PXIe7820 with 'no timetable '.

I did a first compilation for the SMU with the Xilinx Vivado 2014.4 tool 7820 (64-bit). Compilation report said.

Compilation successfully completed.

Use of the device

---------------------------

Total bands: 19.1% (25350 4848)

Records of slice: 6.9% (13937 on 202800)

Slice lUTs: 12.3% (101400 12430)

Block of Rams: 0.9% (3 out of 325)

DSP48s: 6.2% (37 out of 600)

Calendar

---------------------------

None.

Compile time

---------------------------

Introduction date: 16.07.2016 12:48

Date recovered results: 16.07.2016 12:59

Waiting time in the queue: 00:08

Compilation of time: 10:16

-Generate a Xilinx IP: 00:00

-Summarize - Vivado: 04:18

-Optimize the logic: 00:14

-Place: 01:17

-Optimize the Timing: 00:18

-Road: 03:04

"- Generate the programming file: 00:56.

This means no timetable? The embedded clock's 40 MHz. It runs with this clock? Beacause 7833 compilations for the pci or pcie 7842 report displays the maximum clock time.

Hello

"none" means simply from what I can understand, that there is no violation of timing. The source of synchronization that will be used is (as you have already suspected it) on-board 40 MHz clock.

As to why you don't get a mention of the MiteClk and the ReliableClk in summary, I think that it is due the 7833 and the 7842 relying on FPGA Virtex-II and Virtex-5, while the 7820 uses the Kintex-7 family. Depending on what type FPGA using different estimates regarding the use of the device and synchronization are not always available.

As I said, as long as you don't get not an error of timing and your compilation is completed successfully, you should be fine.

Kind regards

Alex

Tags: NI Software

Similar Questions

-

Internal software error of LabVIEW FPGA Module - 61499

I get the error next (in a pop-up window) in the phase of sompilation for the FPGA target with a vhdl IP. This error continues to occur even after restart LabVIEW and the PC. Someone at - it solved is this kind of problem before without having to re - install the software?

Here is the error information:

Error-61499 occurred at niFpgaXml_GetValue_String.vi<><><><>

Possible reasons:

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has occurred. Please contact National Instruments technical support on ni.com/support.

Additional information: lack the tag required XML (/ CompileServerList)

As a first step, I can compile the vhdl IP node successfully. However, once when I'm running a VI with the FPGA, the bureau stop working. After that I restarted by force, it cannot perform the build of a vhdl IP node. Even without connecing to the jury of LabView, he pointed out errors before the end of the sompilation.

Interestingly, the screw which also includes nodes IP vhdl that I properly compiled before, I can still run the VI to the Commission and it works correctly.

Thank you

Looks like your ActiveJobsList somehow has been corrupted. I saw occur when computers are hard stop or blue screen during compilation. I don't have that LabVIEW 2014 installed on my machine, so your path will be a little different, and the file extension will be a .txt or .xml instead of .json, but try this:

Move the file "C:\Program Files (x 86) \National Instruments\LabVIEW 2014\vi.lib\rvi\CDR\niFpgaActiveJobList.json" (or your equivalent) out of the above directory (back it upward and delete essentially) and restart LabVIEW. Must regenerate the file and resolve the problem.

-

Download NI LabVIEW FPGA Module Xilinx Tools 10.1 2013 problems

I'm trying to download the Xilinx tools 10.1 to use with a chassis 9113 in LV2011. Based on this white paper, that the compiler below should work perfectly. The problem is that I can't seem to download all the way.

I can't seem to cross ~ 336MB using the standard or the downloader OR. Any ideas? Does anyone else have this problem?

http://www.NI.com/download/LabVIEW-FPGA-Module-2013/4249/en/

Thank you

-PBD

Well well... on the good side of things, you don't want 10.1 anyway!

Virtex-5 LX50 FPGA<- requires xilinx="">

10.1 is only for devices FPGA Virtex-II! (.. .after LabVIEW 2009 it was, just for all of you who read this know).

so... try this link: http://www.ni.com/download/labview-fpga-module-2013/4248/en/

-

LabVIEW FPGA: An internal software error in the LabVIEW FPGA Module has Unknown

Sir/Madam,

Note Labview 2012 SP1 installed about 2 weeks ago.,.

Accident occurred during the compilation of an fpga vi who worked satisfactorally in the past.

When I restarted and went to the message recomplile "LabVIEW FPGA: an internal software error in the LabVIEW FPGA Module" see attached picture of popup.

I reinstalled Labview in its entirety and backed out the changes I made to the vi but still get the same message.

Thanks in advance

Daryl

It turns out that the question was in the VI and not of LabView FPGA module as the message may indicate. I created a vacuum vi, cut and pasted items in this from the vi error and recompiled and it ran very well.

Somehow the vi has been corrupted internally.

Thank you it's fixed.

-

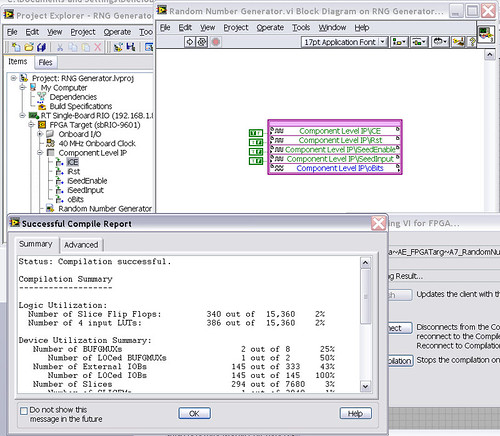

LabVIEW FPGA CLIP node compilation error

Hello NO,.

I work on an application for my Single-Board RIO (sbRIO-9601) and faced with a compile error when I try to compile my FPGA personality via the ELEMENT node. I have two .vhd files that I declare in my .xml file and all at this point works great. I add the IP-level component to my project and then drag it to the VI I created under my FPGA.

Within the FPGA personality, I essentially have to add some constants on the indicators and entries CLIP to my CLIP out and attempt to save/compile. With this simple configuration, I met a compilation error (ERROR: MapLib:820 - symbol LUT4... see report filling for details on which signals were cut). If I go back to my VI and delete indicators on the output (making the output pin of the CLIP connected to nothing), compiles fine.

I've included screenshots, VHDL and LV project files. What could be causing an indicator of the output of my VI to force compilation errors?

Otherwise that it is attached to the output ELEMENT, a successful compilation...

After that the output indicator comes with CLIP, compilation to fail...

NEITHER sbRIO-9601

LabVIEW 8.6.0

LabVIEW FPGA

Windows XP (32-bit, English)

No conflicting background process (not Google desktop, etc.).Usually a "trimming" error gives to think that there are a few missing IP. Often, a CLIP source file is missing or the path specified in the XML file is incorrect.

In your case I believe that there is an error in the XML declaration:

1.0

RandomNumberGenerator

urng_n11213_w36dp_t4_p89.vhd

fifo2.vhd

This indicates LV FPGA to expect a higher level entity called "RandomNumberGenerator" defined in one of two VHDL files. However, I couldn't see this entity in one of two files. If urng_n11213_w36dp_t4_p89 is the top-level entity, edit the XML to instead set the HDLName tag as follows:

urng_n11213_w36dp_t4_p89 Also - in your XML, you set the 'oBits' music VIDEO for output as a U32, however the VHDL port is defined as a vector of bits 89:

oBits: out std_logic_vector (89-1 downto 0)

These definitions must match and the maximum size of the vector CLIP IO is 32, so you have to break your oBits in three exits U32 output. I have added the ports and changed your logic of assignment as follows:

oBits1(31 downto 0)<= srcs(31="" downto="">

oBits2(31 downto 0)<= srcs(63="" downto="">

oBits3(31 downto 0)<= "0000000"="" &="" srcs(88="" downto="">Both of these changes resulted in a successful compilation.

Note: The only compiler errors when you add the flag because otherwise your CUTTING code is optimized design. If the IP is instantiated in a design, but nothing is connected to its output, it consumes all logic? Most of the time the FPGA compiler is smart enough to get it out.

-

8.6 LabVIEW fpga module. Where to download this version

I have Labview 8.5.1 and you have upgraded to labview 8.6 where can I download 8.6 Fpga Module?

I have a license for module fpga 8.5.1

Isutiger,

All downloads evaluation directly from our Web site are always the latest version, currently of 2009. This ensures that users evaluate our software always software up-to-date.

If you have a software maintenance (shared services provider, you get free one year every time you buy a software), you can login to the resource center of services (www.ni.com/src) and download of all supported versions, modules and toolkits for LabVIEW, including 8.6 and 8.6.1 the corrective update. You also have access to videos and tutorials.

If you do not have a service contract (cannot log in to CBC), you want to communicate with your sales representative to discuss an assessment for older versions.

-

NI Service Update: updates and Service Packs: LabVIEW FPGA Module Xilinx Tools 10.1 2012

Hello

I downloaded / installed the latest 2012 LV - everythin fine so far (his grand

)

)OR-Update Service proposed the installation of a service pack - download and installation worked too.

NOR-US also suggested to update the tools for FPGA from Xilinx module, but the download does not work. It looks that the download link is broken?

Any suggestions?

Another interesting question: I live in Austria (German), but we use Windows & LV entirely in English in our society. NOR-United States however is highly localized - even the description of the object is in German. While it is OK for me, I still wonder if I could change it to English too.

(for the attachment: "Fehler beim Herunterl...) ("-"unable to download"online)

-Benjamin

-

Cannot send DIO siganl using the LabVIEW FPGA Module and MyRIO

Everything works when no FPGA is used. If the circuit and harware work.

However when targeting module FPGA MyRIO, acquiring data and processing the work and the signal to the engine's 'sent' (visible when executing Hightlight is on). But there is no tension on the DIO ports used. FPGA projects includes VHDL code.

Do you know what could cause this problem?

You must control the OID in the FPGA.

-

LabVIEW FPGA Module Xilinx tools 12.4 zip file is broken

When I download the tools from Xilinx compilation by http://joule.ni.com/nidu/cds/view/p/id/2592/lang/en, I am able to download a zip file of 2.25 G, but when I try to unzip it or open it, the file is broken. I'd appreciate any help I need emergency compilation for LV 2011 these tools.

The file has been fixed.

Thank you.

-

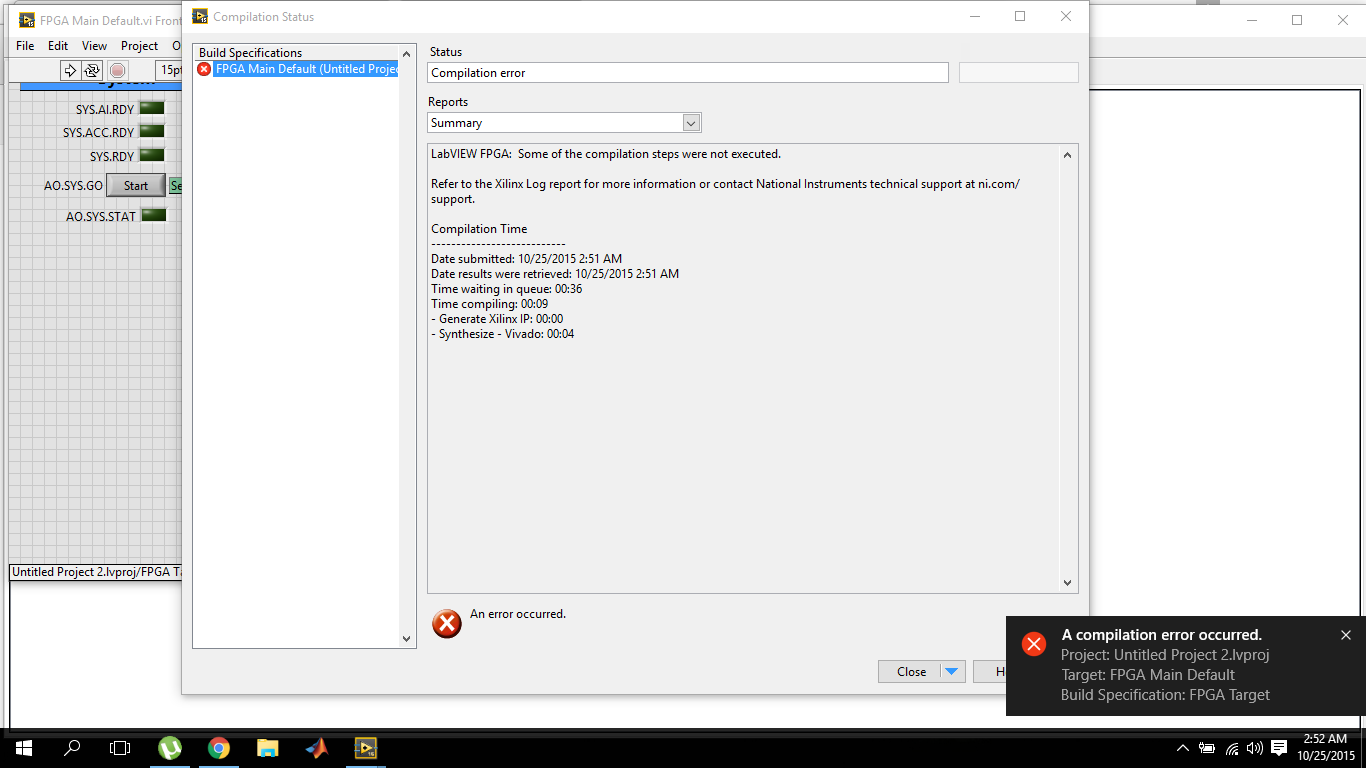

LabVIEW FPGA, 2015 compilation error

I've recently switched to LabVIEW 2015 and I'm working on OR myRIO. So also installed myRIO 2015 bundled software. The problem I have is that the compilation of fpga fails within 10 seconds.

and the target Xilinx journal report is empty

The first time when I tried to compile on 2015 version, it failed and the message box that failed came alongwith the avast antivirus warning for malicious activity. I reported it as wrong and now I tried several times with avast shield disabled control, but the results are the same. While the version of labVIEW 2014 works very well.

Now, I'm sure that there is something wrong with the installation of Vivado because this dll is part of it. The dll must be default in the2014_4\lib\win32.o directory C:\NIFPGA\programs\Vivado if you are using an operating system for 32-bit AND also in C:\NIFPGA\programs\Vivado2014_4\lib\win64.o If you use a 64-bit operating system. If the dll is not here, it is probably that the anti virus (I've never seen what happens to Xilinx but I have for other stuff).

I'm emphasizing the 2014_4 because LabVIEW 2015 uses Vivado 2014_4 while 2014 LabVIEW uses Vivado 2013_4. Since you have also installed LabVIEW 2014, you must have 2013_4 as well and if it works, you will find the dll I just wanted you make sure you check the correct directory for the Vivado 2014_4.

Download and install (reinstall or repair if already installed) 2015 LabVIEW FPGA Module Xilinx tools Vivado 2014.4. You can also use the DVD Setup if you have. It would be a good idea to do the installation with the disabled and even anti-virus try the first compilation the same. Try and let me know if the problem persists.

Kind regards

-

Model a block synchronous dual-port RAM with LabVIEW FPGA

This question caught my attention recently.

I am trying to model a particular design element called "RAMB4_S8_S8" with the LabVIEW FPGA module. This element is a block synchronous dual-port RAM allowing simultaneous access to two ports independently from each other. That being said, a port can perform read/write operation to this RAM while at the same time, the other port might be able to do the same thing. There are two opportunities of possible port conflict, however. The first is when both ports are trying to write to the same memory cell. The other scenario is when a port writes in a cell memory while at the same time the other port reads from it. Other than that, everything should be a legitimate operation.

In order to reproduce this I select memory block that is integrated into my FPGA target. An interface is configured to be the playback mode, and the other is set to write fashion. For the option of arbitration, I let the two interfaces to be "arbitrate if several applicants only. Then I got a compiler error when I tried to run my FPGA code for this model in a SCTL. The error message is something like "several objects to request access to a resource through a resource configured with option interface" arbitrate if several applicants only ", which is supported only in the single-cycle Timed loop if there is only a single applicant by interface.

This error goes away if I replace the SCTL with a simple while loop, but not what I would like to implement. So I wonder if there is a better solution to this problem, or is it just the limitation of the LabVIEW FPGA module.

Thank you.

Yes, you can use a form of conduct to perform the operations you want in the generations clock cycles, but all the code is inside a single SCTL. Basically, read the first address and storing in a register in a single cycle and then read the second address in the second clock cycle. This would allow you to two readings of valid memory every clock cycle 2. I have included a crude extract to illustrate the concept. The case selectors are identical with address A being connected to the memory in the true case, B in the case of fake address. Your biggest model memory dual port will be intact, but it will operate at 1/2 rate.

Take a look at the white paper that provides more details on the construction of memory:

Data on a target FPGAS (FPGA Module)

The ball on the memory block indicates that memory block double port cannot be applied in a configuration of reading, which is a double ROM. access read/write port must be imitated with custom code.

-

Zip file and iso LabVIEW FPGA Xilinx tools 12.4 Module is broken

I downloaded the two zip file of LabVIEW FPGA Module Xilinx tools 12.4 and iso image file three times to make sure that both files are broken and can not be installed!

The size of the file is so large about 3g. It would be better to double-check before you download on the Web site.

-Very well,.

The download is complete and the standard Windows Extraction tool worked, WinRAR worked and 7Zip worked (and no, I don't know why, I installed all). I did download a wireless network that does not have direct access to our internal servers, it should therefore be a test valid. If the link I provided above was not that you used (probably isn't, because it is not an ISO option), could you please provide me with a link to the page that you used so that I can test and repair? In the meantime, the link above should work for you.

-

Hey saying,.

It looks like your application will need to have 3 main components: A VI host on your computer, a RT VI on the cRIO and an FPGA VI. To start, you may consider looking through the following documentation:

LabVIEW FPGA Module training

http://www.NI.com/white-paper/3555/en

Getting started with the FPGA Module

http://zone.NI.com/reference/en-XX/help/371599G-01/lvfpgahelp/fpga_getting_started/

If you are already familiar with the basics, then you can consider starting for example from the Finder of LabVIEW example. In LabVIEW, select help > find examples. Then select material input and output > CompactRIO > FPGA Fundamentals. From here you can look through examples more specific to your application. I hope this helps!

-Ryan S.

-

Drivers Xilinx/Multisim and Labview FPGA

Where can I find drivers for my FPGA OR if I use Multisim/Xilinx and NOT of Labview? All the links I found are Labview be installed. However, the explicit manual FPGA indicates that you can use Multisim/XIlinx ISE in place.

OK, I tested just outside. The Driver of LabVIEW 2013 DEFB contains 2 separate components, the driver and Module FPGA support. If you run this installer, it won't check if you have LabVIEW FPGA installed unless you check the box for LabVIEW FPGA support.

I can change the text in the Installation Instructions to read "LabVIEW FPGA 2013 is required to install the LabVIEW FPGA Module Support component installation".

-

LabVIEW FPGA failure with compiler Xlinx?

I'm in LabVIEW FPGA 8.6 with NOR-RIO 3.0.1 (to 8.6). When I compile a simple program, I get the notorious:

«Error starting compile step: make sure that a compatible version of Xilinx tools is installed in the location specified in the setup of LabVIEW FPGA.»

I checked the FPGA compile server and I ran the utility fixTlink.VI with no improvement. This produces two identical PC, neither one having a FPGA installed card.

Any ideas?

After further analysis, the problem was to be in our facility in LabVIEW FPGA 8.6. Using the correct Installer of NEITHER solved the problem.

This thread is now resolved.

Maybe you are looking for

-

How I fix Bitmoji after that 10 updated iOS

Just deactivation and reactivation of the Bitmoji keyboard in settings did not work for me. Here's what I did: To get the application Bitmoji to start working again in the Messages, I took the following steps: Settings > general > keyboard > keyboard

-

Where can I find opening 3.0 so I can upgrade. Not installed on my computer.

-

Express Media Player for Satellite M40?

Hello worldwhere can I find this software to operate the keys specified on my laptop? I reinstalled the laptop with XP - Pro, but I have not found this software.Please help meThank youKarotte

-

I have a HP Officejet Pro L7580 and I moved it to a new fax line. When I went to start it now it tells me 'Failure of Fax', I have tested the line and a dose of different fax job. What can I do to get it working again?

-

Problem with Windows Vista Start Menu icons

The Start Menu doesn't display the 9 item in the list, why? [img] http://i47.tinypic.com/e053f9.jpg [/ img]